本次整理2023年6月5日~6月11日,FPGA算法技术交流群的相关问答。相关问题的解答和交流来自群成员,仅作参考。

1.有用过xilinx FIFO的first word fall through模式,然后write data count会少2个计数的吗?

答:wr count应该是代表目前fifo中写入值,读出fifo的值是不算在他的计数内,不是累加的。

2.GTH自回环,直接把差分收发assign就行吧?

答:是控制loopback。直接assign,表面上是连起来了,实际硬件管脚并没有连起来。ip核里边有个loopback,配置一下看自收发数据正不正常。Ibert可用来测高速收发器的功能。

3.有没有遇到flash启动不了的情况,上电有百分之10的几率不运行固化的程序?

答:看看SPI速率是不是比较高?如果flash是3.3v的,3.3得快点上,用k7的时候遇到过,可以试一下。

4. FPGA是不是不支持PCIE4.0X16的啊,IP核最大只找到了PCIE4.0X8的?

答:PCIE4.0X16得用高级一点的片子,versal已量产的可以支持gen4x16,gen5x8。同时Vivado版本也要用新的。

5.写verilog代码,有那些好用的编辑器?

答:notepad++、gvim、sublime、vim、vscode(有不少插件)、utral edit、TerosHDL、Digital IDE等,用起来习惯就好。

6.请问下vivado生成ram的ip时只能生成vhdl代码吗,可以选生成verilog吗?

答:取决于这个IP 最初是用什么语言写的,确实有部分IP底层用的VHDL写的。不过一般在例化接口,提供了VHDL和verilog两种模式,可以选择。

7.想问问大家,一般比如说ZYNQ中,PS/PL之间交互,一般是xilinx的ip,还是自己写axi_dma读写的ip啊?

答:自己手动写。此外,BD侧可以调用DMA。

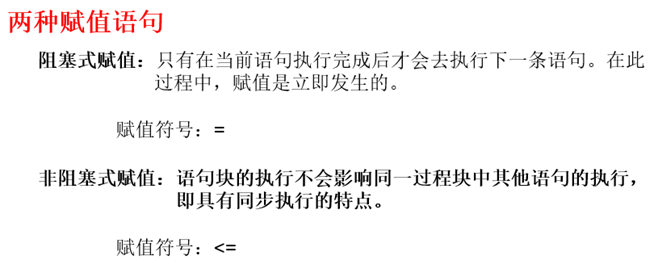

8. 阻塞与非阻塞赋值问题。

always@(*)、assign用于组合逻辑,阻塞赋值。

always@(posedge clk)用于时序逻辑,非阻塞赋值。

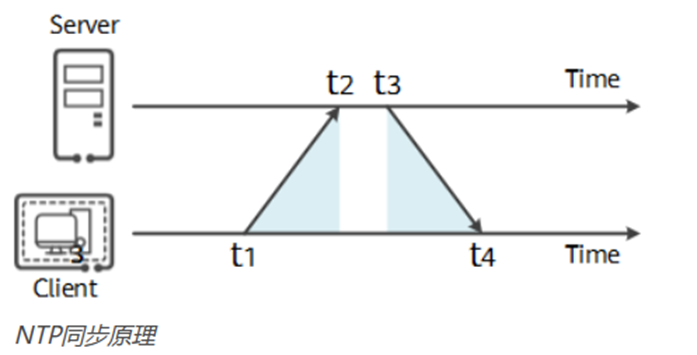

9.NTP 协议用于时钟同步FPGA怎么实现?

答:看协议规范,找资料。以下是NTP的同步原理。

NTP最典型的授时方式是Client/Server方式,如下图所示。

客户端首先向服务端发送一个NTP请求报文,其中包含了该报文离开客户端的时间戳t1;

NTP请求报文到达NTP服务器,此时NTP服务器的时刻为t2。当服务端接收到该报文时,NTP服务器处理之后,于t3时刻发出NTP应答报文。该应答报文中携带报文离开NTP客户端时的时间戳t1、到达NTP服务器时的时间戳t2、离开NTP服务器时的时间戳t3;

客户端在接收到响应报文时,记录报文返回的时间戳t4。

客户端用上述4个时间戳参数就能够计算出2个关键参数:

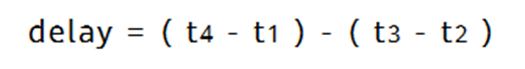

NTP报文从客户端到服务器的往返延迟delay。

客户端与服务端之间的时间差offset。

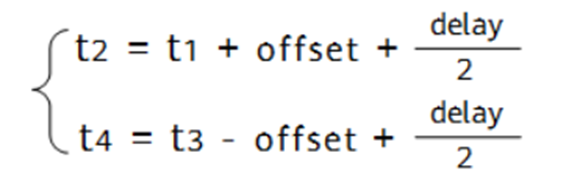

根据方程组:

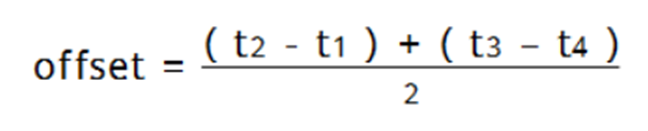

可以解得时间差为:

NTP客户端根据计算得到的offset来调整自己的时钟,实现与NTP服务器的时钟同步。

与NTP类似的还有PTP,NTP客户端根据计算得到的offset来调整自己的时钟,实现与NTP服务器的时钟同步。可以通过IEEE 1588进行时钟同步。

10. 就是千兆网的crc计算中,为啥用网站生成了crc公式得到的值,还要按字节为单位按位取反呀?

答:查一下IEEE Ethernet中的计算说明。

11. 请问一下大家这个zynq ps 40M进来 到PL 40M 在pl里边经过锁相环生成100MHz时钟,非常准确吗?

答:PS的里面的这个时钟精度不高,大都给AXI总线时钟用,很少用来当FPGA的工作时钟,也就不怎么关注详细的精度了。

12. 能不能用PLL IP的lock信号当作复位信号用呢?我看这个lock是晚于几个时钟周期后出来的。假如板子上没有设计硬件复位引脚,可以拿这个信号当全局复位用吗?

答:可以,现实当中就这这么用的。可以,但是一般我都让它控制一个计数器,因为有些东西对复位信号长度有要求,不小于XX周期。

13. 用zynq做nvme的接口,读写SSD有啥好方案嘛?

答:直接挂载到linux上用文件系统读写,我之前用的SATA接口读写SSD 使能cache能到200~300Mbytes/s。

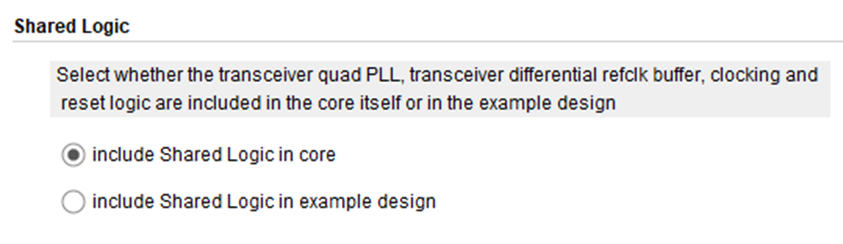

14.某些IP核生成时关于共享逻辑的问题。

答:如果选上边的,核里多包含一些必要的东西,使用起来简单些。但是那些东西也就没法复用了。下边的,是核里只包含必要的东西,其它附属东西放在例子里。

有时候需要例化多个该IP时,选用下面的在例子中使用共享逻辑,可以复用部分时钟和复位,特别是GT相关的。

15. SSS检测,找相关峰的时候可以这样(a^2+b^2-->|a|+|b|)简化算法吗?336个相关器,如果并行处理,会消耗大量的乘法器。

答:SSS检测,需要336个相关器,考虑虚警概率,如果处理方法不当,可能在拉距时容易漏检。SSS周期长,允许时间内,可不全并行处理,复用部分相关器。找最大值,可以直接用功率了吧,不用开方了,效果差不多。求功率也就2个乘法器,1个加法器。

另外,平方根的简化算法:z=sqrt(a^2+b^2)有个近似算法:

M=max(abs(a),abs(b))

m=min(abs(a),abs(b))

if (M>2*m) z=M+m/4

else z=7/8*M+m/2

16. 请教一下,VHDL怎么和c联合仿真呢?

答:通过DPI接口可以把c和sv交互。或者考虑以下QEMU。一般来说,ARM侧不用仿真。

17. 对于zynq的使用,单独从vivado加载程序,可以吗?如果我pl钟来自ps得话,需要加载sdk加载吗?

答:这只是下载程序的问题,下载PS的程序只能从SDK ,你PL的时钟需要加载PS的程序才能激活。

18.实信号与复数信号采样问题。

答:一路实信号,fs得两倍。正交的IQ有效带宽其实是加倍了。实信号正负频率共轭对称的,带宽定义的是零频到正半边,采样率大于二倍这个就行。复信号相当于两个实信号,两路AD都大于实信号二倍就行。采样速率,所以是两个实信号相加。

19. 请教一下,大家都是怎么在设计初期估计硬件板子的功耗,以及电源需求的哈。

答:Xilinx有一个excel表格可以估,XPE。XPE的使用方法参考《Xilinx Power Estimator User Guide (UG440)》。极限条件的XPE仿真步骤参考《xapp1348-power-analysis》。

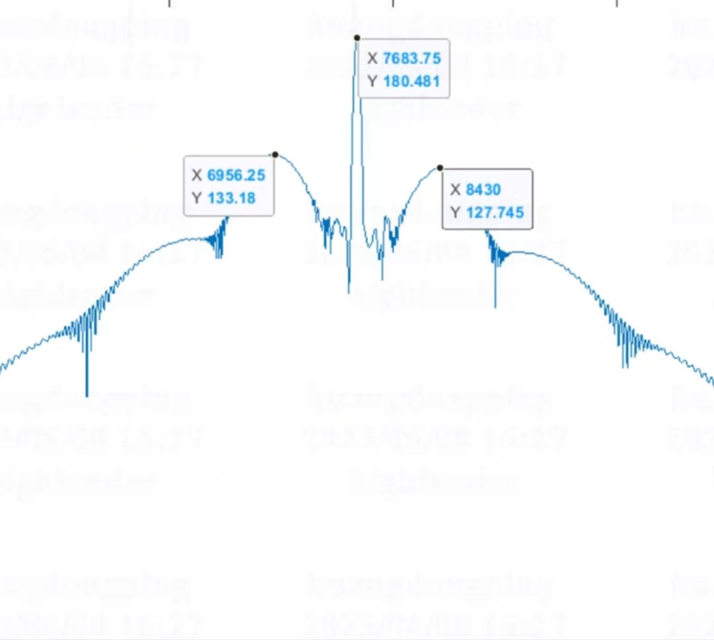

20. 请教一个问题,数字中频闭环采线性调频信号做脉压,匹配滤波器用理想的系数,脉压的结果看着很差,这个问题接下来还可以怎么排查呢?

答:线性调频信号,可以简单看看频率是不是线性变化。线性调频直接用相位差分,看看调频曲线。相位取差分,就是调频曲线,看是不是线性。

21. 有没有类似github的但是以verilog为主的开源网站?

答:例如

a、opencores,https://opencores.org/

b、FPGAs4fun,http://www.fpga4fun.com/

c、OpenHW Group ,https://www.openhwgroup.org/

d、FPGACPU,http://www.fpgacpu.org/links.html

审核编辑:汤梓红

-

FPGA

+关注

关注

1625文章

21663浏览量

601672 -

Xilinx

+关注

关注

71文章

2163浏览量

120975 -

fifo

+关注

关注

3文章

387浏览量

43533 -

编辑器

+关注

关注

1文章

800浏览量

31108

原文标题:FPGA算法技术交流问答集锦(6.5~6.11)

文章出处:【微信号:FPGA算法工程师,微信公众号:FPGA算法工程师】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

PCB Layout and SI设计问答集锦

FPGA相关技术交流

购买iphone问答集汇

特瑞仕 | 线性稳压IC网络研讨会问答集锦,请查收~

FPGA算法技术交流问答集锦

FPGA算法技术交流问答集锦

评论