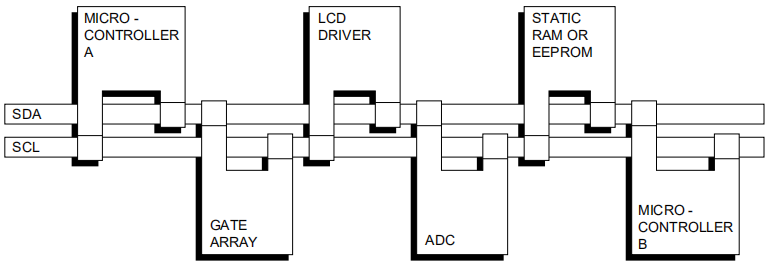

80年代初期,Philips Semiconductor为减少电子产品内部并行数据总线的数量,开发了Inter IC (I²C)总线。1992年,Philips®发布I²C总线的1.0版本,该版本定义了一个2线、双向总线,用于IC之间的互联。到1998年为止,I²C总线已经成为低速IC互联的标准,50家以上的公司使用了该标准,I²C接口被集成在1000多种不同的IC内。

实验表明,本文提供的I²C总线配置很容易实现总线上从器件的访问。

背景及讨论

I²C总线能够工作在标准模式、快速模式或高速模式(Hs)。最大速率分别为100kbps (标准模式)、400kbps (快速模式)、1.7Mbps (Hs模式,Cb = 400pF)和3.4Mbps (Hs模式,Cb = 100pF)。

原标准模式采用7位地址,允许112个从地址。随着对从设备数量需求的增加,I²C总线引入了10位地址长度。

快速模式下,从设备增加了很多有用功能。最大数据速率提高四倍,增加到400kbps。快速模式下I²C总线还向下兼容,支持速率其它类似的常常连接到I²C总线的总线,例如,一些无法支持高速率的总线。为抑制噪声,快速模式器件的输入采用了施密特触发器结构;另外还要求I²C从器件在电源掉电时,其SCL和SDA为高阻态。

构建Hs模式的主要目的是提高数据通信速率—数据速率是标准模式的36倍。I²C总线工作在Hs模式时,最主要的影响是SCL线上从低电平到高电平的瞬变;因为标准模式和快速模式下,总线的上拉电阻不能产生较快的上升时间,以支持Hs模式的规格要求。绝大多数Hs模式系统必须在SCL线上提供有源上拉。其它改变包括:Hs模式的兼容性要求,Hs模式主机在标准、快速模式下使用的是8位代码。如果非应答(I²C帧结构的其中1位)在主机代码之后立即保持在高电平,那么在停止位出现之前所有通信都将保持在Hs模式。图1波形演示了如何使用主机代码进入Hs模式。

图1. 从快速、标准I²C模式进入Hs模式的波形

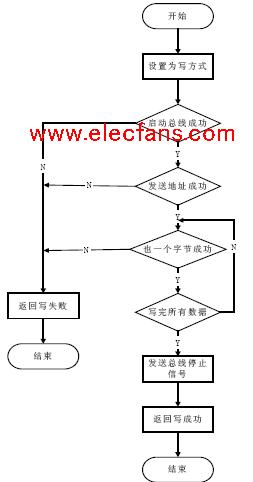

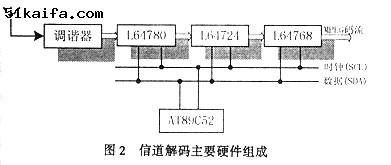

内置I²C接口实例

PIC18F442微控制器(µC)包含I²C外设接口,此接口支持标准和快速I²C模式。图2给出一个应用电路,通过此接口接收来自ADC (MAX1169)的采样数据。PIC®收到数据后会以115k波特率的速率通过UART发送出去,数据经过RS-232收发器(MAX3232E)后由计算机标准串口采集。文件I2C_on_chip_asm.zip"包括了所有实现快速模式下PIC片上I²C接口通信的汇编程序。可以使用MPLAB IDE 6.10.00版本开发图2电路的汇编程序。

图2. PIC18F442 µC内置I²C接口与16位ADC (MAX1169)的连接

逐位仿真实现I²C通信

MAXQ2000是低功耗16位RISC µC,能够以逐位仿真方式实现标准模式、快速模式甚至1.7MHz Hs模式的I²C通信。图3给出了MAXQ2000的通用原理图,可以作为I²C主机支持三种工作模式。为了支持1.7MHz Hs模式,原理图中I²C总线采用有源上拉。I2C_bit_bang_asm.zip"文件包含了使用µC GPIO口仿真标准、快速模式I²C通信所需的所有汇编程序。

图3. 该原理图(基于MAXQ2000低功耗LCD µC)提供了一个能够工作在标准、快速或Hs模式的I²C主机

MAXQ2000的I²C 固件的默认时钟速率为100kHz,但µC的16MHz系统时钟能够支持逐位仿真的I²C接口工作在400kHz。以下例程演示了捕获中断事件并在简单中断服务程序中处理中断的过程。开发工具使用MAX-IDE 1.0版(开发日期:2004年11月18日),该软件可从Maxim网站免费下载。

I2C_bit_bang_c.zip"文件中包含了使用MAXQ2000 GPIO口逐位仿真标准、快速模式I²C通信所需的C程序源文件。图3对应的例程基于maxqi2c库文件,包括maxqi2c.h和maxqi2c.c.两个文件。将文件加载到用户工程后,可以在任何GPIO口支持100kHz或400kHz的I²C通信。但是,使用C程序产生特定速率的I²C通信时,图3中的Y1必须用20MHz晶体代替15MHz的晶体。本例使用了为MAXQ2000 1.12B版(FAE版)开发的IAR Embedded Workbench® IDE工具,用户可以在IAR网站注册后免费下载用于MAXQ2000的IAR Embedded Workbench (4K,初级版)。

HSI2C_bit_bang_asm_c.zip"文件包含了使用MAXQ2000 GPIO逐位仿真1.7MHz Hs模式I²C通信所需的汇编程序和C程序。源代码采用汇编语言和C语言混合代码,以便充分发挥这两种编程语言的优势。汇编程序有助于优化速度,C程序能够使源代码更简捷(只需少数几行指令)。Hs模式对时序要求非常苛刻,I²C接收函数(hsi2cRecv)采用了汇编程序,代码在hsi2c.asm文件内。

主程序C代码对MAXQ2000的UART进行初始化,波特率为115.2kbps。为了实现1.7MHz Hs模式I²C通信,图3中的Y1必须采用20MHz晶体。主程序C代码在需要时调用hsi2cRecv函数,并使用printf函数通过片上UART发送数据,数据格式为8-N-1。这里使用Rowley CrossWorks IDE 1.0版(Build 2 Licensed copy)开发工具。要想获得CrossWorks IDE工具,请联系Rowley Associates Limited或访问其网站。

I²C IP核外设接口的实现

DI2CM I²C IP核(由Digital Core Design开发)广泛用于许多CPLD和FPGA器件。DI2CM I²C IP核将并行接口转换为I²C接口,并可支持主机真正工作在3.4MHz的Hs模式。图4应用电路中,Altera® EPM3256AQC208-10 CPLD包含DI2CM IP核。此电路需要使用40MHz晶体(U3)以支持1.7MHz和3.4MHz的Hs模式。带有输出使能的3态逻辑缓冲器使DI2CM IP核可以在SCL线上产生有源上拉,以满足Hs模式下I²C通信的要求。逻辑反相门电路U5、U6和U7用于实现高电平有效和低电平有效的内存映射的并行接口。

图4. 按照电路所示配置,Altera EPM3256AQC208-10 CPLD中的DI2CM IP核能够实现Hs模式的I²C主机

HSI2C_IP_core_asm.zip"文件包含了所用用于实现Hs模式I²C通信所需的汇编程序,通过连接68HC16的存储器映射并行接口和使用DI2CM IP核编程的Altera EPM3256 CPLD实现。本例采用了Motorola® 68HC宏汇编程序,4.1版。

结论

由于I²C总线是目前业内使用最为广泛的串行总线,系统设计人员能够得到丰富的经过验证的例程。实施方案有—芯片内置、逐位仿真或IP核,具体取决于所使用的系统处理器。使用经过验证的设计示例进行开发时最简捷的途径,本文给出了三种工作模式下I²C接口的设计参考。

审核编辑:郭婷

-

芯片

+关注

关注

455文章

50771浏览量

423412 -

ADC

+关注

关注

0文章

110浏览量

16845 -

I²C总线

+关注

关注

0文章

14浏览量

2127

发布评论请先 登录

相关推荐

GPIO模拟I2C总线的驱动设计与实现

用Verilog HDL实现I2C总线功能

用Verilog HDL实现I2C总线功能

基于CPLD的I2C总线接口设计

基于SystemVerilog的I2C总线模块验证

I²C总线的验证及实现

I²C总线的验证及实现

评论