二.Latch-up测试流程。

目前通用的Latch-up测试标准是 JESD78E 。该标准中将Latch-up测试分为两种: 1.电流测试 I-test ,用于测试非电源管脚;2.电压测试 V-test 用于测试电源管脚。其中I-test又有正向注入/负向抽取两种,正向注入电流会使得端口电压升高,负向抽取电流会使得端口电压降低。

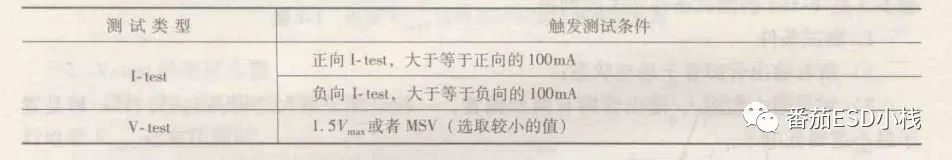

表一.测试闩锁效应的分类。(图源《CMOS集成电路闩锁效应》)

表一为Latch-up的测试条件,其中MSV表示(Maximum Stress Voltage)最大允许工作电压。

2.1 V-test的测试流程

- 对所有的输出引脚悬空,输入引脚置于高电平偏置,测量VDD到GND的漏电流In。

- 对待测管脚施加V-test源。

- 去除触发源后将被测管脚复原,测量漏电流Isupply,进行失效判断。(如果In<25mA,失效标准为In+25mA,如果In>25mA,失效标准为>1.4*In)

- 如果没有发生Latch-up,将所有输入管脚,都置于低电平偏置,重复实验。

- 重复2,3,直到每个电源Vsupply管脚(或管脚组合)都通过测试。

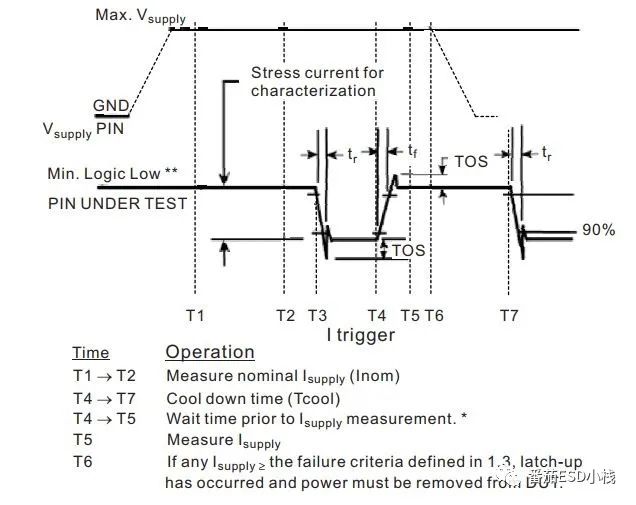

图一.V-test激励波形。

V-test测试模拟的是电源浪涌是否会造成PN结击穿,形成雪崩击穿电流,从而造成寄生SCR的开启。

2.2 I-test的测试流程

- 不接受测试的输出管脚悬空。对于输入管脚,偏置于最大逻辑高电平。电源管脚置于最大工作电压。

- 测量VDD到GND的漏电流In。

- 对待测管脚施加I-test源。

- 去除触发源后,将被测管脚恢复到施加触发源之前的状态,并测量每个电源管脚的漏电流Isupply,进行失效判断。(如果In<25mA,失效标准为In+25mA,如果In>25mA,失效标准为>1.4*In)

- 如果没有发生Latch-up,对所有待测管脚,重复实验。

- 将非待测管脚置于悬空态。将输入管脚置于最小逻辑低电平。电源管脚置于最大工作电压。重复上述实验。

图二.I-test正向激励波形。

图三.I-test负向激励波形。

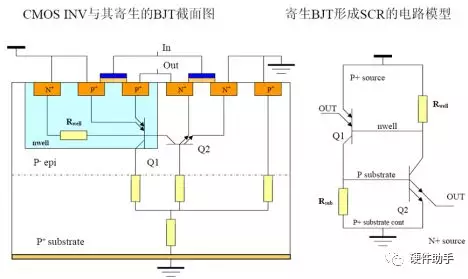

I-test测试模拟浪涌电压出现在非电源管脚,浪涌电压高于VDD或低于GND。该电路中寄生SCR能否开启。

2.3 无源器件相连的特殊管脚

这类管脚都只进行I-test,具体情况请参照《CMOS集成电路闩锁效应》。

2.4 特殊功能管脚

某些芯片会具有特殊的功能管脚,例如LDO,PWM,BOOT,PHASE,HB,VCC等,这些芯片的管脚能为其他芯片或器件提供偏置。而针对这类管脚,使用I-test还是V-test需要根据情况确定。

2.5 多电压域芯片

BCD工艺或者BiCMOS工艺能实现高压-低压多工作电压芯片,而这种芯片因为工作电压不同,V-test激励值不能统一按1.5*Vmax算。

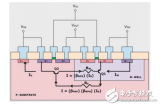

图四.多电压域Latch-up测试。(实例取自德仪Latch-up白皮书)

如图所示,该芯片存在5V,12V,60V多个VDD。针对该芯片的V-test需要不同的激励, VDD 5V需要1.5Vmax或MSV;VDD 12V需要1.2Vmax或MSV;VDD 60V需要1.1Vmax或MSV 。

三.Latch-up防护设计。

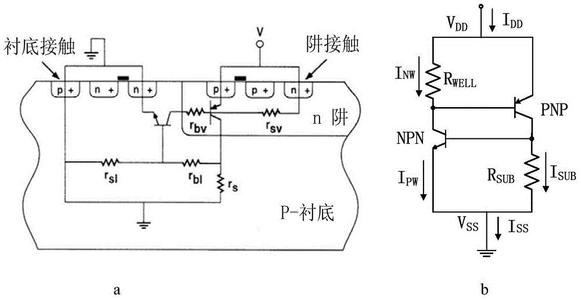

Latch-up防护的核心就是预防电路中寄生SCR的开启。而围绕这一目标具体有两个实现方向:

一.减少阱电阻Rn和Rp,降低寄生三极管的基级电压。

具体的版图设计规则:

1.减少Bulk与Soure/Drain端的间距,减少N-WeLL/P-WeLL的阱电阻。

增大阱接触区的面积和接触孔数量,因为阱接触区是高掺杂浓度的有源区,能大幅度改善阱电流分布,降低阱电阻。

2.使用环状阱接触有源区。环状设计能确保有源区与接触孔分布均匀,避免电流集中流向某一区域造成的局部电压过高。

二.减少βn和βp,降低寄生三极管的放大倍数,削弱寄生三极管的正反馈耦合作用。

具体的版图设计规则:

1.增大NMOS/PMOS有源区与N-WeLL/P-WeLL的距离。通过增加间距,拉宽寄生三极管的基区宽度,减小其放大倍数。

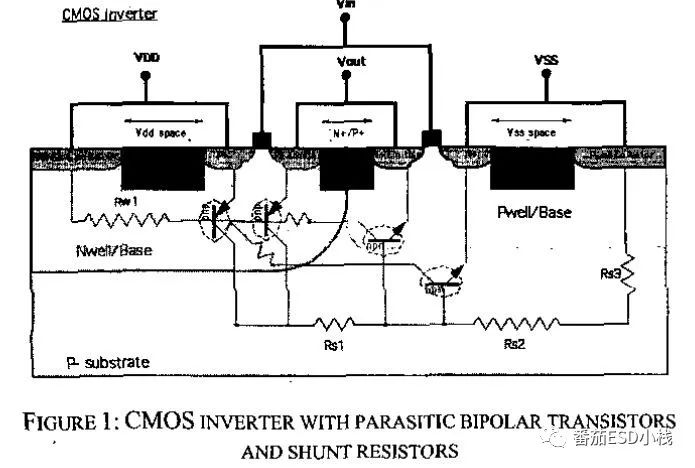

2.增加额外保护环。保护环能为寄生三极管增加额外的集电极/射电极,而新添加的寄生三极管,(NPN:NMOS_Drain/P_Sub/N_Guard)与(PNP:PMOS_Drain/N_WeLL/P_Guard)更易触发,且不存在相互耦合作用。换句话说起到了对外部注入载流子的收集作用。

图五.CMOS保护环示意图。

3.IO电路与核心电路的隔离,IO电路所承受的风险远高于内部电路。所以IO单元最好与内部电路间隔一段距离,确保ESD/Latch-up/EOS等不会引起内部核心电路的损坏。

其实Latch-up的防护相对于ESD来说较为简单, 只要版图工程师注意间距与保护环的问题,绝大多数Latch-up失效都能避免(目前大部分工艺都已经把latch-up rule 写入 DRC中,只要按图索骥即可) 。但是模拟IC要面临的Latch-up的情况更加复杂,所以这里介绍些 非常规设计方案 。

1.利用工艺优势,Epi(外延层工艺);DTI(深槽隔离);SOI(绝缘体上硅);NBL埋层,这些工艺都能有效改善Latch-up问题。

2.利用Deep N-WeLL 进行隔离,深N阱的隔离作用更加有效,也能有效缓解Latch-up。

3.浮阱设计(一种特殊设计,会造成阈值电压和漏电流浮动,主要应用在ESD与Latch-up,以后会讲案例)

4.输出级在端口挂载电阻,I-test时能分担部分压降,但是会降低输出级的负载能力。

-

三极管

+关注

关注

143文章

3637浏览量

123302 -

SCR

+关注

关注

2文章

151浏览量

44568 -

VDD

+关注

关注

1文章

315浏览量

34424 -

电源浪涌

+关注

关注

0文章

12浏览量

5927 -

PMOS管

+关注

关注

0文章

84浏览量

6886

发布评论请先 登录

相关推荐

CMOS的闩锁效应:Latch up的原理分析

Latch UP

寄生电路的效应:Latch-Up(锁定)

静电放电/过度电性应力/闩锁试验 (ESD/EOS/Latch-up)

LIS3DH加速度计自我测试失败

ESD/Latch-Up Considerations wi

Latch-Up White Paper

Latch-Up白皮书

c2m0160120d碳化硅功率MOSFET技术

高压闭锁双SPST开关的adg5421/adg5423数据表

浅谈Latch-up(二)

浅谈Latch-up(二)

评论