来自RISC-V欧洲峰会的新创新准备简化开源处理器的设计过程。

随着RISC-V欧洲峰会的结束,我们将回顾本周的公司如何利用这次活动作为平台,展示他们利用开放指令集架构(ISA)的最新创新。这些发展既包括硬件也包括软件,这使得它们对许多领域的设计师都很重要。

自2015年发布以来,RISC-V一直是一个开放的标准,支持自定义硬件和软件创新。ISA使用预先存在的知识来加快开发时间,并在设计过程中提供改进的灵活性。

RISC-V欧洲峰会的三个亮点可能为不需要在架构的最低级别操作的设计人员提供新的抽象级别。本文将介绍峰会上的这些公告,并讨论每个创新如何为设计师提供工具,使开发周期更简单,同时缩短上市时间。此外,我们将研究不断发展的RISC-V生态系统,以评估ISA将如何继续发展。

自定义矢量核

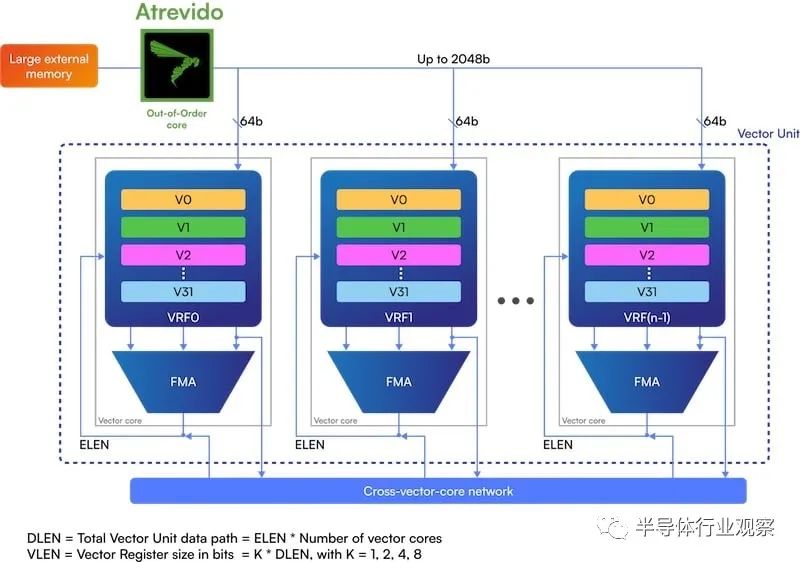

为了迎接RISC-V欧洲峰会,semidynamics宣布了“最大的、完全可定制的”矢量处理RISC-V处理器。随着矢量计算在人工智能或计算机视觉应用中变得越来越重要,硬件矢量支持可以成为许多开发人员在高性能系统上工作的宝贵设计工具。随着RISC-V国际公司2021年的矢量扩展,预计ISA的矢量处理将随着需求而增长。

来自semidynamics的矢量单元是可定制的,以适应应用程序的需求,允许设计人员根据需要缩放数据路径长度,矢量长度或数字格式。并且在单个单元中集成了从4到32个矢量内核,即使是计算最密集的应用程序也可以使用vector unit。矢量单元与atrevideo和Avispado RISC-V内核一起提供,并展示了RISC-V ISA的多功能性。

RISC-V矢量加密

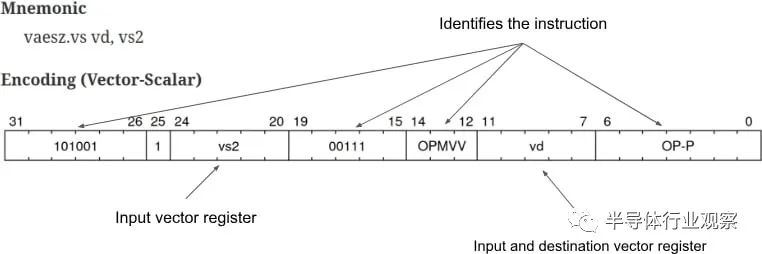

随着矢量硬件可用性的提高,Codethink已经将对RISC-V矢量加密扩展集的全面支持集成到仿真软件QEMU中。虽然仿真可能不是实现矢量加密设计的直接要求,但它是RISC-V规范中批准的要求。

基于他们过去在RISC-V设备上的经验,Codethink在QEMU模拟器上的开发最终将使矢量加密技术更接近RISC-V标准化。目前,扩展集处于稳定阶段,预计会发生有限的更改,之后扩展集可以冻结和/或批准。

软件定义的硅

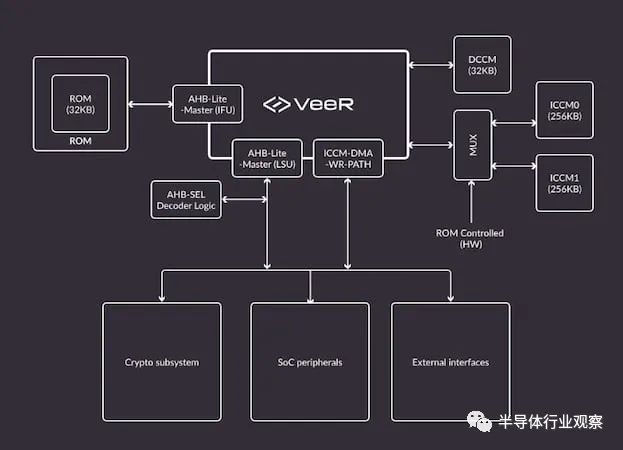

一组芯片联盟成员,包括安特微和谷歌,提出了改进的数字设计工具,用于集成使用RISC-V内核。这些工具,即Verible和Kythe,可以与非常高效和优雅的RISC-V (VeeR)核心家族一起使用,以简化设计过程,并允许在组织内部和组织间的工作中进行开放协作。

Caliptra项目突出了这些努力,该项目利用VeeR核心家族提供现代处理器所需的安全性。除了设计和验证工具之外,Antmicro还提供了一个视觉系统设计器,提供了更多的理由相信RISC-V设计器很快就会体验到一个新的抽象层次。

高性能RISC-V

虽然RISC-V欧洲峰会肯定会讨论更多的发展,但本文中的发展代表了RISC-V处理器增加可访问性和市场份额的趋势。这并不是说模拟和数字芯片设计师很快就会过时,而是说设计RISC-V处理器可能很快就会成为一项更容易的任务。

随着软件和硬件的创新,如视觉系统设计,矢量核心支持,或专用的RISC-V模拟IP,高级开发和集成的新机会似乎即将到来。除了进入RISC-V生态系统的门槛较低之外,这最终支持了RISC-V不可避免的说法。

-

处理器

+关注

关注

68文章

19316浏览量

230082 -

指令集

+关注

关注

0文章

226浏览量

23387 -

RISC-V

+关注

关注

45文章

2292浏览量

46210

原文标题:RISC-V,迎来新创新

文章出处:【微信号:Rocker-IC,微信公众号:路科验证】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

拥抱RISC-V的开发世界 兆易创新推GD32VF103系列RISC-V MCU

玄铁RISC-V生态大会深圳召开,达摩院引领RISC-V创新应用

2024 RISC-V 中国峰会:华秋电子助力RISC-V生态!

RISC-V Summit China 2024 | 青稞RISC-V+接口PHY,赋能RISC-V高效落地

RISC-V,即将进入应用的爆发期

为什么选择RISC-V?

【RISC-V专题】芯昇科技RISC-V生态开发板首发试用

RISC-V简介

RISC-V芯粒,终于来了

RISC-V竞赛|2024年iCAN大学生创新创业大赛“算能杯”报名正式启动!

RISC-V Summit China 2024 青稞RISC-V+接口PHY,赋能RISC-V高效落地

2024年RISC-V产品和应用创新案例征集活动公告

RISC-V,迎来新创新

RISC-V,迎来新创新

评论