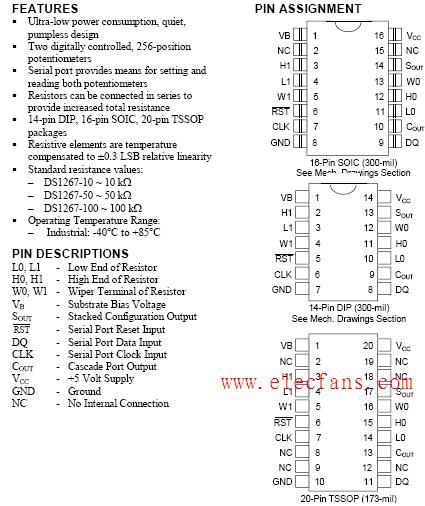

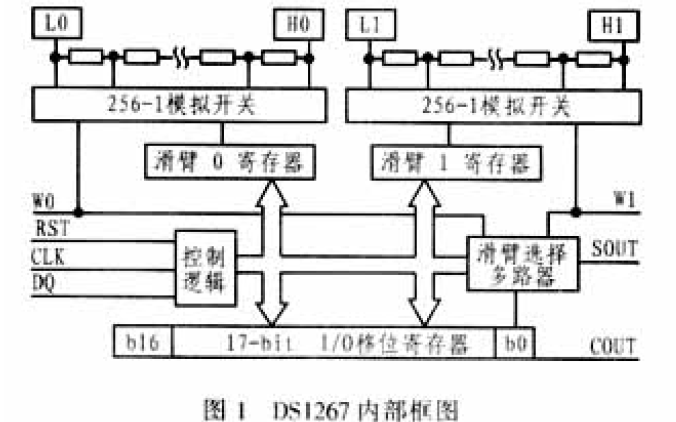

DS1267为双通道数字电位器,具有串行“移位寄存器”型接口。移位寄存器有一个输入引脚,用于移入数据,还有一个输出引脚,在写入时将数据移出移位寄存器的最后一位。这样就可以将多个DS1267以菊花链方式连接在一起,并在同一串行总线上一起编程。本应用笔记通过电路示例和伪代码示例描述了如何实现此目的,展示了如何为任何微处理器开发代码。

介绍

Dallas Semiconductor的数字电位器DS1267非常适合需要数模转换器(DAC)的系统,或需要可编程偏置电流、电压或电阻而无需传统机械电位器人工干预的系统。DS1267在一个封装中提供两个数字电位器。独特的3线协议允许将其中多个芯片串联或并联放置。可选的堆叠配置允许芯片的两个8位电位计串联放置,提供9位精度。DS1267可用于输入范围为-5V至+5V的双电源系统,只要基板偏置电压低于所使用的最低输入电压即可。

本应用笔记概述了通过公共总线与多个DS1267通信的不同配置。它还提供与两个以菊花链形式串联在一起的DS1267通信所需的硬件和软件。

与DS1267通信的硬件设置

连接3线总线以与多个芯片通信有两种主要方式。这些设备可以串联或并联连接。对于任一类型的连接,一次将向器件写入 17 位数据块。数据将确定电位计游标器的位置和每次复位取消置位时的堆栈输出。

系列

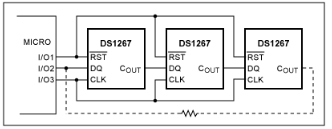

标准串联连接如下图1所示。这种连接方法适用于具有双向端口的微处理器,这些端口在预期输入时具有高阻抗。这允许使用反馈电阻从C驱动DQ引脚外菊花链中的最后一个设备。如果不希望从器件读取数据,则可以省略隔离电阻。这种方法允许无限数量的芯片串联放置。

图1.三个DS1267串联,与反馈电阻串联,用于读取移位寄存器。

注意:反馈电阻应约为10kΩ,以便在I/O引脚2和C之间提供足够的隔离外当 I/O 引脚 2 驱动 DQ 时。

第二种串行连接方法(图2)必须用于具有集电极开路I/O端口的微处理器。在集电极开路端口上,有一个内部(8051微处理器如此)或外部上拉电阻,无需高压侧驱动器即可产生高信号。这样做通常是为了消除微处理器与连接到它的某个外部设备争用的可能性。如果在C之间连接了隔离电阻外和DQ,如图1所示,那么每当C时,它都会在写入周期中导致器件错误外试图将 DQ 引脚驱动为低电平,因为 C外将超过弱上拉电阻的驱动。图2所示的设置允许使用一个额外的引脚读取DS1267中的移位寄存器,仅用于集电极开路端口上的输入。典型的3线信号像以前一样控制DS1267。

图2.DS1267与用于从移位寄存器读取的独立输入串联。

在两种串联连接情况下,DS1267的反馈都可以省略,只需要三根线即可写入任意数量的DS1267。如果以后必须知道电位器的状态,则必须使用2字节的RAM来跟踪写入总线上每个DS1267的值。串联方法的主要缺点是串行总线上的n个DS1267写入或读取的时间是单芯片的n倍。

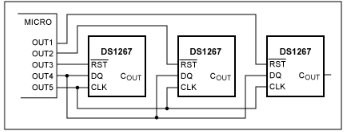

平行

第二类设置是并行配置。图3所示为并行设置,可用于写入多个DS1267,DQ和CLK在公共和独立的RST信号中。该系统的优点是只需17个DS1267时钟周期即可写入所使用的任何器件。缺点是每增加一个DS1267就需要一个额外的输出引脚。如果需要多个DS1267和高速写入,则可以通过增加解码器对地址进行解码,以产生复位(片选)信号。这将允许操作 2(# 可用选择引脚)DS1267s.因此,如果有三个I/O引脚可用于解码地址,则可以对它们进行解码,允许1267个DS16双通道电位器(<>个电位器,采用<>个封装)工作在公共DQ和CLK信号下。如果下面的系统使用解码器,则可以再增加五个电位计,而不会损失另一个输出引脚。

图3.三条并行配置的DS1267共用DQ和CLK线路。

上述设置不包含任何DS1267读数的规定。如果要在使用解码器的系统中读取电位计,则可以将解码器地址行与多路复用器一起使用,以读取所有 C外s,像以前一样进入单个双向I/O引脚或单独的输入引脚。

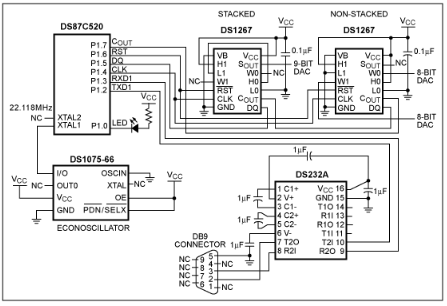

图4(下一页)所示的硬件设置用于生成附录A中的代码,为DS22C2微处理器提供87.520 MHz时钟。DS232A将5V CMOS信号转换为RS232电平,用于微处理器和PC之间的通信。DS232A连接到标准串行端口插头,该插头可以连接到PC,允许微处理器以19200波特(1个停止位,无奇偶校验,无流量控制)反馈。两个电位计以菊花链形式连接(串联),并连接到端口 1 上的微处理器。第一个DS1267以堆叠配置连接,提供9位DAC。第二个DS1267提供两个8位DAC。由于它们是串联连接的,因此每次读取和写入尝试都将涉及移动 2*17 位。LED 也已连接到端口 1.0 作为状态指示器。

注意: 8051 具有收集器开路端口;因此,C 必须使用单独的输入引脚外.使用DQ作为双向端口引脚会导致微处理器和DS1267之间的通信错误。此外,如果要使用串行端口,时钟速率必须接近 22.118 MHz。如果时钟速率低于该频率的 2-3%,可能会导致串行端口通信错误。

图4.DS87C520微处理器DS232A串行端口发送器和两个DS1267以菊花链形式连接在3线总线上。

3线协议

3线协议是一种简单的协议,通过1267位移位寄存器对DS17的两个电位器进行编程。移位寄存器由复位、数据和时钟信号控制。复位 (RST) 用于选择芯片。该信号为高电平有效,必须在尝试写入或读取器件时置位。数据引脚(DQ)用于将数据传输到器件。将数据正确放置在DQ上后,时钟信号(CLK)被脉冲以同步数据传输。这些事件的时序在DS1267数据资料中给出。移入器件的数据可以继续转移到另一个具有级联输出的3线器件(C外.)级联输出也可以路由回控制器,以允许微处理器读取它所写的内容。

串联的两个器件的数据格式如图5所示。

图5.两个17位DS1267移位寄存器级联在一起,用于串联工作。

在这种配置中,移入寄存器的第一个位一直移位到最后。因此,在数据传输开始时放置在 DQ 上的第一个位将是 STK#2。这是DS1267 #2的堆栈控制位。接下来发送的8位是控制DS8 #1上游标1267位置的2位,图中标有电位器3。请注意,字节的 MSB 首先发送到该部分。然后接下来的8位将控制电位计2。发送的下一个位将是STK#1,它控制DS1267 #1的堆栈输出。电位计 1 和 0 的字节将分别跟随堆栈控制位。如果总线上仅连接一个芯片,则只有17位数据将传送到该器件,但数据的格式与图5前半部分所示相同。

要将17位写出到DS1267之一,必须执行以下步骤:

断言 RST(高)

在DQ引脚上放置一个数据位

脉冲CLK

重复步骤 2) 和 3) 再重复 16 次

取消断言 RST(低)

如果将 n 个 DS1267 级联在一起,则在取消 RST 之前执行步骤 2) 和 3) n × 17 次。

如果可选反馈电阻与双向端口一起使用,则存储在移位寄存器中的值 通过完成以下操作进行读取:

置位 RST,并将 I/O 引脚 2 置于高阻抗状态。

读取 I/O 引脚 2(等于 C外如果 I/O 引脚 2 处于高阻抗状态)。

脉冲CLK。

重复步骤2)和3)16倍以上。

取消断言 RST。

从具有 C 的部分读取外连接到单独的输入,以下序列必须 完成:

断言 RST。

读取 C外在输入引脚处。

C 的写入值外到DQ。

脉冲CLK。

重复 2)、3) 和 4) 再重复 16 次。

取消断言 RST。

注:C 的值外必须写回 DQ,因为读取和写入尝试之间的复位和时钟信号的操作没有区别。因此,C外被写回 DQ,如图 1 中的硬件所做的那样。此外,如果串联连接n个DS1267,则序列2、3和4必须执行n×17次,否则DS1267中的数据将不与读取例程开始时相同。

使用软件生成的1267线通信控制两个DS3

主要的3线通信程序

1267-Wire协议部分所述的DS3通信方法通过四个程序在代码中完成。这些例程用于写入 34 位、读取 34 位、序列化要发送到每个电位计的数据字节,以及将从电位计接收的数据位重建为字节。前两个套路分别调用后两个套路。该代码位于附录 A 中,下面列出了这些例程的简要说明。

WritePots3

此例程是主编写例程。它写入存储在称为 stack1 和 stack2 的内存位置中的堆栈控制位,并使用 WriteBits3 例程将所有数据写入电位计。写入DS1267的数据以4个字节(PotData0、PotData1、PotData2和PotData3)存储。

WriteBits3

此例程通过将 MSB 旋转到进位,将进位写入 DQ,最后脉冲 CLK 来写入累加器中存储的字节。总共重复八次,将整个字节写入DS1267。

ReadPots3

此例程是主阅读例程。它读取堆栈控制位,并将其存储在称为 stack1 和 stack2 的内存位置。它还使用 ReadBits3 例程回读控制每个电位计的 8 位信息,并将值存储在标记为 PotData4、PotData0、PotData1 和 PotData2 的 3 字节中。

读取位3

此例程从用于存储游标位置的电位计读回 8 位,将 8 位转换为字节,并将数据传递回累加器中的调用过程。

其他例程

这些例程都通过执行下面描述的功能来支持主通信例程。

initSP1

初始化串行端口 1。

介绍

通过串行端口 1 在 PC 终端上显示欢迎消息

init3wire

初始化 3 线总线信号(RST、DQ、CLK),并设置用于写入电位计的变量中的值(堆栈 1、堆栈 2、PotData0、PotData1、PotData2、PotData3

重量

可编程等待功能。使用 wait16us,并寄存器 R5、R6 和 R7,以实现 14.42 μs 和 3.7 min 之间的延迟。

等待16us

每次调用延迟 1.6 μs。

DisplayPots:

使用 outchar 和 binasc 显示从每个电位计读回的值。DS1267的工作不需要代码,但是当您可以在尝试读取后验证存储字节中的数据是否正确时,调试读取问题变得更加容易。

outchar

将单个字符放入串行端口 1 缓冲区,然后等待设置串行传输完成标志,然后再返回。

binasc

将累加器中存储的整数转换为十六进制格式的两个 ASCII 字节。

outstr

使用 outchar 通过串行端口 1 将空终止的字符串发送到 PC。发送的字符串存储在代码末尾的消息部分中。

主程序

主程序执行以下顺序:

禁用中断

初始化串行端口 1

初始化 3 线引脚和变量

反转位于 P1.0 上的 LED,表示程序的开始

将电位计写入初始化期间存储的值

延迟 5 秒,这样做是为了万用表可用于确定读取功能(下一个)是否将电位计覆盖为不同的值

读取电位计

显示结果

开始闪烁 LED,每秒闪烁一次,表示程序已完成执行

审核编辑:郭婷

-

寄存器

+关注

关注

31文章

5308浏览量

119977 -

dac

+关注

关注

43文章

2268浏览量

190819 -

微处理器

+关注

关注

11文章

2247浏览量

82306

发布评论请先 登录

相关推荐

利用8051微处理器生成3线信号以控制多个DS1267数字电位计

DS1267 pdf datasheet (Dual Dig

数字电位器DS1267及其在电桥自动平衡中的应用

DS1267中文资料 (256结点双数字电位器)

数字电位器DS1267 及其在电桥自动平衡中的应用

DS1267 双路、±5V、数字电位器芯片

使用多个DS1267数字电位器在一个8051微处理器生成3线

使用多个数字电位器DS1267与8051微处理器产生三线信号

数字电位器DS126的结构和工作原理及DS1267在电桥自动平衡的应用说明

使用多个DS1267数字电位器和8051微处理器产生3线信号

使用多个DS1267数字电位器和8051微处理器产生3线信号

评论