DS3112具有六种不同的发送时钟和六种不同的接收时钟类型:发送DS3、DS2、DS1、E3、E2和E1时钟,以及接收DS3、DS2、DS1、E3、E2和E1时钟。由于电路中同一级的时钟具有相似的特性,因此时钟将成对描述为DS3(E3)、DS2(E2)和DS1(E1)。本应用笔记阐明了发送时钟的频率容差、发送和接收时钟速率能力以及DS1/E1发送和接收时钟接口的详细信息。

DS3112具有六种不同的发射时钟和六种不同的接收时钟类型:发送DS3、DS2、DS1、E3、E2和E1时钟,接收DS3、DS2、DS1、E3、E2和E1时钟。由于电路中同一级的时钟具有相似的特性,因此时钟将成对描述为DS3(E3)、DS2(E2)和DS1(E1)。

本应用笔记阐明了发送时钟的频率容差、发送和接收时钟速率能力以及DS1/E1发送和接收时钟接口的详细信息。

传输时钟

在发射端,DS3(E3)时钟和DS1(E1)时钟由输入引脚派生,但DS2(E2)时钟频率是DS3(E3)时钟频率的一小部分。出于设计原因,分数将表示为整数比率,这取决于设备的模式。DS1(E1)时钟可以容忍基于DS3(E3)时钟频率和器件模式的频率范围。

DS1(E1)和DS2(E2)时钟频率可以独立于DS3(E3)时钟频率而变化。此更改通过使用 DS2(E2) 和 DS3(E3) 成帧开销的功能(称为填充)来实现。帧结构中有一些保留的填充位,可用于有效负载数据或不用于有效负载数据,具体取决于开销中使填充控制代码的 C 位的值。但在“DS3 C 位奇偶校验”模式下,C 位用于额外的信号传输,填充速率设置为 100% 填充的固定值,其中填充位从不用于数据。

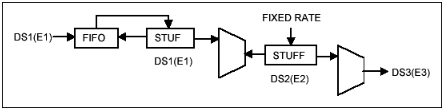

图1.传输时钟图。

DS2(E2)发送时钟基于固定的速率得出,具体取决于器件的模式。填充速率表示为填充位未用于发送有效负载数据的次数与填充机会总数的比率。比率越高,有效载荷的有效时钟频率越低。确定DS2(E2)频率的公式如下:

DS2 频率 = (672 - 填充速率) / 4760 × DS3 频率

672 是 DS2 帧中 DS3 有效负载位数。

4760是DS3帧中的总位数。

E2 频率 = (378 - 填充速率) / 1536 × E3 频率

378 是 E2 帧中 E3 有效载荷位数。

1536 是 E3 帧中的总位数。

DS3112采用固定填充速率设计,根据器件的模式产生固定频率。下表列出了使用精确DS2(E2)频率的固定速率和由此产生的DS3(E3)频率。

| 模式 | 物价 | DS2(E2) 与精确的 DS3(E3) |

| DS3 C 位 | 1/1 (100%) | DS2 = 6.306272MHz (-907ppm) |

| DS3 M13 | 7/18 (38.9%) | DS2 = 6.312016MHz (+2.53ppm) |

| G.747 C 位 | 1/1 (100%) | DS2 = 6.306272MHz (-907ppm) |

| G.747 M13 | 7/18 (38.9%) | DS2 = 6.312016MHz (+2.53ppm) |

| E3 | 1/2 (50%) | E2 = 8.446562MHz (-170ppm) |

使用固定填充的最小和最大DS2(E2)时钟频率可以使用最小和最大DS3(E3)时钟频率(±20ppm)计算。结果如下表所示。

| 模式 | 时钟 | 最小兆赫 | 最大兆赫 |

| DS3 C 位 | 储能系统 | 6.306146 (-927ppm) | 6.306398 (-887ppm) |

| DS3 M13 | 储能系统 | 6.311889 (-17.6页) | 6.312142(+22.5页/分钟) |

| G.747 C 位 | 储能系统 | 6.306146 (-927ppm) | 6.306398 (-887ppm) |

| G.747 M13 | 储能系统 | 6.311889 (-17.6页) | 6.312142(+22.5页/分钟) |

| E3 | E2 | 8.446393 (-190ppm) | 8.446731 (-150ppm) |

参考简单的发送时钟图,当FIFO超过一半满时,DS1(E1)端口将使用DS2(E2)帧中的填充位发送额外的数据位。FIFO使用内部DS1(E1)时钟清空,该时钟由FIFO与外部DS1(E1)时钟解耦。平均而言,内部时钟与外部时钟的频率相同,因为FIFO中的电平用于生成内部时钟,使FIFO接近半满。输入DS1(E1)时钟可能有很多抖动,并且可能突发。

DS1(E1)时钟频率的最大范围由填充量决定。填充比可以从0%到100%。DS1(E1)最大和最小频率的确定公式如下:

| 模式 | DS1(E1) 频率公式 |

| DS3 C 位 | DS1 频率 = (288 - 填充速率) / 1176 x DS2 频率 |

| DS3 M13 | DS1 频率 = (288 - 填充速率) / 1176 x DS2 频率 |

| G.747 C 位 | E1 频率 = (273 - 填充速率) / 840 x DS2 频率 |

| G.747 M13 | E1 频率 = (273 - 填充速率) / 840 x DS2 频率 |

| E3 | E1 频率 = (206 - 填充速率) / 848 x E2 频率 |

通过将DS1(E1)填充速率设置为2%和2%,可以使用最小和最大DS1(E1)时钟频率传输绝对最小和最大DS0(E100)时钟频率。结果如下表所示:

| 模式 | 时钟 |

最小兆赫(100% 填充 ,最低 DS2(E2)) |

最大兆赫(0% 填充 与最大 DS2(E2)) |

| DS3 C 位 | 储能系统 | 1.539000 (-3238ppm) | 1.544424 (+275ppm) |

| DS3 M13 | 储能系统 | 1.540402 (-2331ppm) | 1.545831 (+1186ppm) |

| G.747 C 位 | E1 | 2.041990 (-2935ppm) | 2.049579 (+771ppm) |

| G.747 M13 | E1 | 2.043850 (-2026ppm) | 2.051446 (+1683ppm) |

| E3 | E1 | 2.041876 (-2990ppm) | 2.051918 (+1913ppm) |

实际的最小和最大DS1(E1)时钟频率与最小和最大DS2(E2)时钟频率相反,因此最大DS1(E1)时钟频率由最小DS2(E2)时钟频率设置,填充率为0%。结果如下表所示:

| 模式 | 时钟 |

最小兆赫(100% 填充 ,最低 DS2(E2)) |

最大兆赫(0% 填充 与最大 DS2(E2)) |

| DS3 C 位 | 储能系统 | 1.539062 (-3198ppm) | 1.544362 (+235ppm) |

| DS3 M13 | 储能系统 | 1.540463 (-2291ppm) | 1.545769 (+1145ppm) |

| G.747 C 位 | E1 | 2.042072 (-2895ppm) | 2.049497 (+731ppm) |

| G.747 M13 | E1 | 2.043932 (-1986ppm) | 2.051364 (+1643ppm) |

| E3 | E1 | 2.041957 (-2950ppm) | 2.051836 (+1873ppm) |

DS1(E1) 输入时钟

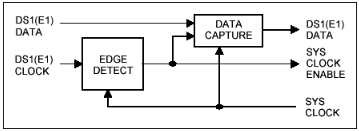

DS3112使用DS1(E1)时钟对DS3(E3)输入时钟进行采样,并检测用于使能内部高速系统时钟的低到高转换,持续一个时钟周期。这种采样消除了芯片中不必要的时钟域。在DS1(E1)时钟输入端检测到低至高边沿后,由高速系统时钟对相关的DS1(E1)数据进行采样。

图2.DS1(E1) 输入时钟采样。

接收时钟

在接收端,提供DS3(E3)时钟,DS2(E2)和DS1(E1)时钟频率基于嵌入在开销中的C位填充码从中派生。DS1(E1)时钟是使用每个DS1(E1)端口的DLL生成的。可以选择使用外部公共接收DS1(E1)时钟,但这超出了本应用笔记的范围。DS3(E3)、DS2(E2)和DS1(E1)时钟频率与在源端传输的时钟频率完全相同。16至28个DS1(E1)发射时钟中的每一个都可以不同,每个时钟频率将在信号被解多的接收器上重新创建。

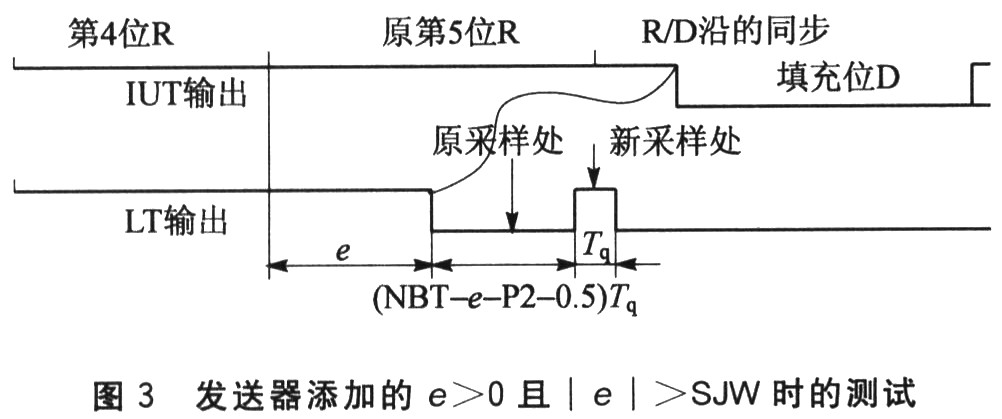

图3.接收时钟图。

DS2(E2) 内部时钟

为发送时钟给出的时钟频率公式也适用于接收时钟。DS2(E2)时钟由生成格式的设备决定。尽管它们的公差应为 ±30ppm,但根据 0% 至 100% 的填充率,它们可能处于极端状态。请注意,DS2 最小频率与 DS2 C 位模式下的 DS3 频率相同。下表列出了基于DS2(E2)最小和最大频率以及3%和3%填充率的绝对最坏情况DS0(E100)内部时钟:

| 时钟 | 最小兆赫 | 最大兆赫 |

| 储能系统 | 6.306146 (-927ppm) | 6.315797 (+602ppm) |

| E2 | 8.435206 (-1514ppm) | 8.457919 (+1174ppm) |

DS1(E1) 内部时钟

DS1(E1)时钟源自DS2(E2)时钟和DS2(E2)中的C位代码 开销。绝对最坏情况下的DS1(E1)时钟,可用于将数据放入接收FIFO 基于绝对最坏情况下的DS2(E2)时钟以及0%和100%填充,下表列出了这些填充物:

| 模式 | 最小兆赫 | 最大兆赫 |

| DS3 C 位 | 1.539000 (-3238ppm) | 1.546726 (+1765ppm) |

| DS3 M13 | 2.041990 (-2934ppm) | 2.052634 (+2262ppm) |

| E3 | 2.039171 (-4311ppm) | 2.054636 (+3240ppm) |

下表列出了基于DS1(E1)行业规定的时钟频率范围±2ppm以及2%和30%的填充速率,内部DS0(E100)时钟范围:

| 模式 | 最小兆赫 | 最大兆赫 |

| DS3 C 位 | 1.540382 (-2343ppm) | 1.545842 (+1193ppm) |

| DS3 M13 | 2.043824 (-2039ppm) | 2.051462 (+1690ppm) |

| E3 | 2.042203 (-2830ppm) | 2.052288 (+2094ppm) |

DS1(E1)输出时钟

DS1(E1)输出时钟通过将DS3(E3)时钟除以两个可能的整数之一来创建。DS1 时钟的除数为 29 和 28,E1 的除数为 17 和 16,G.747 的除数为 22 和 21。根据 FIFO 是超过一半还是小于一半满来选择其中一个除数。当FIFO超过一半满时,较小的除数用于更快地清空FIFO。DS1(E1)输出时钟将在两个频率之间切换,以重新创建发送器的平均时钟频率。

图4.DS1 DLL。

DS1(E1)时钟速率从以下频率切换:

| 模式 | RCLK | 除数 | DS1(E1) 频率 |

| 储能系统 | DS1 分钟 | DS3/29 | 1.542621 (-893ppm) |

| 储能系统 | DS1 最大值 | DS3/28 | 1.597714 (+3489ppm) |

| G.747 | E1 分钟 | DS3/22 | 2.033455 (-7102ppm) |

| G.747 | E1 最大 | DS3/21 | 2.130286 (+40179ppm) |

| E3 | E1 分钟 | E3/17 | 2.021647 (-12867ppm) |

| E3 | E1 最大 | E3/16 | 2.148000 (+48828ppm) |

参考电路

| 信号 | 宽容 | 最低兆赫 | 典型兆赫 | 最大兆赫 |

| 储能系统 | ±20ppm | 44.735106 | 44.736000 | 44.736894 |

| 储能系统 | ±30ppm | 6.311811 | 6.312000 | 6.312189 |

| 储能系统 | ±50ppm | 1.543923 | 1.544000 | 1.544077 |

| E3 | ±20ppm | 34.367313 | 34.368000 | 34.368687 |

| E2 | ±30ppm | 8.447747 | 8.448000 | 8.448253 |

| E1 | ±50ppm | 2.047898 | 2.048000 | 2.048102 |

审核编辑:郭婷

-

芯片

+关注

关注

455文章

50832浏览量

423813 -

fifo

+关注

关注

3文章

388浏览量

43690 -

端口

+关注

关注

4文章

966浏览量

32084

发布评论请先 登录

相关推荐

DS3112 LRCLKx Low Speed Clock

DS325X、DS316X、DS317X和DS318X中时钟

DS3112 Clock Rates and Frequen

DS325X、DS316X、DS317X和DS318X中时钟

CAN标准中的时钟容差修正建议

基于SERDES时钟的频率跟随的设计

了解时钟容差对高性能Σ-Δ型ADC中50/60Hz噪声抑制的影响

DS3112 接口 - 电信

DS3112+W 接口 - 电信

DS3112 LRCLKx低速时钟恢复工作原理

DS3112发送时钟的时钟速率和频率容差

DS3112发送时钟的时钟速率和频率容差

评论