最近用12Track的工艺实现老代码设计,代码例化的STD Cell都是直接例化的12T工艺器件名,不利于替换工艺。

当我需要切换工艺到9T时,就需要把12T的器件名改成9T的器件名,.v代码几百个,这时候手工修改会疯掉,必须脚本来。

所以建议verilog代码一定要隔离开具体工艺,用wrap层包封好,进行隔离,利于切换工艺。

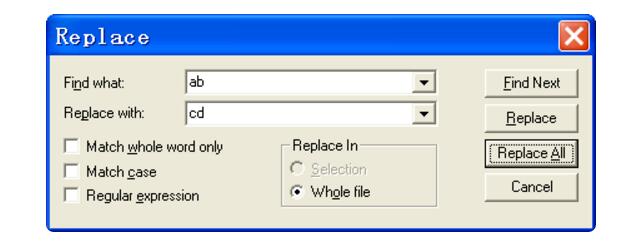

用linux命令grep搜索到含A12的行并全部替换为A9,可以使用sed命令结合正则表达式进行行内容的替换。

以下是一个使用grep和sed实现您要求的示例命令:

grep "A12" input.v| sed 's/A12/A9/g' > output.v

这个命令将会搜索名为input.v的文件中包含"A12"的行,并将其中的所有"A12"替换为"A9",然后将结果输出到名为output.v的文件中。

如果希望直接在原始文件上进行替换而不是生成一个新的文件,请使用-i选项(例如:sed -i 's/A12/A9/g' input.v),切记备份源文件!!!!

grep搜索所有文本文件含A12的行并全部替换为A9,可以使用grep结合find命令来搜索所有文本文件中包含"A12"的行,并使用sed进行替换。

如果不想在原始文件上直接进行替换,可以删除-i选项,

并将结果重定向到另一个文件中。

审核编辑:刘清

-

Linux系统

+关注

关注

4文章

593浏览量

27389 -

STD

+关注

关注

0文章

36浏览量

14356

原文标题:如何替换所有.v代码中的字符串

文章出处:【微信号:全栈芯片工程师,微信公众号:全栈芯片工程师】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

python字符串拼接方式了解

keil如何全局替换字符串

替换所有.v代码中字符串的方法

替换所有.v代码中字符串的方法

评论