一、什么是去耦以及为什么要去耦?

模电书上讲的去耦大多是讲电源的去耦,就是一个电路的各个单元共用同一电源供电,为了防止各单元之间的耦合,需加去耦电路。

造成耦合的原因有:

1. 数字电路——在电平翻转时的瞬间会有较大的电流,且会在供电线路上产生自感电压。

2. 功率放大电路——因电流较大,此电流流过电源的内阻和公共地和电源线路时产生电压,使得电源电压有波动。

3. 高频电路——电路中有高频部分因辐射和耦合在电源上产生干扰。

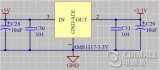

这些干扰会对同一供电电路中的对电源电压较敏感或精度要求较高的部分. 比如微弱小信号放大器、AD转换器等产生干扰,或者相互干扰,严重时使整个电路无法工作。为了阻止这种干扰,可以加电源去耦电路来解决,一般常用的电源去耦电路有RC或LC电路,要求较高的另加用稳压电路。

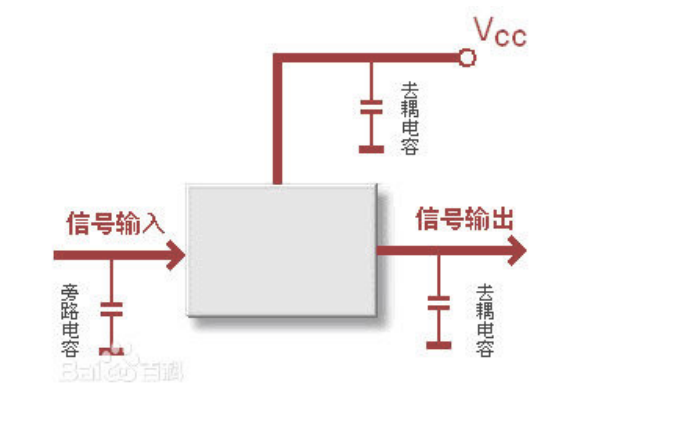

一般需要在以下位置放置去耦电容:

接插件的电源和信号引脚﹔

运放/比较器的电源引脚﹔

ADC和DAC的电源引脚;电路板上其他有可能发生电流波动的位置。

二、为什么电容可以去耦?

1)电源噪声一般是高频交流分量,而电容具有通交隔直的功能,所以电容以去除高频噪声分量,实现去耦。

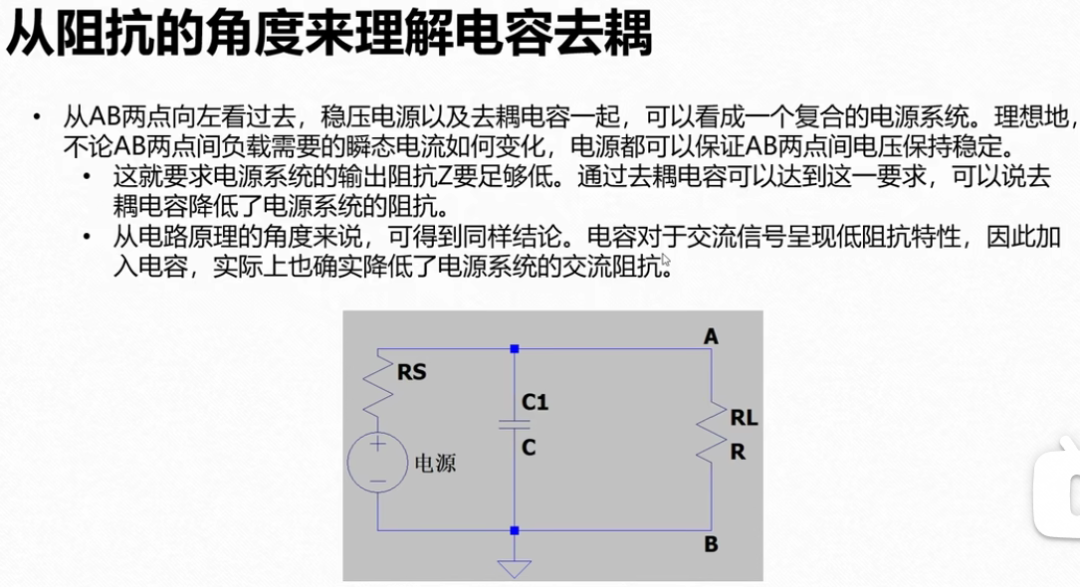

2)通过降低电源系统输出阻抗,可以减少后级的负载变化对于电源输出电压的影响,而电容可以实现降低输出阻抗的要求。(因为输出电阻越小,可以减小负载瞬时电流突然变大导致的输出电压跌落(也就是电压波动))。

(另一种降低输出阻抗的去耦方式是缩短电源层和地层的距离)。

三、理想电容和实际电容的特性

虽然我们都知道电容具有通交隔直的功能。但是在实际使用过程中,我们还需要了解实际电容的特性,这样才能选择根据去耦电路的实际需求去选择最合适的电容。

1)理想电容VS实际电容:

理想的电容:本身不会产生任何能量损耗,在任意频率下都呈现容性。

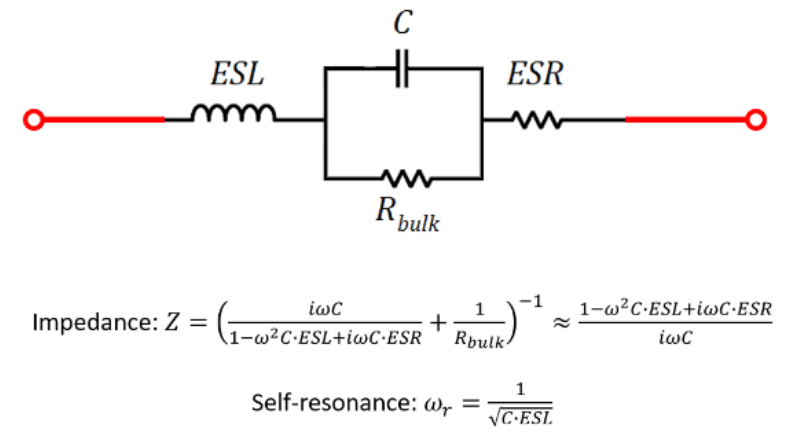

实际电容:实际上,因为制造电容的材料有电阻,电容的绝缘介质有损耗,各种原因导致电容变得不“完美”。实际上的电容等于等效串联电感ESL、等效串联电阻ESR、与理想电容的串联,因此其特性与频率有关。

2)实际电容的模型:

实际的电容会存在一些能量损耗,在外部的表现就像一个电阻跟电容串联在一起(等效串联电阻ESR)。另一方面,由于引线、卷绕等物理结构因素,电容内部还存在着电感成分(等效串联电感ESL)。电容器中存在一些泄漏或体电阻(体电阻Rbulk),它与理想电容、ESL 和 ESR 并联存在。下图显示真正实际的电容模型和阻抗。

由于电容器中的介电材料具有很强的绝缘性,因此 Rbulk 的值通常非常大(~100 GOhms),因此在计算电容器的阻抗时可以忽略它。因此,我们在选择电容时需要重点关注ESL和ESR值。

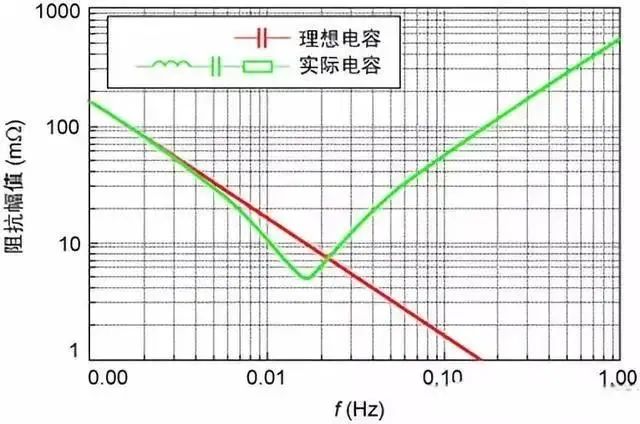

3)ESR和ESL对于电容滤波作用的影响:

ESR:——会导致电压突变!

ESR通常是在100mΩ ~ 1000mΩ不等,假如你的芯片电源会有一个非常短暂的100mA的peak current, 而且这个电流几乎是去耦电容来提供的, 如果你的电容ESR有1Ω,想象一下100mA的电流流过这个电阻, 到达另一端的时候, 已然有了100mV的压降了.

ESL——会影响滤波的工作频率和高频滤波效果。

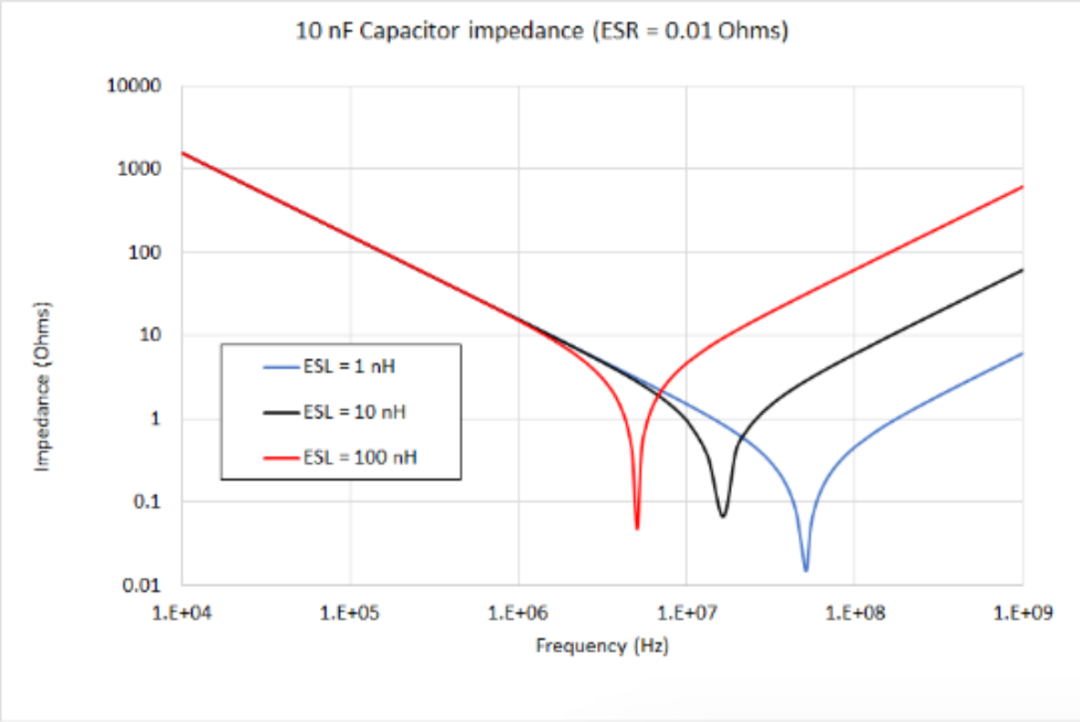

下图显示了 ESL 如何影响具有 0.01 欧姆 ESR 的理论 10 nF 电容器的阻抗。各种曲线显示了不同 ESL 值(1 nH、10 nH 和 100 nH)的阻抗曲线。

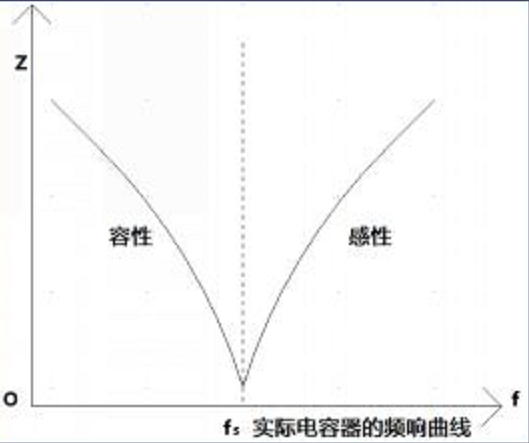

从上图中,我们看到阻抗在自谐振频率(也就是最低那个点)之前是容性的,(阻抗随频率升高而减少,呈现容性)而与 ESL 值无关;然后在高于自谐振频率之后变为感性(因为这时候阻抗随着频率升高而增大,呈现感性)。

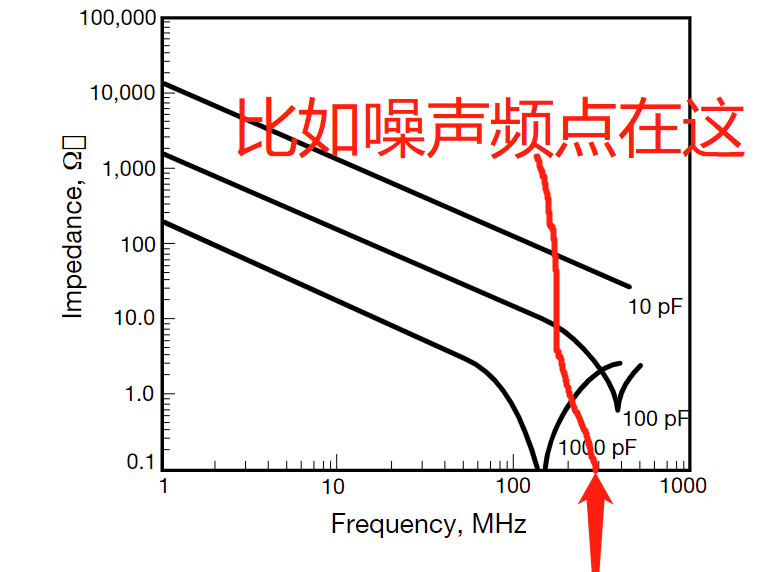

电容的最佳滤波效果就是这个自谐振频率处,所以对于EMC的RE辐射问题,我们一般都是将辐射超标点频率作为自谐振频率点,然后根据这个曲线去选电容。

这样降低ESL就有双重意义了:

1.降低ESL,可以提高自谐振频率,也就是上图中最低那个点的频率右移。这样就可以让电容可以前面更宽的范围保持容性。

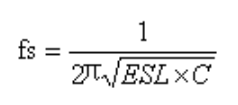

因为:电容的LC自谐振频率Fs,是由下面的公式计算的:

2.降低ESL,降低高频区域的阻抗,因为在频率超过超过自谐振频率fs之后,电容呈现的是感抗,跟ESL相关,这时候降低ESL,就可以降低电容的阻抗。

所以结论就是:为了提高电容的去耦滤波作用,一定要选用低ESR和低ESL的电容!

(一般电容容值越高,ESL越大,这就是为什么一般用大电容滤低频,小电容滤高频的原因(因为小电容ESL小,自谐振频率高))

四、去耦电容的选型——容值及自谐振频率

1)容值

对于芯片电源引脚级别的滤波,一般可以从容值方面进行选型:

可以参照以下三种方法:

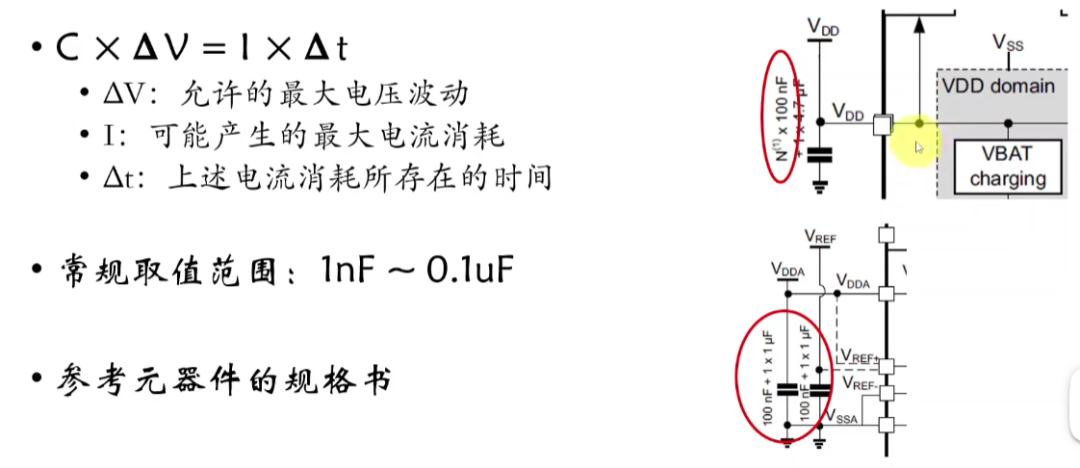

1.1)参照芯片规格书overshoot电压手动计算

1.2)经验值(按照100倍原则:比如10pF, 1nF,0.1uF)

2)自谐振频率

对于EMC RE辐射超标问题,或者某些对于电源纹波特别敏感的芯片,这时候就要根据噪声频点,并结合电容的自谐振频率去选电容了。

如果是想要滤除单个点噪声,可以选择噪声频点略低于自谐振频率的电容,这时候可以达到最佳的滤波效果。

如果找不到合适封装的怎么办?

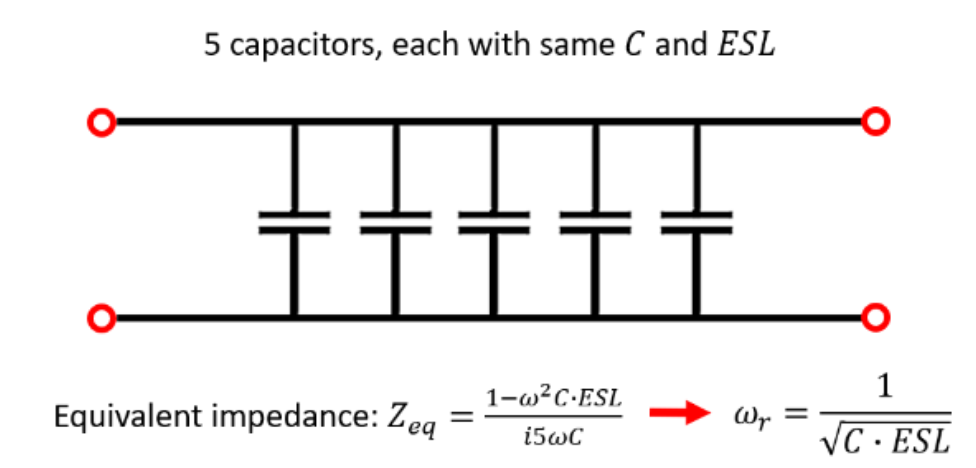

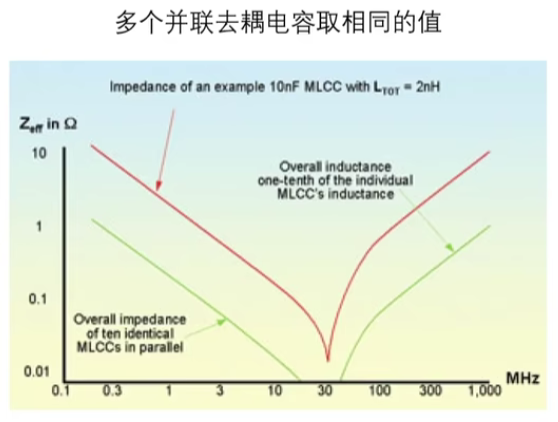

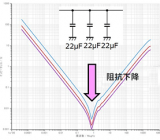

那可以选择多个容值的电容,将他们并联起来,并联使用多个相同的电容会增加总等效电容并降低 PDN 阻抗,但不会改变谐振频率。(多个电容并联可以降低ESL)

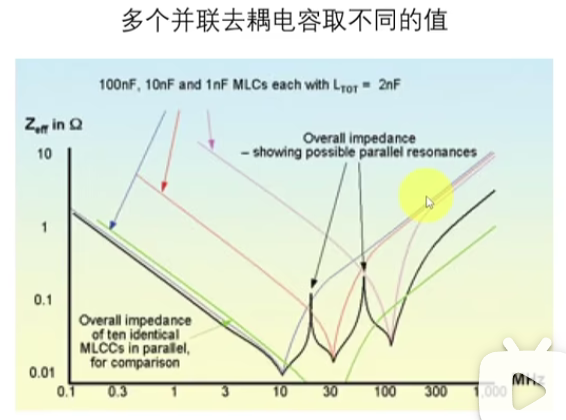

如果噪声频点是一个范围,那就需要选择多个容值的电容。

五、去耦电容的放置要求

1)就近原则:

去耦电容应尽可能的靠近芯片的电源引脚。减小去耦电容和芯片之间走线的寄生电感,去耦效果更好。

2)越小越近的原则:

小容值电容最靠近芯片,然后按照容值递增的原则依次远离芯片(远离是相对的,前提是遵循就近原则)。小电容负责高频响应,应该更靠近芯片缩短响应的时间。并且小电容可以滤除高频噪声,若距离芯片太远,则电容和芯片之间的走线会重新拾取噪声,削弱去噪效果。

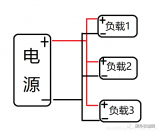

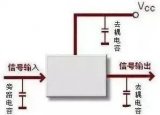

3)电源线先经过去耦电容再连接至芯片引脚

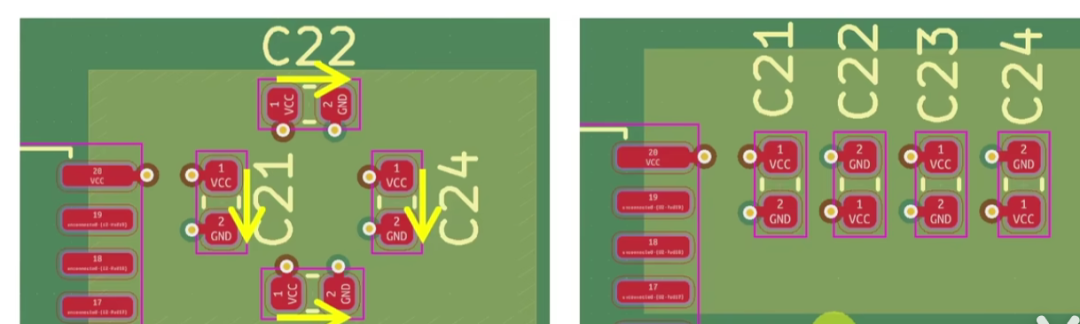

4)多个电容并联时,最好不要平行并排放(有互感),可以改为:

审核编辑:汤梓红

-

放大电路

+关注

关注

103文章

1779浏览量

106450 -

噪声

+关注

关注

13文章

1114浏览量

47337 -

模电

+关注

关注

21文章

464浏览量

36341 -

去耦电容

+关注

关注

11文章

315浏览量

22293

原文标题:探索去耦电容,噪声无所遁形

文章出处:【微信号:knifewheat,微信公众号:小麦大叔】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

去耦电容有什么作用

去耦电容的作用和选型

去耦电容的作用和选型

评论