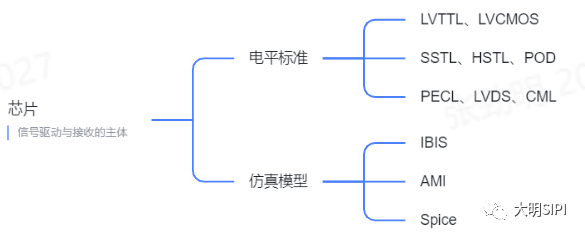

这一节开始我们介绍信号完整性的另一个要素--芯片(驱动、接收器件),主要涉及到如下内容:

有一定基础的同学也可以直接略过此部分内容,但我觉得在介绍IBIS模型、介绍SIPI仿真之前,还是有必要先讲一下各种电平标准,这样有助我们更好的完成信号完整性仿真和分析。

驱动和接收器参数

在介绍具体的电平标准前需要介绍一些概念:

-

驱动器:

- 输出高电平(Voh):保证逻辑门的输出为高电平时的输出电平的最小值,逻辑门的输出为高电平时的电平值都必须大于此Voh。也就是说输出高电平的最低值可能会达到Voh。

- 输出低电平(Vol):保证逻辑门的输出为低电平时的输出电平的最大值,逻辑门的输出为低电平时的电平值都必须小于此Vol。也就是说输出低电平的最高值可能会达到Vol。

-

接收器:

- 输入高电平(Vih):保证逻辑门的输入为高电平时所允许的最小输入高电平,当输入电平高于Vih时,则认为输入电平为高电平。

- 输入低电平(Vil):保证逻辑门的输入为低电平时所允许的最大输入低电平,当输入电平低于Vil时,则认为输入电平为低电平。

- 阀值电平(Vt):数字电路芯片都存在一个阈值电平,就是电路刚刚勉强能翻转动作时的电平。它是一个界于Vil、Vih之间的电压值,对于CMOS电路的阈值电平,基本上是二分之一的电源电压值,但要保证稳定的输出,则必须要求输入高电平> Vih,输入低电平

对于一般的逻辑电平,以上参数的关系如下:Voh > Vih > Vt > Vil > Vol。

我们在做SI分析时,用Vih、Vil来衡量仿真波形的高、低电平的噪声裕量。在考虑不同逻辑电平接口之间的互连时我们必须充分考虑驱动器的Voh和接收器的Vih以及驱动器的Vol和接收器的Vil之间的裕量是否足够,如果裕量很小,那么两种接口的电平对接就存在一定的风险。

常用的逻辑电平有 TTL、CMOS、LVTTL、LVCOMS、SSTL、HSTL、CML、ECL、PECL、LVPECL、LVDS等。这些逻辑电平接口都有自身的结构特点,为了能够获得最优的信号质量我们必须对所使用的电平接口输入输出结构有充分的了解。只有如此才能够设计出传输线和驱动、接收器完好匹配的电路。另外,我们需要对常用的逻辑电平的电气特性有充分了解,这有助我们判定仿真测试得到的结果是否满足要求。在实际的设计中经常遇到不同电平接口之间的互连,这就导致驱动器和接收器的共模电平、电压摆幅很可能不相同,为了数据的安全可靠传输就需要考虑各种电平接口之间的转换。

在各种逻辑电平的互连设计中,需要尊需以下基本原则:

-

电平关系, 驱动器件的输出电压必须处在负载器件所要求的输入电压范围,包括高、低电压值。应保证合格的噪声容限(Vohmin-Vihmin≥0.4V,Vilmax-Volmax≥0.4V),并且输出电压不超过输入电压允许范围,否则有可能导致器件损坏。

-

驱动能力 ,驱动器件必须能对负载器件提供灌电流最大值。驱动器件必须对负载器件提供足够大的拉电流,关系到驱动器的带负载能力和总线速率。对于一般驱动器来说驱动电流都是mA级别的,相比而言各种逻辑电平的输入电流都是uA级的,对于TTL、CMOS等传统的低速接口来说可以驱动很多器件工作。高速的SerDes链路大部分都是CML电平而且都是点到点的拓扑结构,此时更加关注信号的边沿变化率,如果边沿变化率太缓可能无法支持过高的信号速率。但也要注意长的布线链路也会造成比较大的损耗,这就需要驱动器可以通过驱动能力的调整来改善信号的幅度,对于高速serdes来说往往不仅仅是驱动能力的问题,还需要配合加重、均衡等技术来改善信号质量。

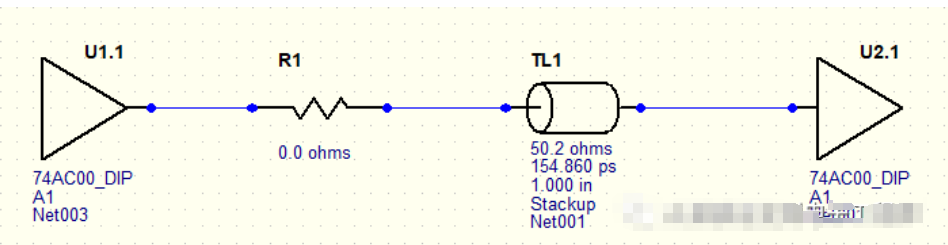

从另一方面驱动能力反映的是驱动器的 输出阻抗 ,从阻抗方面理解更有利于我们 保证驱动器和传输线之间的阻抗匹配 。

-

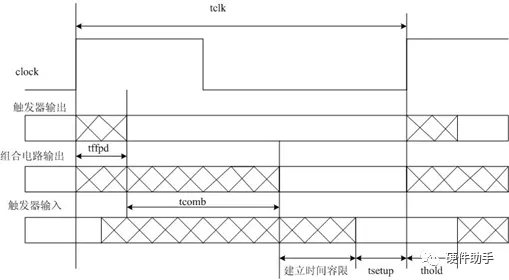

时延特性, 在高速信号进行逻辑电平转换时,往往会带来一定的延时。而且同一器件同一总线不同管脚的输出延时会有一定的偏差,这一延时偏差会很大程度上限制总线速率,时序设计时一定要充分考虑。

-

如果两种电平不能直接相连,则需要借助电平转换芯片。选用电平转换逻辑芯片时应慎重考虑,反复对比。通常逻辑电平转换芯片为通用转换芯片,可靠性高,设计方便,简化了电路,但对于具体的设计电路一定要考虑以上三种情况,合理选用。需要充分考虑电平转换芯片对上升/下降时间的影响,应保证Tplh和Tphl满足电路时序关系的要求和EMC的要求。

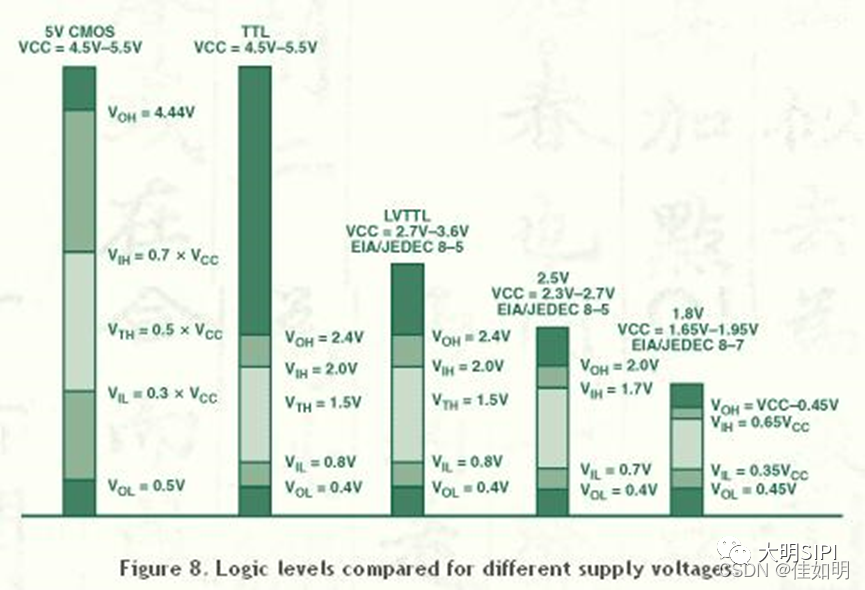

TTL 、CMOS电平

TTL和CMOS的逻辑电平是比较传统的低速电平接口,不能提供很快的开关速度,按典型电压可分为四类:5V系列、3.3V系列,2.5V系列和1.8V系列。5V系列比较通用被称为TTL或者CMOS电平,3.3V及以下的逻辑电平被称为低电压逻辑电平,常用的为LVTTL或LVCMOS电平。一般的数字设计基础教材中都有详细介绍。这里给出不同系列的逻辑电平之间的逻辑电平对比,并简要分析何种情况下不同电平接口可以直接互连,什么情况下不能直接互连。

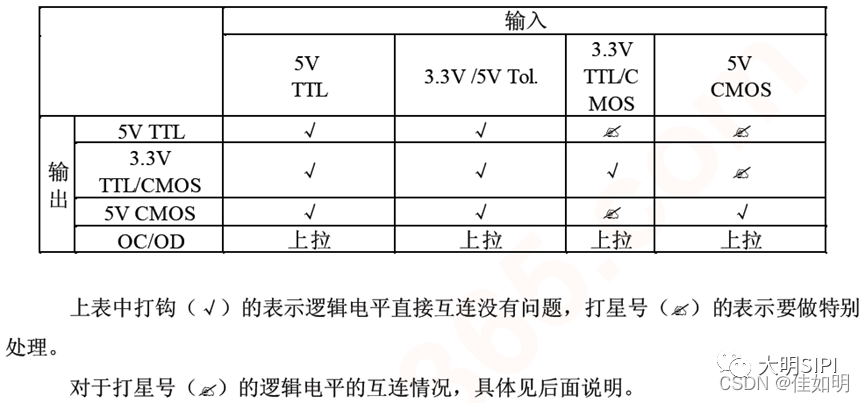

常用的TTL和CMOS电平分类有:5V TTL、5V CMOS、3.3V TTL/CMOS、3.3V/5VTol.、和OC/OD门。其中:

- 3.3V/5V Tol.是指输入是3.3V逻辑电平,但可以忍受5V电压的信号输入。

- 3.3V TTL/CMOS逻辑电平表示不能输入5V信号的逻辑电平,否则会出问题。

3.3V和5V逻辑电平的互连

注意某些5V的CMOS逻辑器件,它也可以工作于3.3V的电压,但它与真正的3.3V器件(是LVTTL电平)不同,比如其VIH是2.31V(=0.7×3.3V,工作于3.3V)而不是2.0V,因而与真正的3.3V器件互连时工作不太可靠。因为这种接法无形中减小了高电平的噪声裕量,在进行信号完整性仿真时需要特别注意。

值得注意的是有些器件有单独的输入或输出电压管脚,此管脚接3.3V的电压时,器件的输入或输出逻辑电平为3.3V的逻辑电平信号,而当它接5V电压时,输入或输出的逻辑电平为5V的逻辑电平信号,此时应该按该管脚上接的电压的值来确定输入和输出的逻辑电平属于哪种分类。

** OC/OD输出加上拉电阻可以驱动所有逻辑电平。**

5V TTL和3.3V/5VTol.可以被除了2.5V、1.8V外的所有逻辑电平驱动

由此得到以下逻辑电平匹配表格:

2.5V和3.3V之间的逻辑转换。

-

3.3V TTL/CMOS逻辑电平驱动2.5V CMOS逻辑电平

2.5V的逻辑器件有LV、LVC、AVC、ALVT、ALVC等系列,其中前面四种系列器件工作在2.5V时可以容忍3.3V的电平信号输入,而ALVC不行,所以可以使用LV、LVC、AVC、ALVT系列器件来进行3.3VTTL/CMOS逻辑电平到2.5V CMOS逻辑电平的转换。

-

2.5V CMOS逻辑电平驱动3.3V TTL/CMOS逻辑电平

2.5V CMOS逻辑电平的VOH为2.0V,而3.3VTTL/CMOS的逻辑电平的VIH也为2.0V,所以直接互连的话可能会出问题(除非3.3V的芯片本身的VIH参数明确降低了)。此时可以使用双轨器件SN74LVCC3245A来进行2.5V逻辑电平到3.3V逻辑电平的转换。

-

驱动器

+关注

关注

54文章

8365浏览量

147588 -

接收器

+关注

关注

14文章

2486浏览量

72488 -

信号完整性

+关注

关注

68文章

1418浏览量

95845 -

AVC

+关注

关注

0文章

22浏览量

11037 -

CMOS电平

+关注

关注

0文章

19浏览量

7265

发布评论请先 登录

相关推荐

2011信号及电源完整性分析与设计

信号完整性与电源完整性的仿真分析与设计

高速串行总线的信号完整性验证

介绍信号完整性的另一个要素—芯片

介绍信号完整性的另一个要素—芯片

评论