关键要点

・桥式电路中的死区时间设置与损耗和安全性有关,因此需要充分确认。

・死区时间的理想值是不直通的最短时间。

・由于开关器件的开关速度会受温度和批次变化等因素影响而发生波动,因此在设计过程中,除了最短时间外,还应留有余量。

PFC电路:死区时间理想值的考量

在本文中,我们将探讨如何估算桥式电路中理想的死区时间。

电路示例

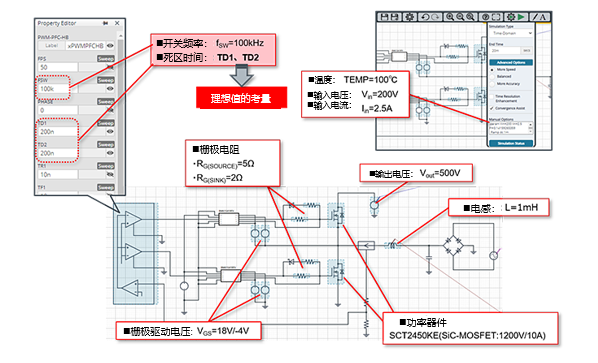

电路以Power Device Solution Circuit/AC-DC PFC的一览表中的仿真电路“A-6. PFC CCM Synchro Vin=200V Iin=2.5A”为例(参考图1)。关于更详细的电路图,还可以通过这里查看。

由于该电路是进行同步整流工作的电路,所以我们通过仿真来探讨高边(HS)和低边(LS)SiC MOSFET SCT2450KE的死区时间理想值,即不直通的最短时间。死区时间可以通过仿真工具的PWM控制器参数TD1(HS)和TD2(LS)来分别设置。

图1:PFC仿真电路“A-6. PFC CCM Synchro Vin=200V Iin=2.5A”

咨询或购买产品

扫描二维码填写相关信息

将由工作人员与您联系

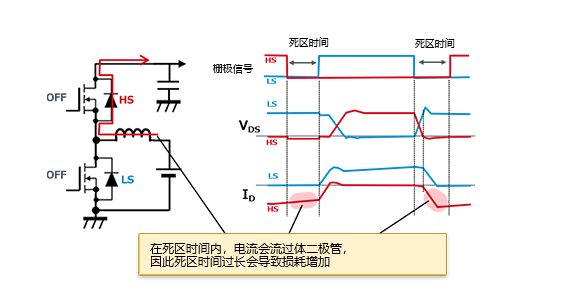

死区时间内的损耗

图2表示死区时间内的电流流动情况。在桥式结构的电路中,要防止直通电流,就需要确保足够的死区时间长度,但如果将死区时间设置得过长,会导致损耗增加。这是因为在死区时间内,SiC MOSFET处于OFF状态,因此电流会流过体二极管。通常,体二极管的导通损耗比较大,其导通时间越长,损耗越大。

图2:死区时间内的电流流动情况

死区时间和功率因数

图3表示死区时间长度与电感电流IL之间的关系。如果死区时间过长,低电压区域可能会变为断续工作状态,电感电流波形可能会失真,功率因数可能会恶化。因此,从功率因数的角度来看,将死区时间设置得过长并非好事。

图3:死区时间长度与电感电流IL的关系

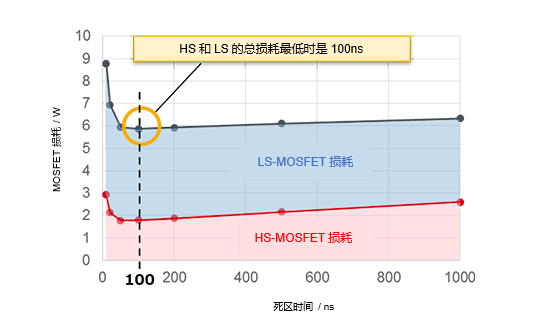

探讨理想的死区时间

图4表示使死区时间变化时SiC MOSFET的损耗仿真结果。

图4:表示使死区时间变化时SiC MOSFET的损耗仿真结果

从图中可以看出,当死区时间在50ns以下时,损耗会因流过直通电流而急剧增加。反之,当延长死区时间时,HS SiC MOSFET的体二极管的导通时间会变长,因此在这种条件下损耗也会增加。SiC MOSFET的损耗最小时,正是死区时间最短(没有直通电流)时,在本例中为100ns时。但是,由于开关速度会随温度和批次差异等因素而波动,因此通常需要留100ns左右的余量。也就是说,在这种情况下,200ns是理想的死区时间。

技术资料下载

我们为您准备了ROHM举办的研讨会的讲义资料和DC-DC转换器的选型指南等可以下载的资料。

查看可以下载的资料清单

“PFC电路:死区时间理想值的考量”相关的文章一览

◇PFC电路的优化

◇Solution Circuit的PFC仿真电路

◇PFC电路:电感调整

◇PFC电路:开关频率的调整

◇PFC电路:探讨适当的栅极驱动电压

◇PFC电路:栅极电阻的更改

◇PFC电路的优化-总结

END

咨询或购买产品

扫描二维码填写相关信息

将由工作人员与您联系

点击阅读原文 了解更多信息

-

罗姆

+关注

关注

6文章

447浏览量

67930

原文标题:R课堂 | PFC电路:死区时间理想值的考量

文章出处:【微信号:罗姆半导体集团,微信公众号:罗姆半导体集团】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

探索 ISL6745A:高精度死区时间控制的桥接控制器

R8C/32C 系列 MCU 深度解析:特性、参数与应用考量

精准剖析 LT4422 理想二极管:特性、应用与设计考量

IGBT死区时间设定指南:死区计算方法、对逆变器的影响、死区优化策略 v2.0

探秘SF-0603SPA-R系列汽车级SMD保险丝:特性、参数与应用考量

MXB12R600DPHFC Si MOSFET:高性能电源管理的理想选择

什么是常见的开关电源的PFC模块与LLC模块

PFC电路与BOOST电路设计实例分享

直流控制系统中PWM功放的频率和死区设置

基于死区补偿的电机低速运行稳定性研究

关于交流负载模式中的CF值设置(上)

基于ST Stellar-E1应用于22KW OBC三相图腾柱PFC的SVPWM控制详解

R课堂 | PFC电路:死区时间理想值的考量

R课堂 | PFC电路:死区时间理想值的考量

评论