对于物理验证中的LVS,需要对各种物理器件进行SpiceVsGDS的比对,基于现在流行的std-cell的库的设计方法,LVS需要对CMOS器件多相应的处理,这里会涉及到一些具体的物理库的知识和小的技巧,这里结合具体的物理设计和CDL形态,一起探讨一下std-cell的在LVS的特殊处理,ICer GO!

标准单元库一瞥

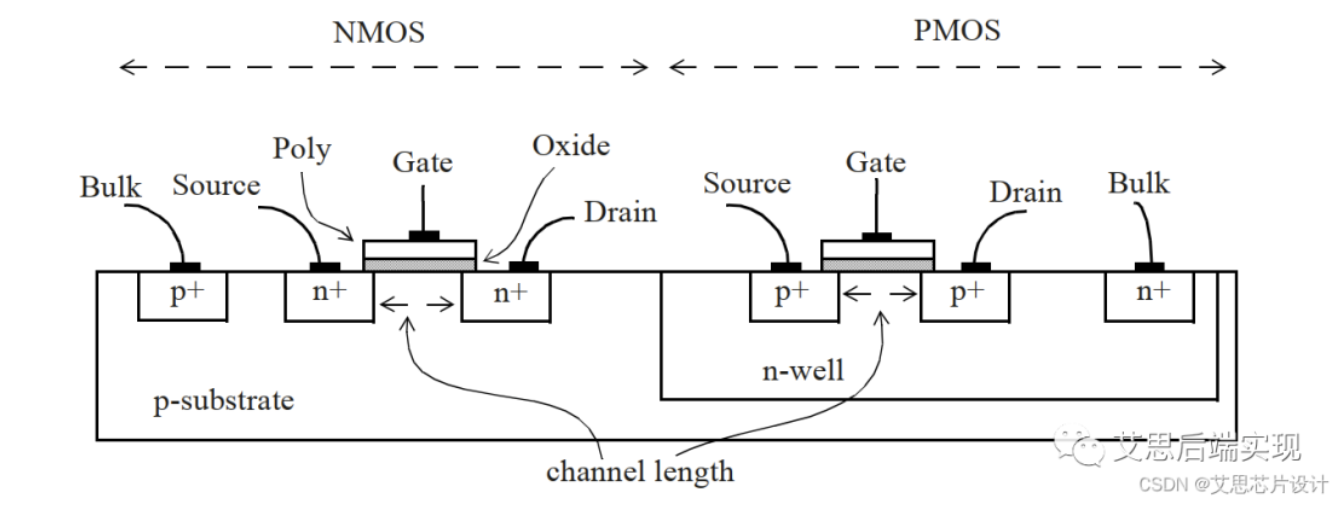

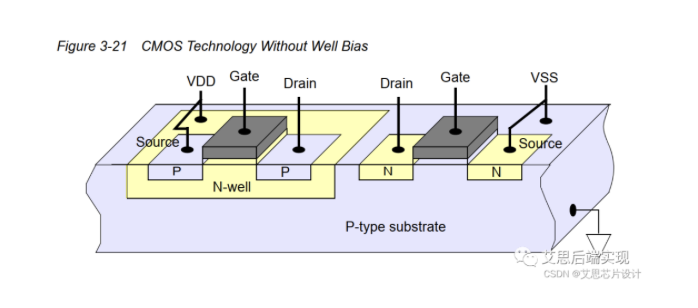

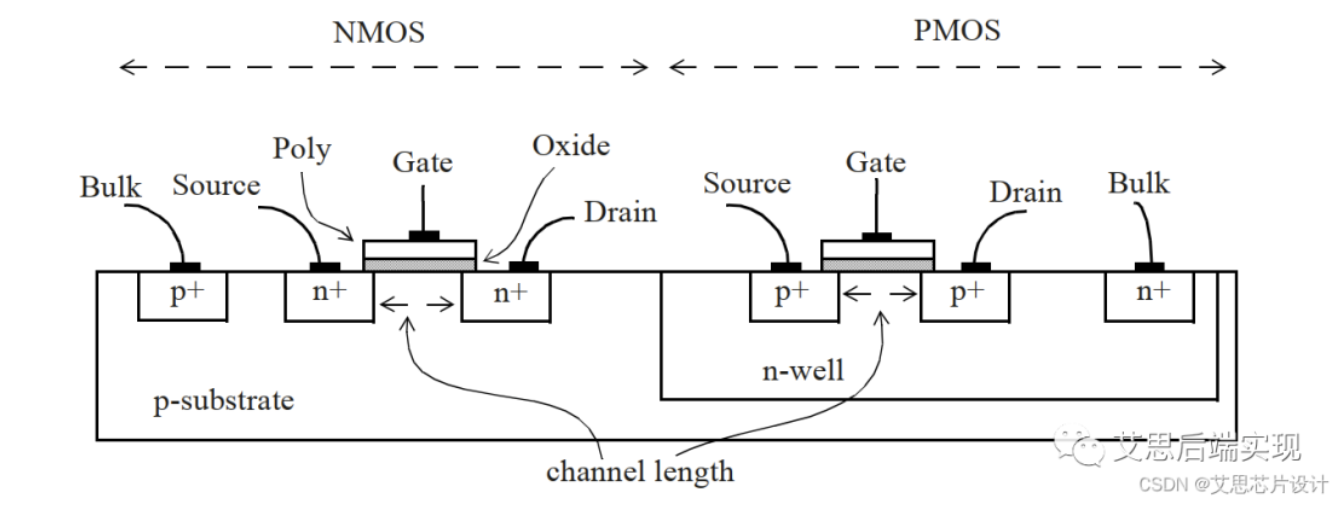

常规的标准单元库(std-cell)是标准的CMOS设计,由于采用P衬底的设计出来的CMOS器件的速度优势,目前业界流行的做法就是采用P型衬底(P substrate)来实现的

-

NMOS 直接坐在P-sub上

-

PMOS 则做在P-sub上的NWELL

譬如下面的一个简单的工艺刨面图

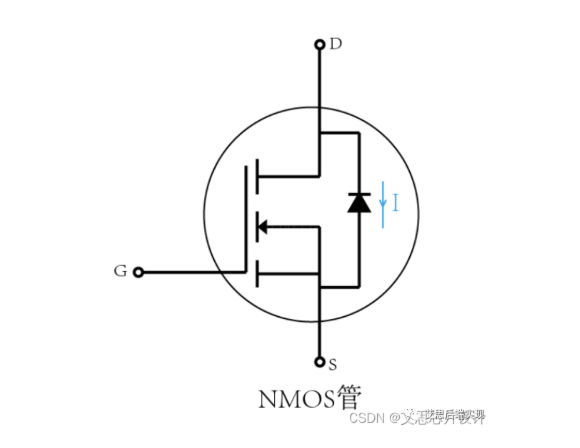

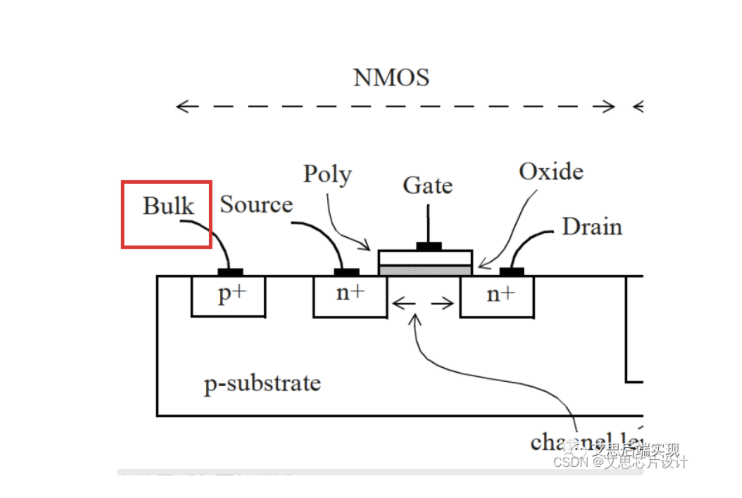

以上边的NMOS为例,通常有更为常见的是下面的一个示意图

比较上述两个图,可以看到,每一个NMOS都会有一个bulk(体)的连接(有些场合也被称作body)

在NMOS里边,这个bulk的作用就是将当前NMOS的P-sub做一个连接,通常P-sub是连接到VSS上的。

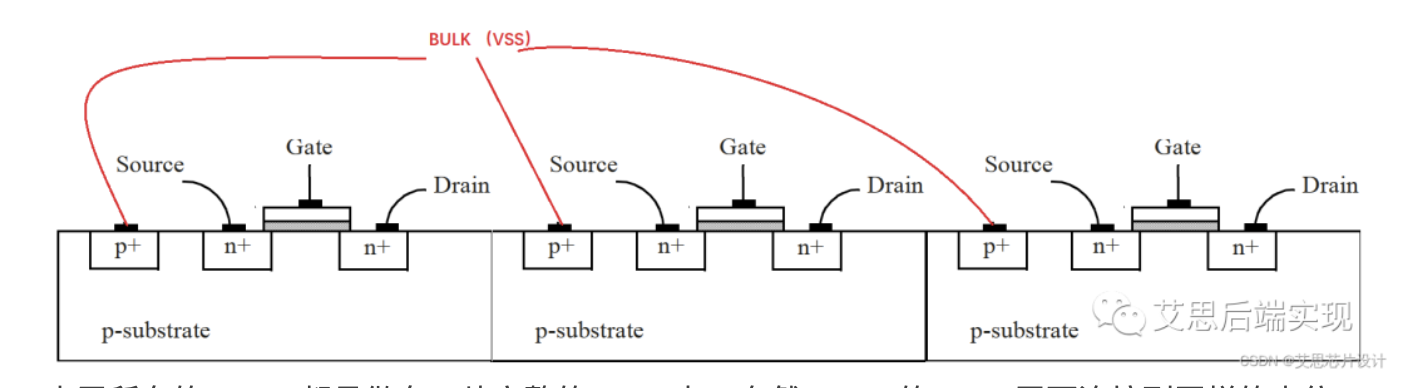

如果芯片里边有非常多的std-cell连续分布(这个也是常规做法),那么在版图里边就会有类似下列的一个刨面图:

由于所有的NMOS都是做在一片完整的P-sub上,自然NMOS的BULK需要连接到同样的电位VSS上,这里就是模拟设计里边常说的TAP 结构了。

可以看到,这个TAP结构完全是一个通用结构,为了节省std-cell的面积,目前业界比较流行的做法就是设计tapless(免TAP)的std-cell,然后使用公用的TAP cell将bulk连接到VSS上,这样对于节省std-cell的面积很有好处,但是考虑到TAP的电位对于std-cell的bulk的影响,工艺会给出具体的TAP的间距(目前流行的做法是checkerBoard/stagger的做法),APR工具为也提供了具体的命令和参数,支持std-cell的这种设计结构。

通过学习std-cell的形态,可以明确下列要点

**- std-cell都是tapless的结构

- bulk需要使用TAP cell 分别将同列的std-cell的P-sub和NWELL分别连接到VSS和VDD上**

LVS的挑战

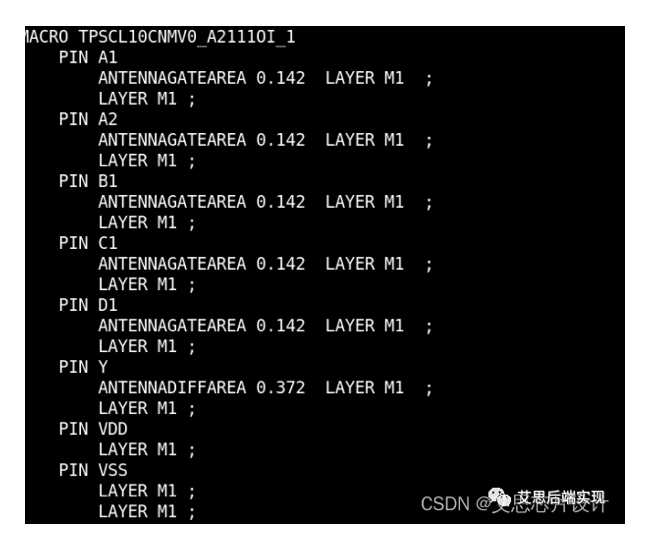

由于bulk在std-cell上PG和信号连接上是没有明显贡献的,对于使用none-bias的流程的std-cell,通常是无法在std-cell看到这个bulk的管脚的,譬如下面LEF的示例:

可以看到,这里有PG管脚的声明,但是没有声明bulk的管脚。

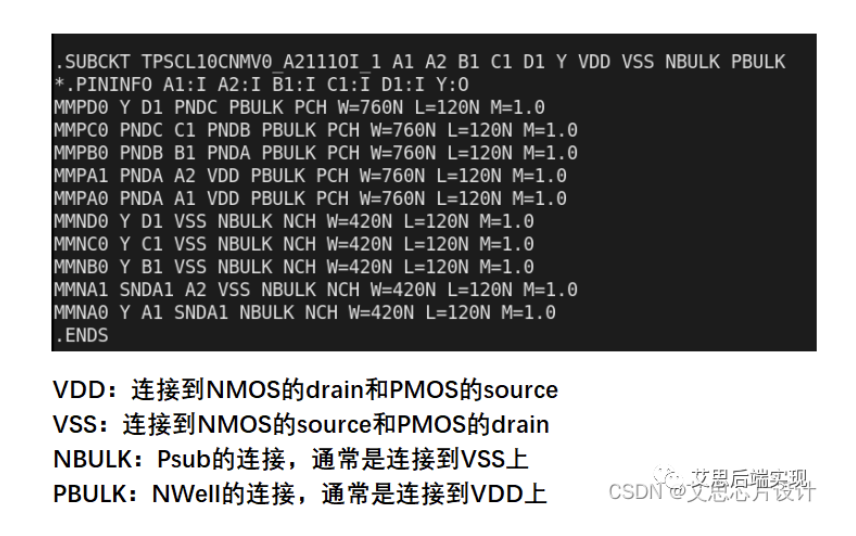

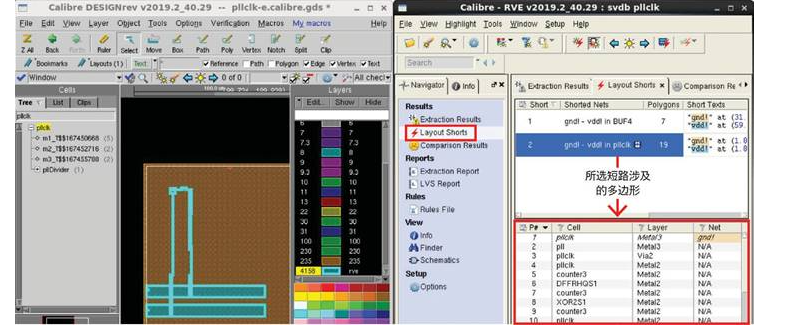

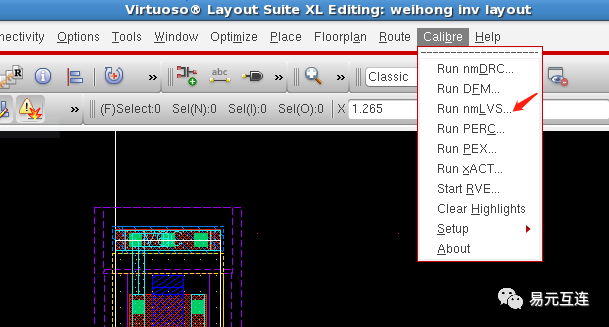

但是对于LVS而言,CMOS是一个四端器件,在验证栅源漏的同时,也需要完成对bulk的连接验证,这个也是符合APR的TAP的布局连接的。所以,这里需要打开CDL来一看究竟,见下图

可以看到,相较LEF而言,最后做LVS的CDL里边,会有bulk的连接描述。对于none-bias的std-cell而言,bulk的物理连接可以简单的连接到PG上,基本如下图

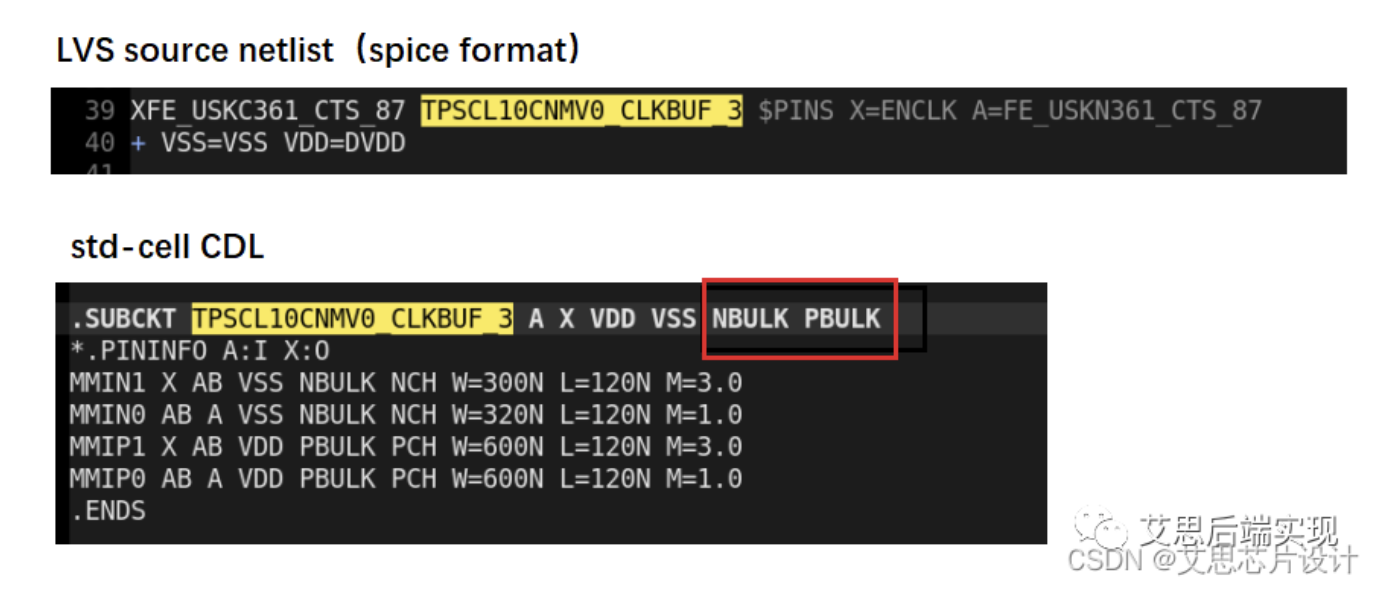

通常的LVS里边的source netlist是来自于APR工具,APR对于PG netlist的抽取,又是依赖于UPF和LEF的,所以综上,用户会遇到一种情形,LVS PG netlist对std-cell的描述会和最终的std-cell CDL出现分歧:source nelist的std-cell会缺失bulk连接声明,

很明显,同样的cell在LVS的source netlist缺失了bulk的连接,这样的LVS的比对,会发生大面积的std-cell port mismatch error,是无法进行的

v2lvs的高阶用法

但是这个问题看起来有一些奇怪,既然LEF里边没有声明bulk,同时在none-bias的flow下,bulk也无法被引用,这样的LVS是不是就走到死胡同了吗?当然不是,这里还是要回归问题本真。

std-cell的bulk仅仅是需要一个连接声明,具体说来就是两类

-

P-sub的bulk连接到VSS上

-

NWell的bulk连接到VDD上

这个需要在LVS的source netlist处理一下就好(当然APR是没有这个魔法的)。

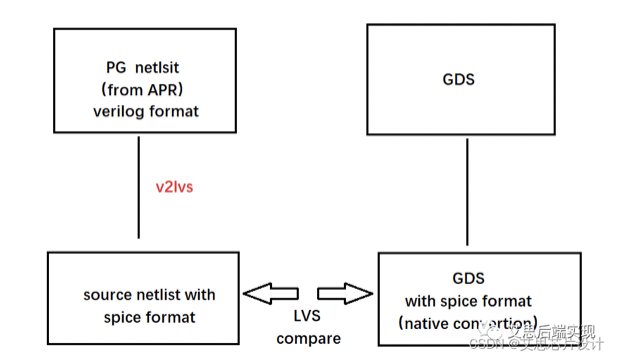

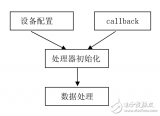

LVS的source netlist 通常是从APR的PG netlist得到的,但是由于LVS是基于spiec比对的,所以一个简单示意如下:

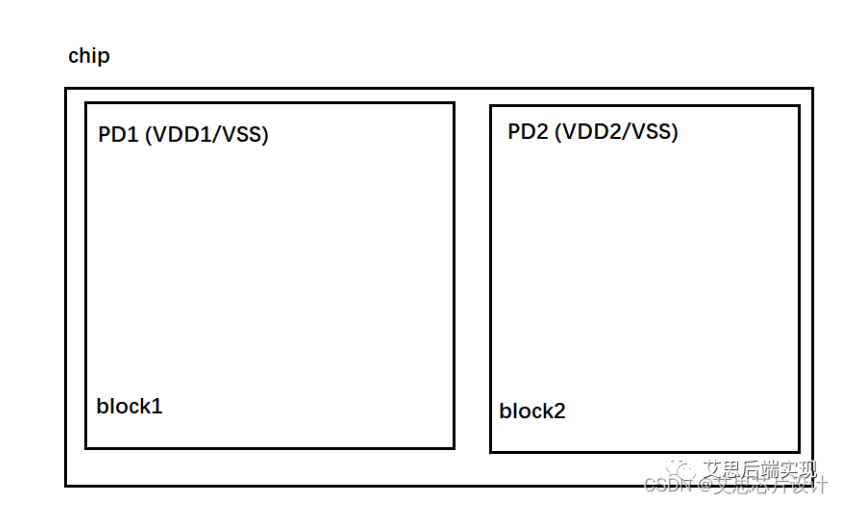

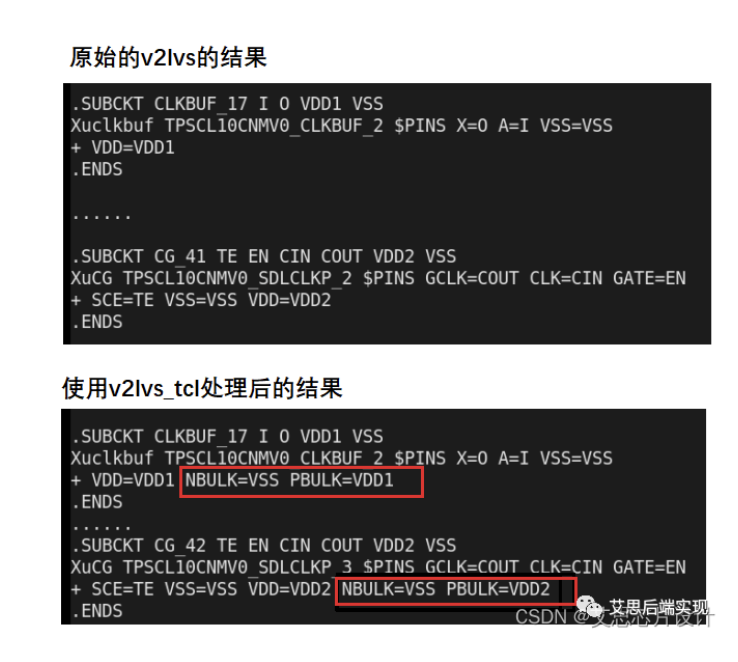

通常而言v2lvs就是简单的把verilog 转换成spice格式,但是bulk的处理需要一些高级的用法,尤其是当设计中使用了多个power domain的时候,譬如下面这个示例:

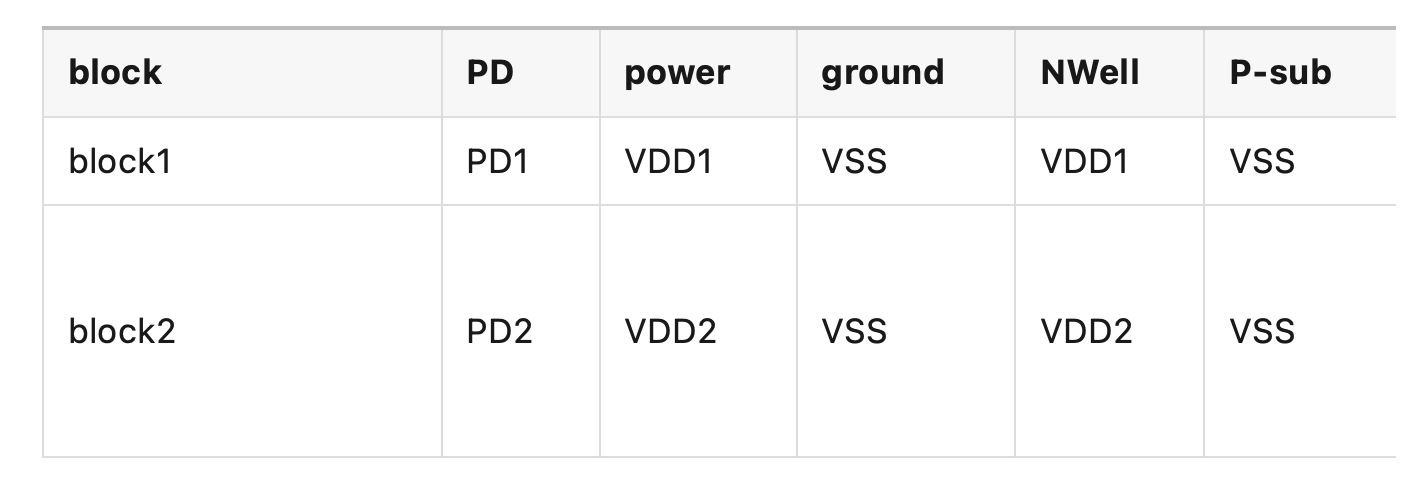

所以,对于处于不同层次/block的std-cell的PG连接就会不太一样,类似的bulk连接也会不一样,具体描述如下表

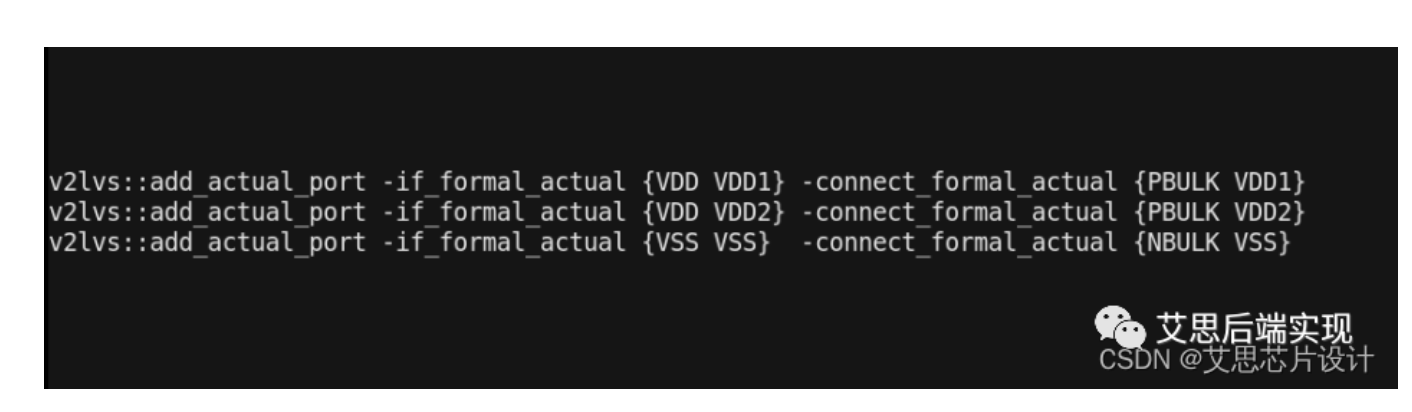

这种情形需要使用v2lvs的tcl模式进行细化处理,才能很好的将处于不同block的std-cell的 bulk连接处理完美

上述命令可以在基于当前std-cell 的PG连接关系,衍生出对应的bulk的连接,会变成下面的情形:

这样处理以后,LVS的std-cell的port mismatch也就完美解决了,

【敲黑板划重点】

v2lvs插上TCL的翅膀,在复杂的netlist也可以处理的游刃有余,再也不用写一堆perl脚本去patch netlist。流程看起来也会更正规也提高了流畅性。

-

CMOS

+关注

关注

58文章

5723浏览量

235639 -

LVS

+关注

关注

1文章

36浏览量

9955 -

VDD

+关注

关注

1文章

312浏览量

33268 -

VSS

+关注

关注

1文章

35浏览量

21450 -

NMOS管

+关注

关注

2文章

121浏览量

5466

发布评论请先 登录

相关推荐

实现有效且高效的LVS调试案例解析

让你彻底理解DFT

Mentor工具简介Calibre物理验证系列

PDK 验证软件PQLab的优势和技术指标

非规则矩形电阻在Calibre LVS中阻值提取

华大电子设计流程采用Calibre物理验证工具

用Hercules完成物理验证的详细流程

Quartz DRC和Quartz LVS:最快速的全线性物

LVS盒处理可帮助设计师迅速完成出色设计

新思科技推出最新IC Validator物理验证解决方案

DS75LVS+ DS75LVS+ - (Maxim Integrated) - 温度传感器 - 模拟和数字输出

Cadence Virtuoso设计的一个反相器LVS验证案例

物理验证LVS对bulk(体)的理解和处理技巧

物理验证LVS对bulk(体)的理解和处理技巧

评论