**IBIS **模型简介

IBIS(Input/Output Buffer Informational Specifation)是用来描述 IC 器件的输入、输出行为特性的文件。在IBIS模型里包含的核心内容就是在给定负载情况下得到的几条I/V和V/T曲线,有了这几条曲线就可以描述buffer的行为特性。这就需要我们注意, IBIS 模型并不提供 IC 器件的功能信息、逻辑信息、输入到输出的时间延迟等信息。也就是说,IBIS 模型只是提供了I/O Buffer 的行为特性。所以对于器件商家而言 IBIS模型不会泄漏器件的内部逻辑电路的结构。仿真的时候把相应的buffer添加到PCB板上电路的驱动端和接收端就可以进行 SI、串扰、EMC 以及时序的仿真分析。IBIS 模型可以通过实际的测量得出也可以通过器件的 SPICE模型转换得到。由于它是一个行为级模型不包括IC内部的电路信息,因此在仿真速度方面比相应的Spice 的晶体管级模型要快 10~15 倍左右。

IBIS 模型是基于器件的。也就是说一个 IBIS 模型是对于整个器件的管脚而言的,而不是几个特殊的输入、输出或者是 I/O 管脚的 Buffer。因此,IBIS 模型中除了一些器件 Buffer 的电气特性,还包括 pin-buffer 的映射关系(除了电源、地和没有连接的管脚外,每个管脚都有一个特定的 Buffer),以及器件的封装参数。还包括一些电气说明如 Vinh、Vinl、Vmeas以及管脚的寄生参数(如管脚的引线 R、L、C)等。同时IBIS 有其特定的语法和书写格式,模型中各个字段、各种信息都需要按照其语法格式进行书写。

一般情况,IBIS 模型包含以下一些信息,IBIS 模型的结构如下图 1.1 所示。

1.关于文件本身和器件名字的信息。这些信息用以下的关键词描述: [IBIS Ver] IBIS的版本号, [File Name]文件的名称, [File Rev]文件的版本号, [Component]器件的名称和[Manufacturer]。器件的制造商。

2.关于器件的封装电气特性描述(寄生RLC),可以使用关键词 [Package]和[Pin]描述。

3.为了表述器件管脚的Buffer所需要的相关的数据信息。关键词 [Model] 是用来表示每个Buffer的数据,具体的内容有:Model_type(Buffer的类型)、Vinh、Vinl以及C_comp(IC芯片的电容)。在前面的内容中提到了Buffer的特性描述,在IBIS模型中需要下面的一些关键词描述:[Pull-up]、[Pull-down]、[GND clamp]、[Power clamp]和 [Ramp]。当然对于不同的Buffer可能不需要上面的全部的关键词来描述。如OC和漏极开路电路就不需要[Pull-up]关键词的数据信息。

下面就图 1.1的内容作一个说明。在图的右半部分的内容有[…]的是 IBIS 模型中的关键词;没有方括号的条目则代表的是子参数的标题。同时对于红颜色的字符“Y”标明在 IBIS 模型中是必选项;而“N”则是表明该内容在 IBIS 模型中为任选项。

IBIS 提供两条完整的 V-I 曲线分别代表驱动器为高电平和低电平状态,以及在确定的转换速度下状态转换的曲线。V-I 曲线的作用在于为 IBIS 提供保护二极管、TTL 推拉驱动源和射极跟随输出等非线性效应的建模能力。

一般而言,IC 器件的输入、输出和 I/O 管脚的 Buffer 的行为特性是通过一定的形式描述的。下面分别对于输入、输出和 I/O 管脚 Buffer 的表述形式作一个介绍。

对于一个 I/O(3-stateable)Buffer 需要 4 个 I/V 曲线来表征其特性。其相应的 4 个关键字分别是:

[Pullup]:在输出为逻辑低时,输出管脚 Buffer 的 I/V 特性;

[Pulldown]:在输出为逻辑高时,输出管脚 Buffer 的 I/V 特性;

[POWER Clamp]、[GND Clamp]:在输出的电平强制在 Vcc以上和 GND 以下时,输出管脚 Buffer 的I/V 特性。此外,还需要Buffer 由一个状态转换为另一个状态的转换时间,以及Buffer 的输出电容。

对于输出 Buffer 只需要 2 套数据曲线就可以了。一个是 Pullup 曲线;另一个就是 Pulldown 曲线。两个曲线的定义和前面的内容是一致的。因为输出管脚没有 3 态的模式,所以电源和地钳位二极管的两个曲线就不需要晶体管的曲线区分了。

对于漏极开路或者是集电极开路的器件需要 3 个 I/V 曲线就可以了。3 个曲线分别是: [Pulldown]曲线、 [GND Clamp]以及[POWER Clamp]曲线。

输入 Buffer 的数据。当我们测量输入 Buffer 的数据时,我们可以使用同输出或者 I/O Buffer 的方法。当然我们必须将电压源放置在输入端。对于输入 Buffer 只需要[POWER Clamp]和[GND Clamp]的 I/V 数据。此外还需要Buffer 的输入电容。

对于上述的V-I、V-T曲线对应下图所示typ、min、max三种模式,在IBIS模型中对三种情况的定义如下:

IBIS模型使用

我们从IBIS模型中能够获得哪些信息

作为信号完整性工程师我们使用IBIS模型通常是用来做信号质量仿真,并以仿真结果为依据来判断互连设计是否满足要求。其实我们通过IBIS模型中还可以获得很大对设计有用的信息。

从IBIS模型中可以获得信号上升时间信息

IBIS模型中的关键字[Ramp]定义了buffer输出的上升下降沿的斜率。如下为micron的DDR3芯片的DQ_34_1600的[Ramp]语句。用 dv_r表示将R_load 接地情况下,逻辑电平状态(由低到高)转换的 20%到 80%的摆幅大小。

由DDR3 的IO电压为1.5V可以计算出信号的上升下降时间为330ps左右(20%到 80%的上升时间为200ps这里为了仿真方便使用330ps)。由经验法则“当信号传输延时小于信号上升时间1/6时,互连线处在集总区域,不会体现出传输线效应。”可知,当信号传输延时小于55ps时,传输链路不会体现出传输线特性。也就是说如果当信号线的延时小于55ps的时候我们可以考虑采用直连的形式,而不需要使用任何匹配。

在ADS中搭建仿真电路对其进行验证。仿真电路中包含以下几部分:信号源内阻17ohm、负载阻抗为10Kohm和传输线阻抗并不匹配;信号源信号上升下降时间均为330ps、频率800MHz输出码型“101010”;TLD1为延时可调的传输线。

将TLD1的delay分别设置为55ps(1/6上升时间)、165ps(1/2上升时间)、330ps(上升时间)进行仿真对比,负载端接收的波形如下:

如上所示红色实线为互连线延时为55ps的仿真结果,过冲只有170mV左右,而且振铃也很小信号质量没有明显恶化;蓝色点线为互连线延时为1/2上升时间的仿真结果,可以看出此时信号的过冲达到了最大值幅度超过了600mV;粉色短划线为互连线延时等于上升时间的仿真结果,此时不光过冲达到了最大值,而且过冲的宽度也有2倍的上升时间的宽度。

一个经验丰富的信号完整性工程师通过IBIS模型中读取了信号上升时间,并根据PCB布局情况估算布线延时就能够大体得知接收端信号应该有什么样的特征,以及信号是否需要匹配。

确定buffer的输出阻抗

由上一节的介绍我们能够从IBIS模型中得到输出buffer的上升时间,那么如果预估的布线延时超过了1/6的上升时间我们就需要通过增加匹配的方式来解决信号完整性问题。最简单的匹配方式就是源端的串联匹配,但如何确定最优的串联电阻值呢。我们也可以从IBIS模型中得到输出buffer的驱动能力,即buffer的输出阻抗Zout,由于通常情况下传输线阻抗Zo控制在50ohm。那么就可以计算得到串联匹配电阻值Rseries = Zo-Zout。下面我们来看如何得到驱动器的输出阻抗Zout。

IBIS模型中的pulldown和pullup曲线分别为输出buffer的下管和上管的工作曲线。而数字电路只是简单地工作在晶体管的饱和区或者可变电阻区。由模拟电路的知识我们可以画出晶体管的直流负载线就可以找到操作点的电流电压值,由此计算出输出阻抗Zout。下面以pulldown曲线为例说明输出阻抗Zout的求解过程。

一般情况IBIS模型中的每一条曲线都会对应typ、min、max三种情况,分别代表了不同的电压、温度下晶体管表现出的不同特性。负载线由50ohm上拉到Vgs,对于micron DDR3的IBIS模型的DQ_34_1600 buffer的typ模式Vgs=Vddq=1.5V,由此可以确定直流负载线和两个坐标轴的交点(0V,30mA)、(1.5V,0A)。这样就能画出typ模式的直流负载线,进而得到操作点的电压和电流,计算得到Zout=600/17.8=23.7ohm。这个计算结果和DDR3手册中的34ohm非常接近,由此可知这种方式计算输出buffer的输出阻抗是完全正确的。如此我们就可以不通过仿真估算出需要添加的匹配电阻值。

最优的Rseries = 50-33.7 = 16.3ohm。在hyperlynx中搭建仿真电路进行仿真验证,由于我们只是通过pulldown曲线来计算输出阻抗,下面的仿真也只仿真一个下降沿。

如上所示的仿真结果来看信号基本没有下冲,这就说明阻抗匹配已经做的很好了。细心的读者可能会想到,当我们增加了16.3ohm的 之后,晶体管的直流负载线已经发生了变化因为到VDDQ的电阻已经由50ohm变为了50+16.3=66.3ohm了,对于在一些饱和区线性度比较高的晶体管这个影响并不是很大,而对于一些在饱和区电阻变化很快的晶体管就会导致匹配的不理想存在下冲和过冲。

我们也可以通过另一种更加简便的方法来得到输出阻抗Zout。源端阻抗匹配的目的就是要让驱动器输出阻抗Zout加上源端串阻Rseries得到的等效输出阻抗和传输线阻抗匹配。我们可以反过来思考当驱动器等效输出阻抗等于传输线阻抗时,驱动器阻抗和传输线阻抗之间由于分压使进入传输线的入射电压Vinc=Vddq/2,那么通过传输线Zo的电流为

对于上面的例子而言VDDQ=1.5V,Zo=50ohm,计算得到Iinc = 15mA。

由此,我们可以直接在pulldown曲线中找到15mA对应的电压500mV,计算得到Zout = 500/15 = 33.3ohm,进而求得最佳的Rseries = 16.7ohm。

可以使用同样的方法对pullup曲线进行分析得到上管的输出阻抗,然后可以根据上下管的输出阻抗得到串阻的范围,只需要在这个范围内选择一个

就可以获得最好的匹配效果。

确定各个管脚的封装延时

IBIS模型中可能会包含三种形式的封装信息,分别在[package] [pin] [package model]三个字段定义。下面来说明一下这三个字段的含义和区别。

首先来看[package]字段,它是定义关于R_pkg,L_pkg, C_pkg参数的一个字段,这里定义的参数是一个笼统的数,为什么说它是笼统的呢,是因为它只有一组数就把器件所有的PIN脚都包括了。

显然这种方式无法描述封装内不同管脚之间的寄生参数的差异性,在速率不是很高的情况下这种参数模型仿真得到的信号质量可能和实际偏差不大,但是仿真结果不能表示封装对信号时序的影响,同样随着信号速率的不断提高如DDR3等接口的仿真如果想得到准确的信号质量和时序结果不能仅仅依靠[package]字段的参数。一般大的IC厂家都不会只弄这么一组数据,还会在[pin]字段里描述了每个PIN脚的package参数,同时与管脚的编号、管脚的信号名称、管脚的模型名称相对应,如下所示:

[pin]字段和[package]字段一样,仅仅用一阶的RLC电路来描述整个package的特性,可能在频率不太高的情况下可以做个参考,但是到了高频后这显然是不够的,PIN与PIN之间的耦合信息是没有的。最理想的做法是用3D全波电磁场建模解决问题,但这种想法并不现实package的3D模型不是每个厂家都能提供的。但是我们已经可以从[pin]字段的L_pin、C_pin中得到每个pin在封装内的延时信息:

这样我们就可以通过PCB的布线控制来补偿芯片封装内部的延时偏差,高速总线的时序设计将能够得到最大限度的保障。

IBIS5.0版本又引入了[package model]字段,让手头仅有的资源发挥出最大的作用。[package model]字段内容可以出现在.ibs文件里,也可以出现在一个单独的以.PKG为后缀名的文件里。先看一下它的整体结构:

接下来3个字段[Manufacturer],[OEM],[Description]属于描述性质的,大家完全可以忽略,对仿真没有什么影响。

[Number Of Pins],这个看字面意思应该也能理解了,就是器件的引脚个数。[Pin Numbers]字段中列出了封装中所有pin的编号。

接下来的[Model Data]将是[package model]的核心内容,包含了[Resistance Matrix],[Inductance Matrix],[Capacitance Matrix],翻译过来就是电阻矩阵,电感矩阵和电容矩阵。后面有Banded_matrix,Sparse_matrix等关键字,分别表示为一维矩阵,多维矩阵。一维矩阵的情况就和[pin]字段中定义的R_pin、L_pin、C_pin效果一样并不包含pin和pin之间存在的耦合信息,多维矩阵则包含了pin和pin之间的耦合信息不仅能够进行信号质量仿真也可以进行串扰仿真。

通过上面的分析可知,我们可以在[pin]、[package model]字段中获得每个管脚封装内部的延时信息,获得这一延时对我们来说有着怎样的意义呢?

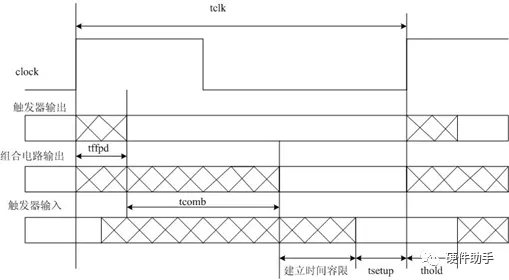

首先,我们知道互连线延时超过信号上升时间延时1/6时互连线就会表现出传输线效应。我们已经了解匹配电阻的布局必须足够靠近驱动器才能和驱动器的输出电阻看成是集总电路,才能获得最好的匹配效果。由[ramp]参数可以读出驱动器的上升下降时间,我们可以用1/6信号上升时间减去封装内部的延时作为封装管脚到匹配电阻的PCB布线延时的约束。

第二,由于我们在进行信号质量测试时只能在靠近输入管脚的封装处选择测试点。而对于一个输入管脚如果封装延时很大,我们在封装处测试得到的信号波形和芯片DIE实际接收到的波形将会存在很大的差异。

在ADS中搭建仿真电路,有8.6nH的电感和2.25pF的电容来模拟封装参数,仿真来观测Vpkg和Vdie两点的电压波形差异。

计算得到封装延时,

此时的仿真结果如下图所示(红色实线为die内接收波形,蓝色短划线为封装处的测试波形)

如上所示,两个波形存在比较明显的差异。封装处的测试波形在上升和下降沿都存在100ps左右的回沟,而且边沿要比die内测试到的波形要缓,幅度要比die内信号波形低。这一现象可以用反射的理论来解释,在封装处测试的波形实际上是由发送端的入射波和接收端反射产生的反射波的叠加产生,由于封装参数的存在导致入射波和反射波之间有一定的延时,在叠加的时候就导致回沟或者台阶的出现。

如此我们可以试着减小封装参数来看是否回购有效减小或者消失。将封装参数更改为电感6.01nH、电容1.52pF,计算得到封装延时

此时的仿真结果如下图所示(红色实线为die内接收波形,蓝色短划线为封装处的测试波形)

如上所示,两个波形之间的差异已经很小。封装处的测试波形在上升下降沿的回沟都消失了,只是边沿要比die内测试到的波形要缓一点,幅度要比die内信号波形低。

-

二极管

+关注

关注

147文章

9624浏览量

166261 -

驱动器

+关注

关注

52文章

8208浏览量

146227 -

PCB板

+关注

关注

27文章

1445浏览量

51603 -

IBIS

+关注

关注

1文章

53浏览量

19882 -

GND

+关注

关注

2文章

539浏览量

38694

发布评论请先 登录

相关推荐

基于信号完整性分析的高速数字PCB的设计方法

Altium Designer中进行信号完整性分析

基于信号完整性分析的高速数字PCB板的设计开发

用IBIS模型对高速PCB进行信号完整性分析,出现报错显示没有有效的连接器插针模型

如何利用IBIS模型研究信号完整性问题?

利用IBIS模型研究信号完整性问题

信号完整性计算和器件的特性阻抗研究

基于IBIS模型的信号完整性分析

如何使用IBIS模型用于信号完整性计算和确定PCB设计解决方案的概述

如何使用IBIS模型来确定PCB板的信号完整性问题

基于信号完整性的高速PCB设计

信号完整性之IBIS模型简介

信号完整性之IBIS模型简介

评论