Peter Delos, Michael Jones, 和 Hal Owens

本文详细介绍了 16 通道 S 波段直接采样接收器设计的性能测量与预测。该设计基于最近 发布直接采样模数转换器(ADC),时钟频率为 4 GSPS和转换器第二奈奎斯特区的采样。这 首先使用指向在线参考的指针来描述设计配置 提供进一步的描述。接下来,显示两个RF的接收器 嵌入式数字信号处理的组件和配置 (DSP),现已集成到现代数据转换器中。计算 呈现和比较单通道性能预测 反对测量。了解单通道性能后, 一组测量结合了来自 16 个通道的数据,评估 噪声密度、杂散信号和互调产物的动态范围改进。本文最后提出了一组观察结果 可用于外推的多通道性能趋势 使用许多分布式接收器实现的大型相控阵模型。

介绍

ADC采样速率的提高目前支持直接采样RF系统: S波段及以上。ADC技术的进步使数字波束成形相控阵得以普及。随着这些进步,工业界 问题仍然存在于直接的单通道性能能力 采样接收器以及动态范围改进可能 许多直接采样接收器分布在大型相控阵中。

尽管两家半导体公司都付出了巨大的行业努力 开发最新的数据转换器和大型公司系统集成商 改进相控阵架构,但公布的数据仍然有限 量化高通道数可实现的性能改进 直接采样接收器系统,可连贯地组合来自多个数据 分布式接收器。

我们的目的是帮助系统工程师提供可量化的测量 可用于通知自己的大型相控阵模型。我们的数据收集是 创建更多时仅要考虑一组基本测量值 复杂的相控阵系统模型。

评估的接收器设计

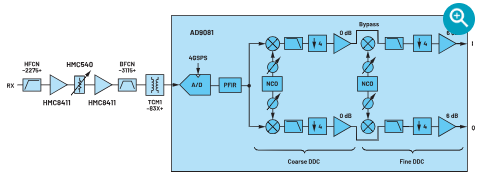

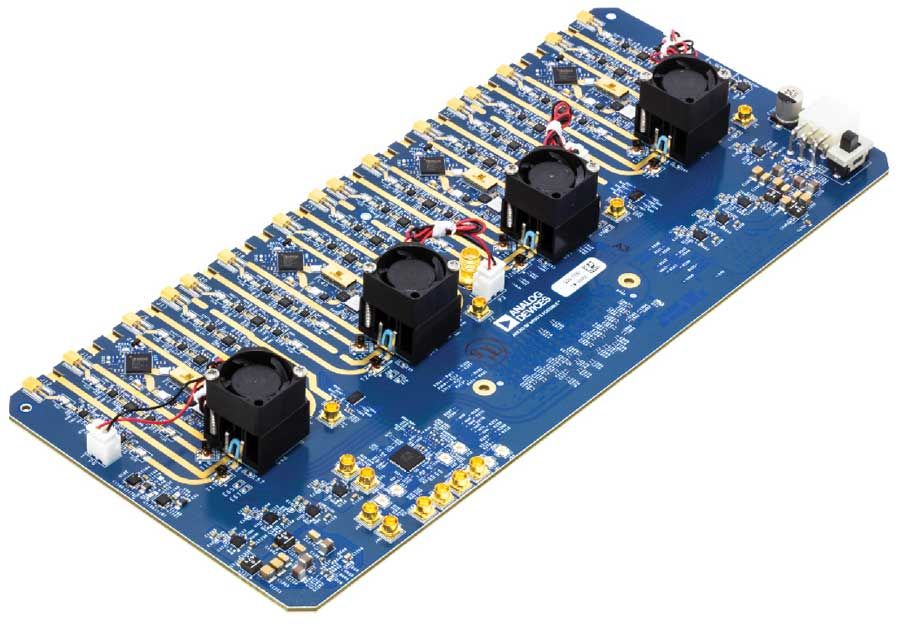

开发了16通道直接S波段射频(RF)采样平台 评估多通道环境中最新的高速数据转换器。1该平台(见图1)包含四个AD9081混合信号前端(MxFE) 集成电路 (IC)。每个AD9081包含四个RF数模转换器 (DAC) 和 16 个射频 ADC,总共提供 16 个射频发射和 <> 个射频接收 渠道。四 MxFE 平台产品页面提供了详细说明 的平台以及使用的软件。®

图1.四通道 MxFE 16 通道直接采样平台。

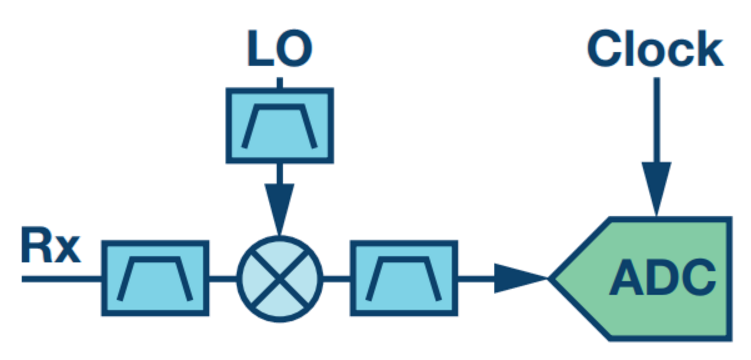

接收器设计细节如图2所示。射频组件在 接收器前端与ADC和配置一起显示 AD9081内部的嵌入式DSP。

图2.接收器框图。AD9081内部嵌入式DSP的配置以及前端RF元件如图所示。

随着现代ADC采样速率的提高,可实现直接采样接收器 架构,设计配置中的大部分考虑因素都会发生变化 从射频域到嵌入式DSP。请注意,射频链非常简单: 有几个放大器用于增益,增益控制功能使用数字 受控衰减器和用于抗混叠目的的滤波器。嵌入式数字信号处理器 但是,与配置相比,具有更多的可编程属性 使用上一代数据转换器的接收器设计。这种趋势 未来的数据转换器将继续增加嵌入式处理。 因此,接收器设计人员有必要了解 在嵌入式处理中选择的选项的含义 立场。首先是要了解ADC数据预处理相对于 系统期望。其次,可能更重要的是优化 使用数据转换器内部的嵌入式DSP来卸载以前在现场可编程门阵列(FPGA)结构中完成的处理,从而减轻 优化系统处理电源效率

基于这一趋势,有必要描述DSP配置 将任何测量值与计算的预测值进行比较时。数据集 本文介绍将AD9081 ADC配置为4 GSPS采样。这 ADC之后是可编程有限脉冲响应(pFIR)滤波器,用于 均衡频带上的幅度和相位。其次是粗略的 数字下变频器(DDC),其中有数控振荡器 (NCO) 配置在感兴趣的波段中心和 4 分位数块中 被利用。精细的 DDC 配置为绕过 NCO,以及额外的 使用4分程和6 dB数字增益。其结果 配置为总抽取值16,数据速率为250 MSPS,数字频率为0 dB 增益,并在粗略的NCO中选择单个非零NCO频率设置 乐队中心。

通过应用程序编程启用组件配置 接口(API)可从AD9081产品页面获得。摘要 表 1 显示了本文中使用的相关主要接收器 API 函数。

| 接口函数调用 | 位域 | 注册 | 价值 |

| adi_ad9081_adc_ddc_ coarse_nco_mode_set(..., ..., AD9081_ADC_NCO_VIF | 粗_ MXR_IF | 0x282<7.6> | 0x00 |

| adi_ad9081_adc_ddc_fine_nco_mode_ 设置(..., ..., AD9081_ADC_NCO_ZIF) | FINE_MXR_IF | 0x283<7.6> | 0x01 |

| adi_ad9081_adc_ddc_coarse_gain_ 设置(..., ..., 0) | COARSE_GAIN | 0x282<5> | 0x0 |

| adi_ad9081_adc_ddc_fine_gain_set(..., ..., 1) | FINE_GAIN | 0x283<5> | 0x1 |

单通道性能测量 与计算预测相比

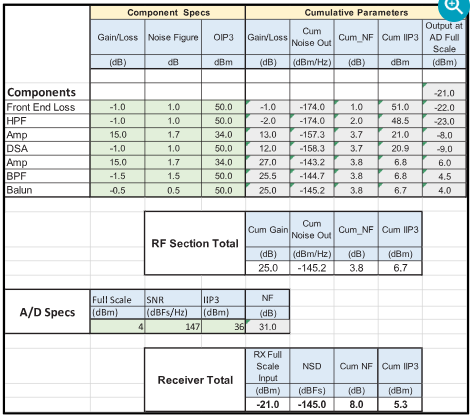

接收器性能的电子表格计算如图3所示。 该分析保持简单,仅包括主要接收器的增益项, 噪声和三阶截距。图中显示了噪声系数和噪声功率的噪声。首先,显示了RF组件的级联分析。这是添加的 接下来是ADC性能。包含两者的级联计算的详细信息 RF元件和ADC包含在“宽带接收器综述”中 架构选项。2最后,性能反射回接收器RF 连接器输入并在图 3 底部进行了总结。

图3.接收机性能计算:首先显示RF级联。然后将RF性能添加到ADC性能中,以进行完整的接收器性能预测。然后,性能被反馈回接收器连接器输入,直接在RF输入端代表有效的ADC。

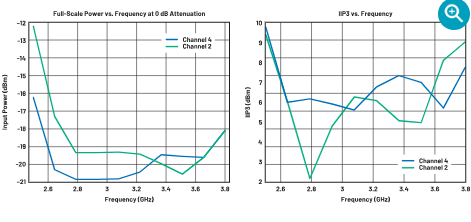

测量满量程输入功率和输入三阶截点 点 (IIP3) 如图 4 所示。从左侧开始,使用满量程输入 功率,图 3 中的预测估计值为 –21 dBm,而测量值为 图4的标称值为-20 dBm±频带中心为1 dB。在 带边是由于抗混叠滤波器,实际上滤波器形状可以是 从这个数据中看到。一两个dB内的增益匹配被认为是合理的,因为 电子表格中可能未考虑额外的dB左右的损失。在 将图 3 右侧的 IIP4 数据与图 3 中的预测进行比较, 我们看到IIP3比预测的略好约1 dB,其中 通道 2 在 2.8 GHz 时的骤降除外。IIP3数据也被视为 相当接近级联预测。

图4.针对满量程功率和输入IP3的单通道测量。测量结果根据接收器RF连接器输入进行校准。

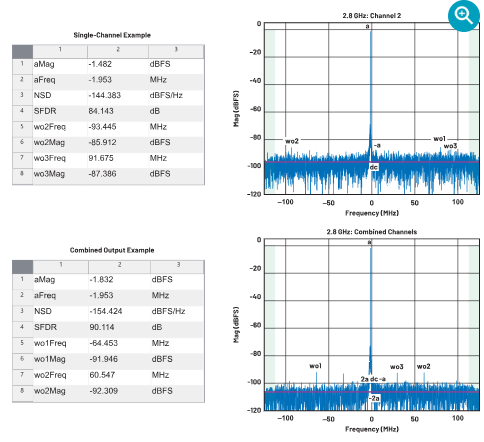

接下来,有必要描述快速傅里叶变换(FFT)分析。 我们描述中提供的所有数据均基于 FFT 和处理以产生 来自FFT数据的测量。图 5 显示了示例 FFT。顶部 图用于单个通道,而底部图用于组合和 校准通道。

图5.FFT 测量示例。

使用图5中的单通道FFT,我们可以将噪声密度与 图 3 中的预测。图3中的级联计算估计了噪声 当RF部分与ADC级联时,密度为–145 dBFS/Hz。图5的单通道测量结果为–144.3 dBFS/Hz,因此级联 计算似乎再次与测量值紧密对齐。

对于图5底部的组合FFT,执行校准 如“DAC/ADC IC上的集成硬化DSP改善宽带”中所述 多通道系统“和”使用多芯片的上电相位确定性” 集成宽带DAC和ADC的同步特性”3,4并对数据求和。然后调整满量程以适应组合数据的位增长,最后执行相同的FFT。通过这种方法, 满量程组合电平接近平均通道电平和 动态范围有所改善,由于组合增益,接下来将看到。

单通道与组合通道 接收器测量

噪声密度和杂散信号

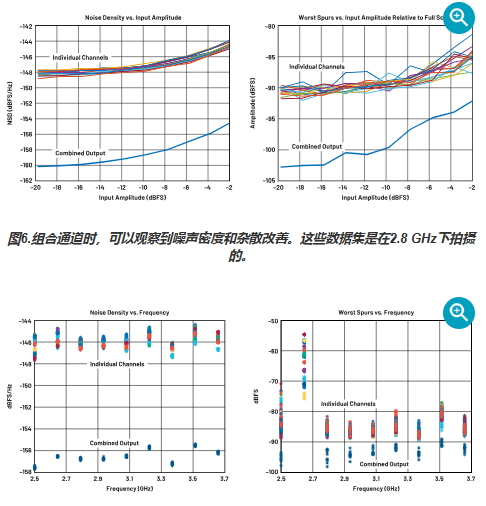

我们想研究组合时的噪声和杂散改善 渠道。同样感兴趣的是观察组合通道影响与输入 功率电平和频率。结果如图6和图7所示。

图7.单通道和组合通道噪声密度以及杂散与频率的关系:在每个频率上捕获十次。图上的每个点代表一个FFT。

从图6左侧开始,噪声密度与输入的影响 可以观察到功率。在低功率水平下,10log(N) 的 12 dB 改进为 在系统中实现 N = 16 个通道。随着功率的增加,请注意 组合输出噪声密度的增加速度略快于低于 各个频道。这是跨 渠道。在这些数据集的情况下,退化仅为大约 1 dB,因此在组合通道时仍有显着改善。这 相关源被认为是锁相环 (PLL) 在单个AD9081或可能的RF输入源中与四个通道共用 使用。自 10 dB 改进以来,没有进行进一步调查 测量仍然相当重要。

图6的右侧详细介绍了系统的杂散性能。 在以下情况下,杂散性能也有显著改善 组合通道,表示杂散在通道之间不相关。 刺激改善是一个相当积极的结果。在这些数据捕获期间, 已经花费了大量精力来评估特定频率的特定杂散 补偿。一个意想不到的观察结果是,马刺看起来相当随机。 单通道中最差的杂散在各个通道之间并不相同,并且确实 在组合数据中不显示为最差的杂散,除了特定的 二次谐波情况如图7所示。有两种解释 马刺的随机性。首先,起点相当不错,因为 如图 5 的 FFT 所示。次要影响是测试设置对所有16个通道的数据采集大小以及这些通道的FFT长度有限 捕获所有 4096 个通道时,数据捕获限制为 16 个点。在 尽管数据捕获长度很长,但仍能观察到<90 dBc的杂散。 未来的多通道测试平台将寻求延长FFT长度。

图 7 显示了类似的单通道和组合通道性能与 频率。对于这些数据集,每个频率捕获了 10 次。每 图上的点表示单个 FFT。这些数据的功率电平为 标称值为 –5 dBFS。

图7左侧的噪声密度数据显示,各个通道 与图3中所有通道和所有通道的估计值相当一致 频率。综合数据显示,相当一致的改进 目标频率两端的 ~11 dB,与图 6 一致 相关功率级别。

图7右侧的杂散也显示出相当一致的组合通道改进。位于2.65 GHz的杂散值得评论。 在此频率下,有第二个谐波落在带内并导致 单通道杂散需要提升。此频率点包含在数据中 因为它与评估折叠谐波引起的杂散影响有关 当通道组合时。有两个有趣的观察结果。这 首先是马刺看起来不相关,其次是存在一个 跨通道的杂散电平范围广。这是一个积极的结果,似乎 表明组合输出仍然可以接近 10log(N) 改进 超越最糟糕的渠道支线。它还表明,通过改进布局 设计上,通道层面的杂散可能会得到改进。我们做到了 不再进一步调查,但指出此处要记录的观察结果 结果。

幅度和相位稳定性

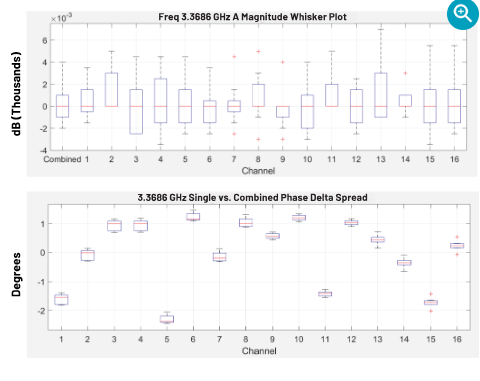

图7中的数据有助于评估幅度和相位稳定性 因为每个频率都获取多个数据集。结果显示 在图 8 的晶须或 MATLAB 箱形图中。®

图8.幅度和相位稳定性测量:图7中采集的数据的晶须图。数据集由 10 个捕获组成,名义上超过 5 秒。上图中的幅度稳定性显示一致性在千分之一dB以内。下图中的相位稳定性显示了十分之一度内的相位稳定性。

选择 MATLAB 箱线图是因为可用数据量有限。箱须图是旨在提供快速数据集的图形 分发信息。盒须有五个主要组成部分 情节。红线表示数据集的中位数,而蓝色表示 围绕红线的框表示 数据。此范围称为四分位距 (IQR)。该框包含 数据集的 50%。框上方和下方是代表 视为数据集的最大值和最小值。任何谎言的数据点 超出 1.5 × IQR(第一个四分位数到第三个四分位数 + 1.5 IQR)的范围是 被视为异常值,由单个红十字数据点表示。 在图8的幅度稳定性图中,比较了所有幅度 通道和组合输出。对于相位稳定性,单相 将通道与组合输出端的相位进行比较。这是 必需,因为在此测试设置中数据捕获是异步的。是的 有趣的是,时钟分布可以从 相位稳定性数据。请注意相位稳定性数据中盒子的形状如何以四个为一组匹配:通道 1-4、5-8、9-12 和 13-16。这些渠道 代表每个AD9081内部的四个通道,每个AD9081都有一个专用的ADF4371 PLL。在此特定集合中相位漂移匹配的观察结果 的四组表示相位稳定性由PLL主导。这 观察结果与我们最近的相位噪声分析一致。5

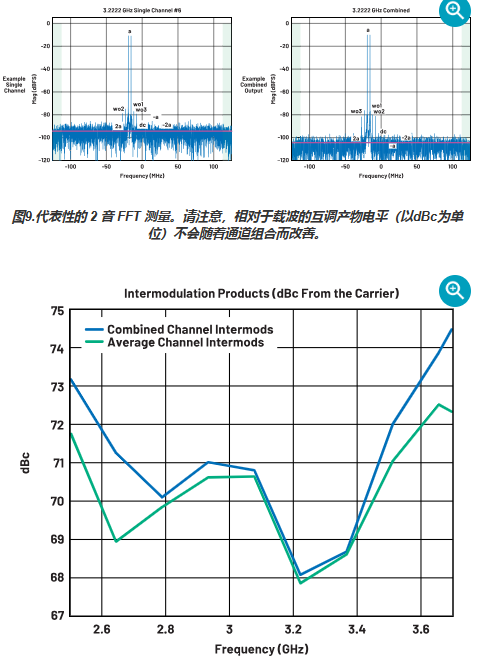

组合 2 音测量

我们的最终数据集是2音测量,用于评估通道组合时互调产物的影响。结果显示在 图 9 和图 10。

图 10.组合互调积与频率的关系:组合互调积电平接近各个通道的平均值。

结果表明,互调产物是相关的,并且它们接近 通道电平互调乘积的平均值。此结果与“使用商用收发器的数字阵列: 噪声、杂散和线性度测量。6

意见摘要

使用这套全面的测量方法,现在可以解决几个关键点 总结一下。

对于组合通道:

振幅:组合输出的振幅接近平均值。 这是一个自然的结果,因为首先要进行校准以对齐通道 振幅和相位。

噪声密度:

在低功耗下,可以实现10log(N)的改进。

当功率增加到接近满量程时,相关项可能具有 由于任何共享电路的影响。测量表明只有 1 dB 16 个通道的降级。

杂散信号:

马刺似乎比最初预期的更随机。这是一个积极的 结果并启用动态范围改进时通道 组合在一起。

最差的杂散通常可以提高10log(N)。

组合 16 通道结果显示 90 dBc 或以下的杂散信号, 这是相当不错的,再次与单通道高电平相媲美 高性能窄带接收器。

应考虑在将来的评估中使用更大的FFT长度以改进 用于杂散分析的FFT动态范围。

互调:互调产物相关,没有 预计动态范围会有所改善。这是分阶段的已知问题 阵列社区。由于与动态范围相关的其他术语随着通道的组合而得到改进,因此未来的系统和规格可能会有所改进 线性度受互调产物的限制。这一事实可能会推动 非线性校正的创新与强制方法的研究 互调产物在大型阵列中不相关。

幅度和相位稳定性:幅度一致性在千分之一以内 对于数据,观察到十分之一度以内的dB和相位一致性 捕获大约 5 秒的持续时间。我们相信阶段 这种设计的稳定性受到用作数据转换器时钟的PLL的限制 源。如果需要提高相位稳定性,可以使用备用时钟源 可以考虑。

结束语:出现16通道噪声和杂散测量 相当出色,可与过去的高性能窄带相媲美 接收机。这些数据表明,确实有可能分发许多 直接采样接收器,实现数字波束成形阵列级可编程性, 并且仍然保持传统窄带系统的高性能指标。

结论

我们的目的是总结和量化一套全面的接收器 在具有代表性的多通道环境中进行测量 该系统 工程师可以用来推断更大的相控阵模型。为此, 已经详细描述了特定的直接采样RF接收机设计, 已将测量结果与计算的性能预测进行比较, 本文介绍了单通道与组合通道噪声密度、杂散和互调性能的改进。这是我们的希望 这些数据集对于工程师评估自己的设计非常有用 在基于发布的最新数据转换器开发大型系统时 半导体行业。

审核编辑:郭婷

-

dsp

+关注

关注

553文章

7987浏览量

348745 -

转换器

+关注

关注

27文章

8694浏览量

147085 -

接收器

+关注

关注

14文章

2468浏览量

71871

发布评论请先 登录

相关推荐

回收 测量接收机 Agilent N5531S

LabVIEW用于分布式测量与控制系统

中频采样多模式数字接收机的设计与实现

C波段卫星信号接收机低噪声放大器的设计

高性能、双通道IF采样接收机

压缩采样接收机抗ADC非线性影响

用于相控阵的分布式直接采样S波段接收机的测量

用于相控阵的分布式直接采样S波段接收机的测量

评论