Jeffrey Fajutagana 和 Kiana Khey

本文详细讨论在测试无线系统期间需要考虑的重要因素,尤其是涉及时序和同步的系统级测试,还讲述了在特定的误差余量内,发射机和接收机模块之间无线传输数据时,这些因素有多重要。本文中讨论的因素将有助于开发测试用例,这些测试用例将确定功能性和非功能性规格、系统边界和漏洞,以确保构建高度可靠和同步的无线系统。

简介

无线技术的迅速发展开启了无线通信的新纪元。它几乎无处不在,对通信、医疗健康、汽车和空间探索行业等不同领域的创新发展产生了重大影响。该市场已然成熟,且正在经历一个充满活力的增长时期。2019年,其收入为14313亿美元,预计到2024年,这个数值将增长到55194亿美元,复合年增长率为31%。无线技术仍在不断发展,将会实现更高的准确性、更高的运营效率、更快的决策速度、更高的数据速率和更多成本节省,继续开辟更多的可能性。但是,随着这些器件的功能不断增加,无线系统级测试环境的复杂性也随之增大。

准确的时序和同步是保证无线系统正常工作的基本要求。这是指在给定的公差内,匹配系统中的发射机时钟和接收机时钟的过程。它们用于确保最高的数据包完整性和优化数据流,在实施无线系统测试和开发时,我们应始终重点考虑这些因素。但是,要满足这些要求是很困难的,因为时钟源会漂移,这一点广为人知。即使是几毫秒的微小漂移,也会随时间不断累积增大,导致系统丧失同步。只有在时钟完全匹配的时候,才能实现完全同步的无线系统。但实际上,这非常困难。漂移是时钟的固有特性,会导致时钟计数时间出现偏差,最终导致不同步。

同步不良的系统可能导致传输性能降低,进而降低所传输的数据的质量。此外,它还可能导致数据完整性丧失,导致操作失败,在可能影响健康、安全和人身安全的应用中,上述这些问题将非常关键。在这些应用中造成负面影响可能导致需要承担法律责任,且会丧失客户的信任。

鉴于对精确同步系统的需求如此之大,我们可以根据要求,例如精度和移动程度,使用多种同步技术。它们分别是:

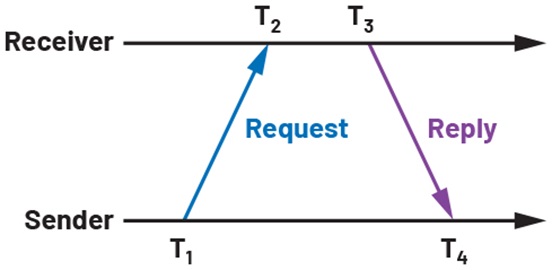

基于发射机-接收机的同步

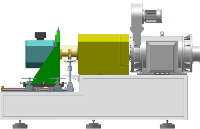

图1. 基于发射机-接收机的同步。

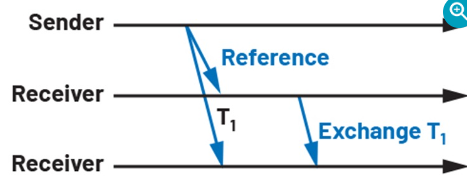

基于接收机-接收机的同步

图2. 基于接收机-接收机的同步。

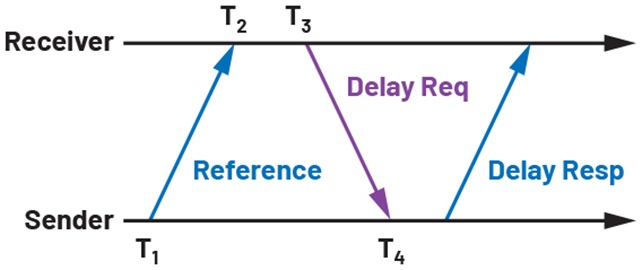

延迟测量同步

图3. 延迟测量同步。

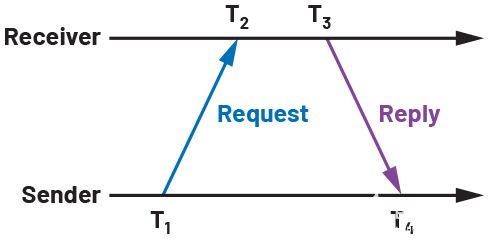

基于发射机-接收机的同步是一种双向信息交换。传感器网络的时序同步协议(TPSN)就是这样一个示例。在TPSN中,网络同步是通过在节点之间发送和接收同步脉冲数据包实现的。会用时间戳标记每次传输的时间偏移并加以计算,以确定时钟时间差,然后用于实施节点同步。

基于SFD的同步使用单向信息交换。参考广播同步(RBS)使用这种同步。

延迟测量同步和基于接收机-接收机的同步一样,也是一种单向信息交换;但是,它用于测量延迟。延迟测量时间同步(DMTS)就是这样一个示例。

接下来我们将详细讨论使用TPSN的无线系统中使用的不同的时序和同步参数,每个参数如何影响系统的整体功能,以及如何配置这些参数,确保实现更可靠的同步系统。此外,在执行无线系统级测试期间,这些参数将有助于识别与时序和同步相关的漏洞和系统边界。

时序和同步参数

同步参考

无线电让软件能够使用同步参考点来准确安排发射和接收命令。以参考点作为基准,按正偏移计划事件,在发射机和接收机之间实现同步。以下是无线系统中常用的参考点:

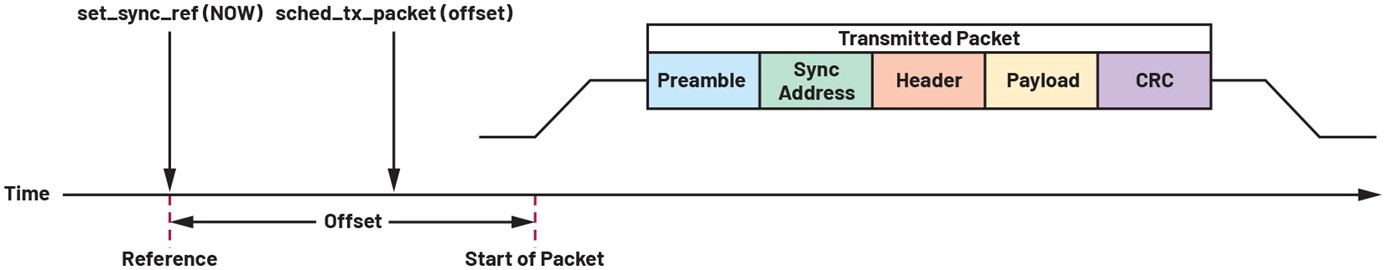

立即同步

同步参考点在处理同步命令(set_sync_ref(NOW))时置位。

图4显示被传输的数据包与被命令(set_sync_ref(NOW))设置的参考点之间的关系。

图4. 立即同步。

同步SFD

同步参考点在帧开始(SOF)时置位,表示检测到有效的同步字。

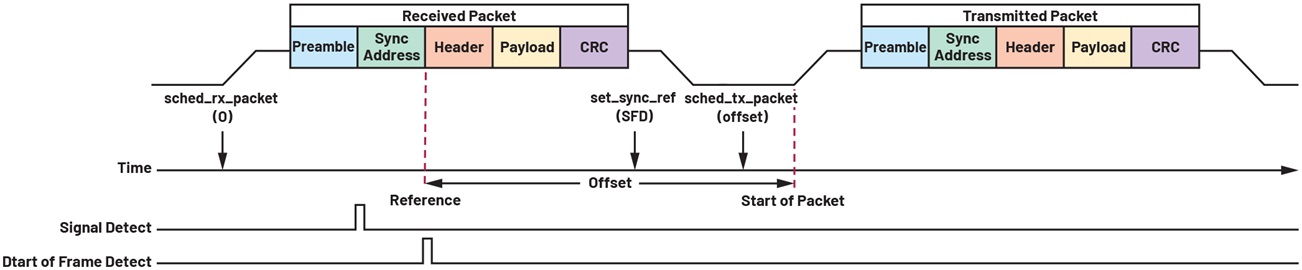

发送命令(set_sync_ref(SFD))之后,会在命令被发送之后检测到首个帧开始(SFD)时置位参考点。在图5中,第2个发射数据包是以SFD参考点为基准进行传输。

图5. 同步SFD。

同步最新

在这个同步模式下,同步参考点在每个SOF时置位。如图6所示,对于后续收到的每个有效数据包同步字,同步参考会更新到最新的SOF的时间戳时间。

图6. 同步最新。

使用这些同步模式可以在两个节点之间实现同步。但是,需要注意的是,硬件时钟以漂移而闻名,这导致其频率随时间变化,由此导致不准确。所以,在任何给定时点,时钟都可能不相同。不断更新发送和接收时钟的同步参考,最大限度地减少偏斜和偏移效应。

时间偏移

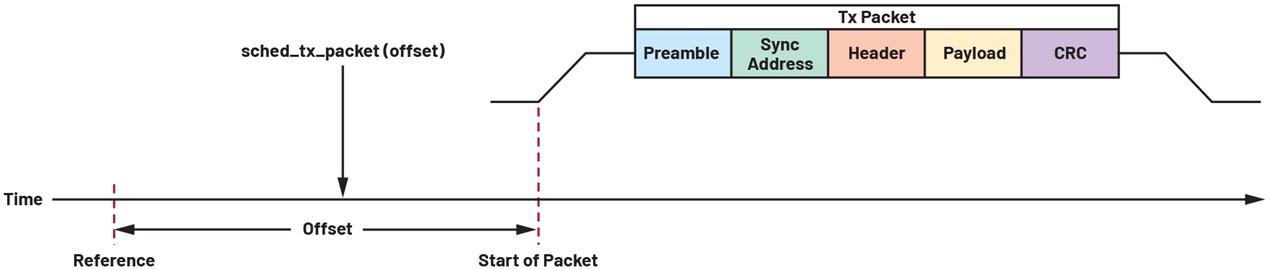

时间偏移是指当前时间与时间捕获或同步参考开始时的时间差。在发送或接收时,会使用这个参数。

最小时间偏移开始是立即执行发送/接收命令所需的最短时间。我们基于API和无线电固有的延迟来计算这个参数。如果数值比这个值更小,会导致调度错误,使得发射/接收操作失败。

图7. 时间偏移。

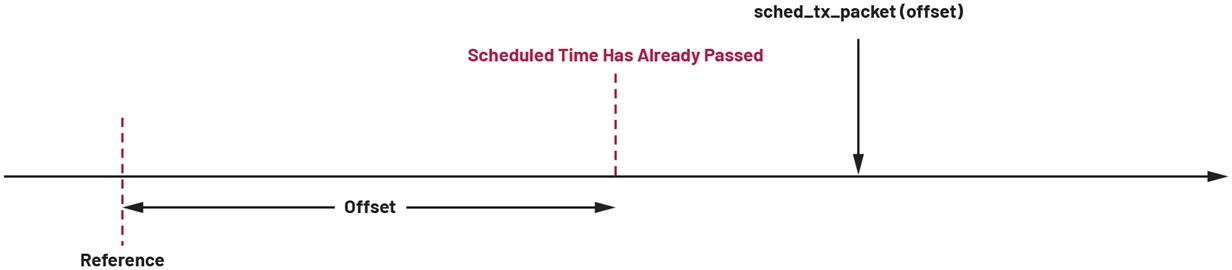

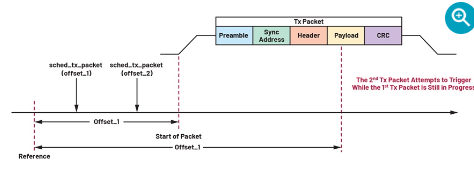

图8显示一种场景,其中使用的时间偏移小于最小允许时间,导致命令被调度至已经过去的时间。

图8. 在超出设置偏移以外的时间调度数据包。

执行两个连续的发射和接收命令(发射-发射或接收-接收)时,如果两个命令都使用单个时间参考,那么第一个数据包的大小是确定用于成功执行第二个命令所需的时间偏移量的重要因素。当第一个数据包的长度增加时,第二个命令的时间偏移量也必须增加,以确保能成功执行该命令。如果使用的时间偏移量小于可允许的最小时间偏移量,则会在仍在执行第一个数据包时调度第二个数据包,导致操作失败。如图9所示。

图9. 使用时间偏移调度数据包。

最大时间偏移量

最大时间偏移量用于防止在设置时间外调度数据包。因为时钟漂移,调度偏离同步参考太远的数据包会导致调度不准确,进而导致信号检测超时或SOF超时。我们将在超时章节详细进探讨这些超时。

周转时间

周转时间是指物理层(PHY)从接收模式变更为发射模式(反之亦然)所需的时间。在周转时间内,模拟RF前端中的组件通电并达到稳定,这需要很长时间。这种时间消耗对低延迟反馈应用来说会更加重要,例如工业系统中的工艺控制环路,其中涉及远程控制机械手臂或其他机器。周转时间仅适用于半双工收发器。

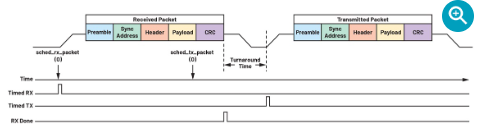

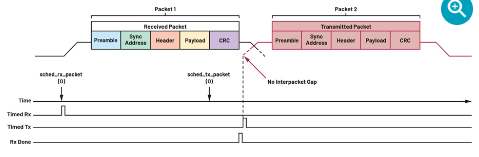

如果用户需要在传输接收包之后,在物理层再次就绪时发送数据包,就会使用周转时间(反之亦然)。

图10显示两个数据包:接收包和发射包。在这个场景中,sched_rx_packet(0)使收发器准备接收数据包。在本示例中,偏移量设置为0,这意味着收发器会在物理层就绪之后,即刻开始接收数据包。接收数据包期间,sched_tx_packet(0)命令被发送,导致物理层切换至周转状态。软件将接收操作完成作为参考点来调度发射数据包,然后添加周转时间值。

图10. 采用周转时间的数据包调度。

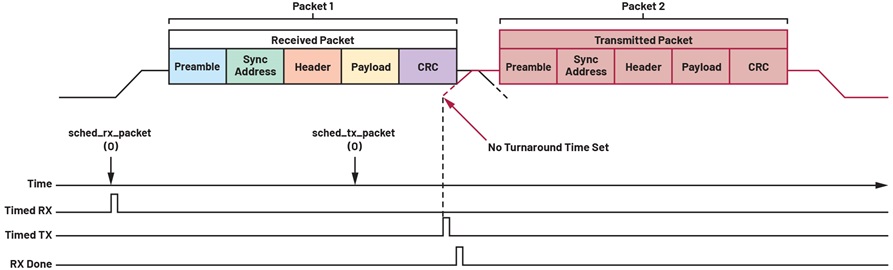

图11显示软件中未设置周转时间时会发生什么情况。由于没有设置周转时间值,调度程序设置在第一个数据包传输完成后即刻开发发送下一个数据包。调度程序不知道物理层尚无法进行发射/接收,因为它还需要更改其状态,导致无法成功传输下一个数据包。

图11. 不采用周转时间的数据包调度。

这说明了设置周转时间的重要性。如果不进行设置,用户将无法知道在发送期间调度的接收能否成功执行(反之亦然)。周转时间值应基于物理层从物理层发送状态转换到物理层接收状态所需的时长决定。本场景对射频器件从发送状态频繁切换到接收状态(反之亦然)的用例至关重要。

数据包之间的时间间隔

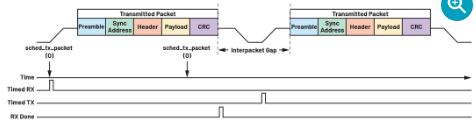

数据包之间的时间间隔是指前一个帧的最后一位和下一个帧的第一个位之间的时间间隔。与周转时间一样,数据包之间的时间间隔被用作参考,用于确定在发送/接收另一个数据包期间,发送数据包的时间间隔。区别在于,数据包之间的时间间隔是用于同类型的两个数据包(发送-发送或接收-接收)之间。收发器需要使用数据包之间的时间间隔来让物理层为下一个数据包做好准备。

图12显示两个数据包:发射包和发射包。在这个场景中,命令 sched_tx_packet(0)使收发器准备好立即发送数据包。在第一个数据包尚未发送完成时发送另一个sched_tx_packet(0)命令,会导致调度程序设置在当前数据包发送完成后,立即开始发送下一个数据包。调度程序将数据包之间的时间间隔用作参考,用于确定何时发送下一个数据包。其值由物理层的下降或上升时间决定。这用于确保物理层已准备好进行下一轮数据包发送/接收。

图12. 采用数据包之间的时间间隔的数据包调度。

图13显示在未设置数据包之间的时间间隔时发生的错误。调度程序设置下一个数据包在第一个数据包发送/接收完成后立即开始发送。但是,与周转时间相同,调度程序并不知道物理层尚未准备好进行另一轮发送/接收。

图13. 不采用数据包之间的时间间隔的数据包调度。

超时

在无线系统中,超时用于防止器件无限等待响应。超时设置了允许器件等待有效响应的时间。如果在该时间段内没有收到有效响应,将报告一个错误。最常见的超时类型如下:

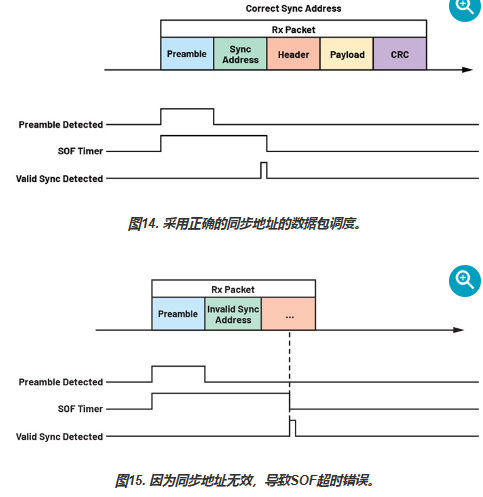

帧开始超时

检测到无效同步时,会发生SOF超时。当SOF定时器在接收到同步字之前过期时,也会发生SOF超时。

图14显示在SOF定时器周期内检测到的有效同步地址,图15显示在分配时间内未检测到有效同步地址时,发生SOF超时的场景。

图15. 因为同步地址无效,导致SOF超时错误。

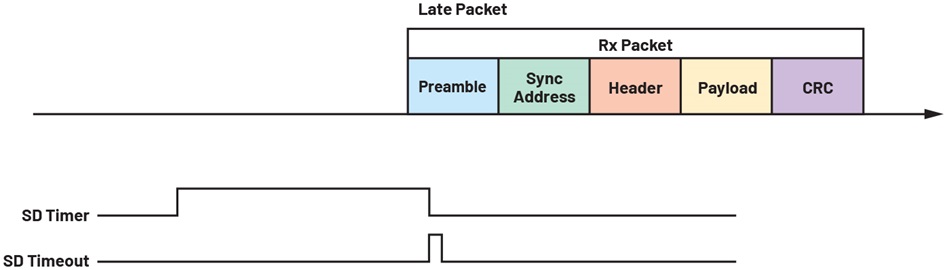

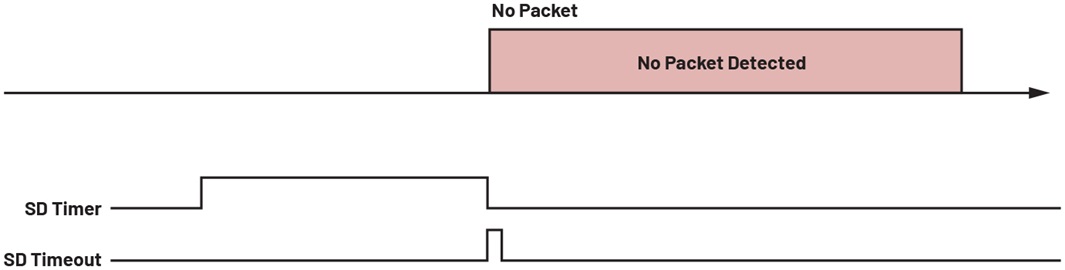

信号检测超时

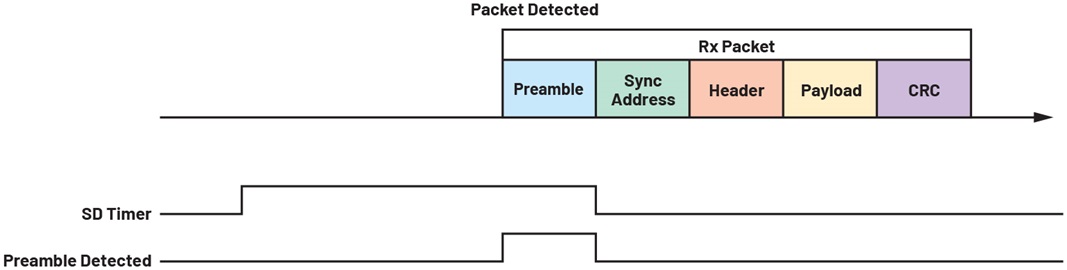

在SD周期内未检测到有效前同步码,或者定时器在接收前同步码之前过期,此时会发生信号检测超时。分别如图16和17所示。

图16. 因为数据包传输延迟,导致SD超时。

图17. 因为未检测到数据包,导致SD超时错误。

图18显示在定时器周期内检测到有效的前同步码的场景;所以,未检测到超时。

图18. 无SD超时。

设置正确的超时周期是非常重要的。超时时间不能太短或太长。如果超时时间太短,会导致杂散检测,也就是存在有效数据包,但因为超时时间太短,没有足够的时间去检测。延长超时时间会降低杂散超时的次数,但会导致器件更长时间处于激活状态,这会消耗和浪费更多功率。

结论

对于无线系统,时间同步是一个非常重要的元素,尤其是对于极为重视数据完整性的应用。有许多因素会影响到系统同步,充分了解时序参数的相关性和特点有助于工程师开发并对高度可靠的无线系统执行无线系统级测试。

审核编辑:郭婷

-

接收机

+关注

关注

8文章

1180浏览量

53453 -

无线通信

+关注

关注

58文章

4564浏览量

143496 -

无线系统

+关注

关注

0文章

289浏览量

21559

发布评论请先 登录

相关推荐

同步电路设计中静态时序分析的时序约束和时序路径

系统时序基础理论之源同步时序要求

同步时序数字电路的分析

基于粒子群算法的同步时序电路初始化

使用时钟PLL的源同步系统时序分析

基于Cadence的源同步时序仿真

如何好好测试无线系统?时序和同步

如何好好测试无线系统?时序和同步

评论