在时序分析时,我们常会碰到的一类现象是:关键路径上的逻辑单元过于分散,导致布线延迟过大,从而造成时序违例。对此,我们可以通过相对位置约束或绝对位置约束来限定相关逻辑的位置关系。就相对位置约束而言,即使芯片型号发生了改变也依然可以继承原有约束;而对于绝对位置约束,一旦芯片型号发生改变就要确认是否要调整相应位置。此外,如果时序违例路径较多,这种方法的有效性将大大降低。

我们还可以采用手工布局的方式,这对于时序违例路径集中在某一个模块或某一个层次内的情形较为适用。使用此方法时需要注意Pblock的大小。Pblock不能太小,否则会增加布局布线的压力;Pblock也不能太大,否则会浪费资源。实际上,Vivado针对Pblock的资源利用率也提供了指导值,该指导值跟整个芯片的资源利用率指导值一致,可通过命令report_failfast查看。

Pblock的形状也是一个重要的因素。通常建议为标准的矩形。不规则的形状如在矩形框中挖掉一个小的矩形形成“回”字形状会严重危害时序性能且导致编译时间增长。Pblock的位置也是一个重要因素。可以先让工具自动布局,在此基础上观察关键模块的分布情况,然后参考此位置确定Pblock的位置。

可以看到,使用Pblock要求工程师有一定的工程经验,需要考虑的因素也较多。如果Pblock的位置不合理,可能会出现顾此失彼的情形(Pblock内的模块时序改善了,而其他模块的时序又恶化了)。Pblock的另一弊端是缺乏灵活性。当芯片型号发生改变时很有可能重新确定Pblock的大小或位置。

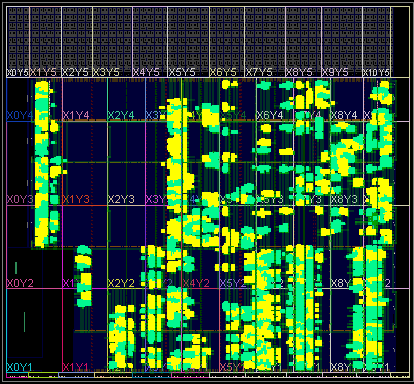

好在Vivado提供了一个新的约束属性USER_CLUSTER(要求Vivado版本为2022.2或之后)。该属性的作用是指导工具在布局时将指定层次/模块下的逻辑单元放得更紧凑一些。为便于说明,我们看一个例子。在没有使用该属性时,布局结果如下图所示。可以看到整个设计的资源利用率并不高,但却比较分散。

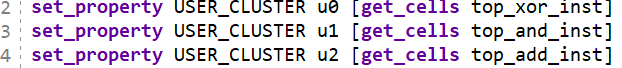

接下来我们使用属性约束USER_CLUSTER。该属性的属性值为用户定义的组名,属性施加的对象为get_cells的返回值,也就是用户通过get_cells指定的模块,如下图所示。

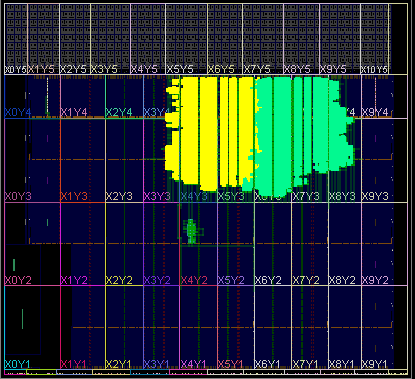

使用此约束之后,最终的布局结果如下图所示。可以看到,相关资源已经非常紧凑了。

相比于手工布局,USER_CLUSTER更为灵活,更为易用。只是需要用户确认哪些模块下的逻辑单元需要放置得紧凑些。

审核编辑:刘清

-

逻辑器

+关注

关注

1文章

10浏览量

6713 -

Vivado

+关注

关注

19文章

860浏览量

71491 -

时序仿真

+关注

关注

0文章

14浏览量

7601

发布评论请先 登录

单片机程序设计的十层功力,你练到那一层了?

PADS9.5 LAYOUT 设置元件 怎样 可以重叠放置 大的中间小的 同一层的?

单片机程序设计的十层功力,你练到那一层了?

单片机程序设计的十层功力,你练到那一层了?

请问FPGA与DDR3是否必须放置在同一层?

介绍一些大功率IGBT模块应用中的一些技术

如何让同一层次的模块在布局时更紧凑一些

让同一层次的模块在布局时更紧凑一些的方法

让同一层次的模块在布局时更紧凑一些的方法

评论