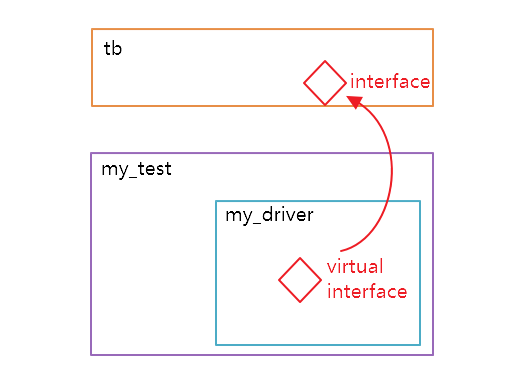

在UVM中,Testcase是一个类,它封装了测试用例开发者编写的特定激励序列。

创建Base Test

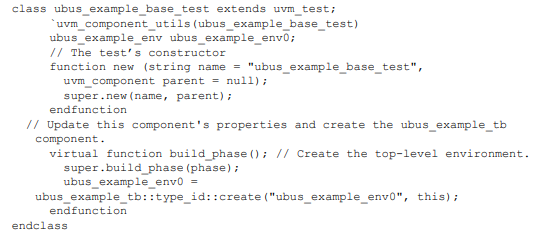

下面首先开发了一个Base Test。这个Base Test是所有基于ubus_example_env开发的测试用例的一个起点。

base test的build_phase()创建了ubus_example_env。任何从ubus_example_base_test派生的Testcase都会继承ubus_example_base_test中的所有定义,这意味着如果派生的Testcase调 用 super.build_phase() , 也会将构建top-levelenvironment。

从Base Test基类创建测试用例

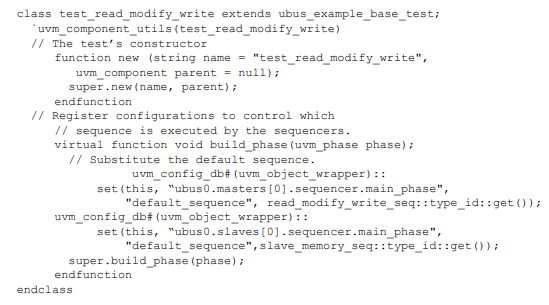

测试用例编写者可以从Base Test派生出使用相同验证环境的测试用例。top-level environment是由Base Test的build_phase()创建的,派生测试用例可 以 对run_phase()做一些 调 整 ( 例 如,改变环境中执行的 default sequence ) 。下 面 是一 个继 承 自ubus_example_base_test 的简单测试用例。

这个测 试 用例改变了由masters[0] agent和slaves[0]agent执 行 的default sequence。

通过基类super.build_phase(),将创建验证环境ubus_example_env0以及它的所有验证子组件。因此,任何会影响这些验证组件构建的配置(比如要创建多少个masters)都必须在调用super.build_phase()之前设置好。

对于这个例子,由于sequences要到后面的phase才开始获取,所以可以在调用super.build_phase()之后再调用uvm_config_db::set。

选择测试用例

在定义了扩展测试用例后,需要调用uvm_pkg::run_test()任务来选择一个要执行仿真的测试用例。它的原型是:

task run_test(string test_name="");

UVM支持通过两种不同的机制指明要运行的测试用例。

测试用例(即已经向factory注册的测试用例名称)可以直接传递给run_test()任务,也可以通过+UVM_TESTNAME在命令行中声明。

如果两种机制都使用,命令行优先。一旦选择了一个测试用例名称,run_test()任务就会调用factory机制来创建一个测试用例的实例,实例名称为uvm_test_top。最后,run_test()通过执行各个phase来启动测试。

下面的例子显示了如何通过仿真器的命令行参数向run_test()任务提供类型名为test_read_modify_write的测试。使用命令行参数可以避免在调用run_test()的任务中hardcode指定testcase名称。在一个initial语句中,调用run_test()如下:

// DUT, interfaces, and all non-UVM code initial uvm_pkg::run_test();

使用仿真器命令行选项选择一个test_read_modify_write类型的测试用例,使用以下命令:

% simulator-command other-options +UVM_TESTNAME=test_read_modify_write

如果提供给run_test()的测试用例名称不存在,仿真器将立即调用$fatal报错退出。如果发生这种情况,很可能是名字打错了或者是`uvm_component_utils宏没有被使用注册这个testcase。

通过使用这种方法,只改变+UVM_TESTNAME参数,可以运行多个测试,而不必重新编译测试平台。

审核编辑:刘清

-

仿真器

+关注

关注

14文章

1018浏览量

83763 -

UVM

+关注

关注

0文章

182浏览量

19179

原文标题:创建UVM Testcase

文章出处:【微信号:芯片验证工程师,微信公众号:芯片验证工程师】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

数字IC验证之“构成uvm测试平台的主要组件”(4)连载中...

什么是uvm?uvm的特点有哪些呢

谈谈UVM中的uvm_info打印

我的第一个UVM代码——Hello world

Modelsim uvm库编译及执行

典型的UVM Testbench架构

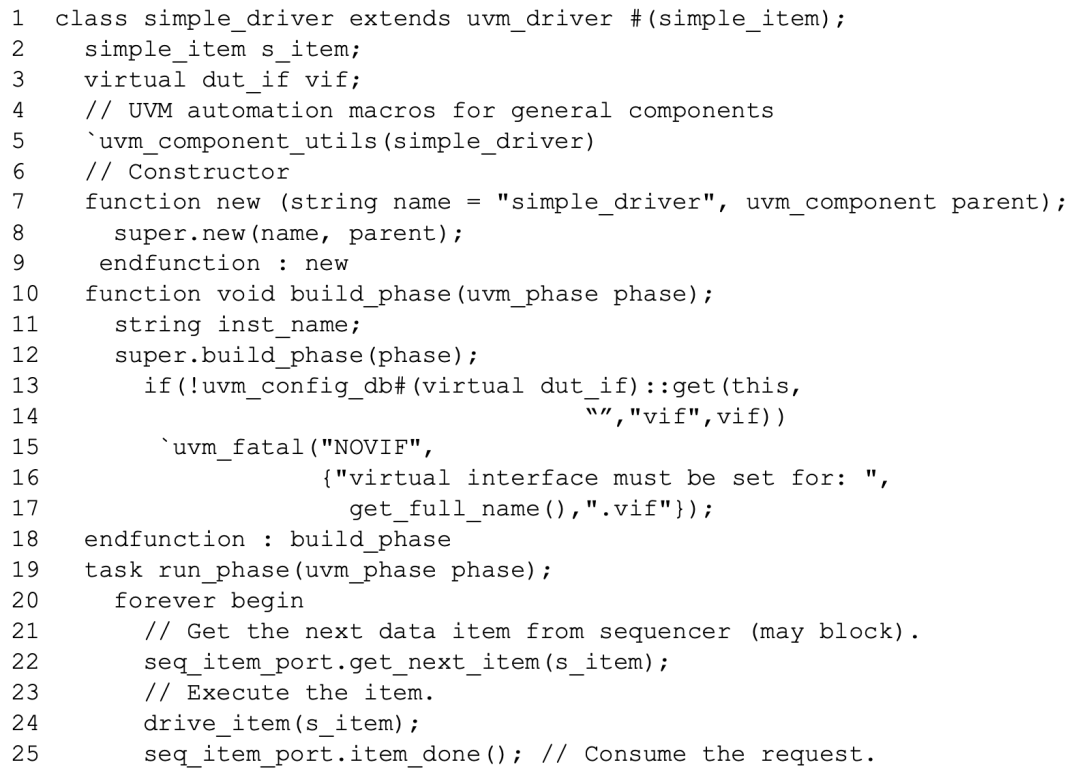

创建UVM Driver

创建UVM Testcase的步骤

创建UVM Testcase的步骤

评论