目前的硬件产品面临着高密、高速的挑战。封装尺寸越来越小,板级布线密度越来越高;总线接口的时钟频率不断提高,数据速率不断提高,时序余量越来越小。同时信号的边沿越来越陡,信号之间相互干扰越来越严重。

工艺越来越先进,信号电压摆幅越来越小,导致信号的噪声余量越来越小者都导致串扰造成的影响越来越严重。对于上个世纪90年代几十兆赫兹的X86系统都已经是新鲜事物,IO接口的电平标准大多为5V或者3.3V的TTL电平,一个时钟周期有几十个ns,信号的噪声裕量(VCC-VIH或者VIL-VSS)甚至会高达1V以上。此时,串扰对时序和噪声的影响就显得没那么重要。然而,数字技术发展日新月异,现在的高速存储器(如DDR3)速率达到1600Mbps,DDR4的速率在此基础上翻一番达到了3200Mbps,DDR5再翻一番最高速率达到了6400Mbps。如此高的数据速率一个数据UI只有156ps,这就对系统的时序设计提出了更高的要求。同时,随着速率的提升IO电压也在不断地降低,这对信号之间的噪声干扰控制是一个新的挑战。

广义上来讲任何两个网络之间都存在串扰。串扰是指有害信号从一个网络转移到另一个网络,串扰是发生在一个网络的信号路径及返回路径和另一个网络的信号路径及返回路径之间的一种效应。

系统中信号之间串扰影响的主要表现有两个方面:第一,串扰会使传输线的特征阻抗和传播速度发生变化,影响系统的时序问题;第二,串扰会在其它传输线上引入感应噪声,使信号的噪声容限减小。这一噪声也有可能发生在信号的边沿导致抖动增加或者时钟信号边沿不再单调,等等这些都可能导致系统设计的失败。

01

电路角度理解串扰

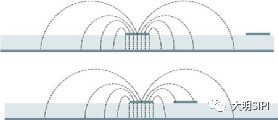

当信号沿传输线传播时,信号路径和返回路径之间将产生电力线;围绕在信号路径和返回路径周围也有磁力线圈。这些场会延伸到周围的空间。相邻传输线之间的场的相互作用就会产生串扰。

我们可以把这种电场和磁场的耦合,简化为电路中的容性和感性耦合。串扰就主要表现为容性串扰和感性串扰。

串扰是不同传输线之间的能量耦合,引起串扰的原因不同传输线或者信号的传输路径之间存在着电磁场耦合。这一耦合只与作为信号传输载体的传输线的无源特性相关。有人会说,传输线间的耦合如果只和传输线结构的无源特性相关,那为什么随着信号速率的提高串扰会越来越严重呢?

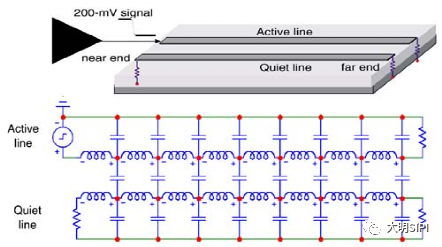

传统的信号完整性理论都会把传输线间的电磁场耦合分成容性耦合和感性耦合。两条传输线通过电场产生的耦合以互容Cm表示,侵害网络通过互容在受害网络上引起的噪声电流

传输线间通过磁场产生的耦合以互感Lm表示,侵害网络通过互感在受害网络上引起的噪声电压

可见,噪声电流Ic与互容Cm和电压变化率dV/dt成正比,噪声电压VL同互感Lm和电流变化率dI/dt成正比。

其中,Cm和Lm代表了传输线间的耦合,即传输线的无源特性;

电流噪声Ic乘以被害网络的阻抗也可以表示为噪声电压;

dV/dt其实就是信号边沿的斜率,反映的是激励信号的特性。

在信号幅度一定的情况下噪声电流和信号的上升时间成反比,同样由噪声电压的计算公式也可以得出这一结论。

实际上信号的上升时间dt的长短对应的就是信号的频谱带宽,信号上升时间越短信号的有效频谱成分越高产生的串扰噪声越大,信号的上升时间dt越大信号的有效频谱成分越低产生的串扰噪声越小。分析到这一层次,我们可以清楚地知道串扰与无源的传输线的物理结构和激励信号本身特性这两个方面相关,无源的传输线的物理结构确定以后,串扰的值由激励信号的特性所决定,也就是说不同频率成分的信号通过同一无源系统所产生的串扰也是不同的。

01 - 1

容性串扰

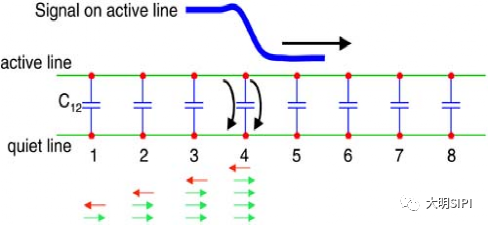

如下图所示,把信号的上升沿看作是沿动态线移动的电流源,信号前沿区,有容性耦合电流流入静态线。

上图所示,红色箭头所示为后向电流,下面绿色箭头所示为前向电流。它们的传播及叠加示意如上,前向电流和后向电流方向相反,但产生的噪声电压都是正的。

很明显,绿色的前向电流产生的噪声随着时间的推移宽度不变,但幅度在增大;而红色所示的后向电流产生的噪声幅度不变、宽度在增加,直到信号边沿到达接收端前向噪声电压的宽度达到最大值2倍的TD(传输线延时)。

01 - 2

感性串扰

相邻布线之间的互感在受害网络产生一个感应电压。

上图所示,上边红色箭头是后向电压,下面绿色箭头是前向电压的传播及叠加示意图。前向噪声电压为负和后向噪声电压为正。

与容性串扰类似,绿色的前向电流产生的噪声随着时间的推移宽度不变,但幅度在增大;而红色所示的后向电流产生的噪声幅度不变、宽度在增加,直到信号边沿到达接收端前向噪声电压的E宽度达到最大值2倍的TD(传输线延时)。

01 - 3

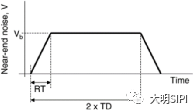

近端串扰

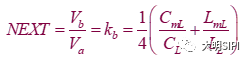

近端串扰其实就是后向的容性和感性串扰之和。上面对于容性和感性串扰的分析可知,在大于RT时间之后无论容性和感性的后向串扰的幅度都是固定的。如下所示为近端串扰的计算式,串扰仅和互容、互感与传输线自容、自感的比值相关。

下图为微带线和带状线在不同线间距情况下的近端串扰系数。可明显看出:随着线间距增大,近端串扰减小,当信号线间距在3W以上时,近端串扰在一个比较低的水平。

01 - 4

远端串扰

远端串扰其实就是前向的容性和感性串扰之和。上面对于容性和感性串扰的分析可知,远端串扰会随着信号的向前传播而累加。如下所示为远端串扰的计算式,远端串扰和互容、互感与传输线自容、自感的比值相关,并且容性前向串扰和感性的前向串扰方向相反。

远端串扰系数:

我们注意到:如果所有导线周围的介质材料是同质的,而且是均匀分布的,如两条耦合的完全嵌入式微带线或两条耦合带状线,则相对容性耦合和相对感性耦合是完全相同的,在这种结构中就不会出现远端串扰。

而微带线由于信号线的介质在PCB板上是PP,板外的介质是空气,有着不同的介电常数。因此,微带线的远端串扰要大于带状线。

而实际上,我们使用的介质并不是均匀的:

(1)通常的FR4介质是由玻璃纤维和环氧树脂编制而成,而玻璃纤维和树脂的介电常数是不同的。

(2)玻璃纤维的编织有疏有密;不同类型的介质树脂的含量也不尽相同。

因此,实际的设计中,带状线也会还是会存在远端串扰。使用介电常数为均匀稳定的介质,并尽量使用带状线布线对减小串扰、提高高速链路性能非常重要。

02

电路角度理解串扰的局限

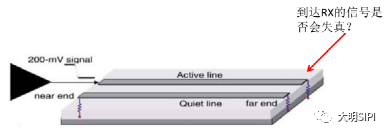

以上所讲的容性、感性、近端、远端串扰都是从电路的角度来理解串扰。不知道大家有没有发现一些不对的地方。按照容性串扰和感性串扰前向串扰的解释,前向串扰的值应该是一直叠加下去,信号线越长,串扰的幅值越大才对。但实际的测试情况是这样的吗?

真实的近端和远端串扰的测试结果如下,我们发现远端串扰是会饱和的,并不会无限的增大下去。

传统的、电路角度的串扰解释是在假设产生串扰的过程中,也就是信号在传输的过程中,信号本身没有变化的基础上得出的结论!

显然这是不可能的。因为随着信号的传输,信号的能量已经通过容性和感性耦合进入到了受害网络了,这样的话攻击线上的信号本身已经有了一定的衰减。

攻击线上的入侵信号也会失真。这个失真主要来自于两个方面:

(1)传输线损耗;

(2)耦合到受害网络上的能量。

上面所讲到的容性串扰、感性串扰、近端串扰、远端串扰的公式都是从电路角度得出的,目的是便于我们理解串扰,但并不准确。因此,那些公式没必要死记硬背,只需要了解串扰和哪些因素相关即可。后面有机会会讲一下S参数,用S参数来表示串扰更加方便也更准确。

03

串扰的控制

接下来该讲一讲控制串扰的方法。首先从信号路径考虑控制串扰:

•减小走线并行长度;

•拉大布线间距;

•避免相邻层布线;

•减小传输线与参考平面的间距。

•关注阻抗的影响!

驱动器的阻抗一般比较低,如果没有匹配的话在串扰到达驱动器端将发生负反射(反射系数为负数),串扰将返回远端影响负载的接收。

对于TTL、CMOS等电平负载端阻抗一般为高阻,远端串扰会在负载端由于全反射而加倍。

因此,源端和负载端的阻抗匹配,不仅能够消除有用信号的反射,而且也能消除串扰信号的反射,有利于降低串扰。

其次,减小串扰不仅需要从信号路径入手更要关注信号的返回路径,同时也要考虑相邻过孔之间的垂直耦合。

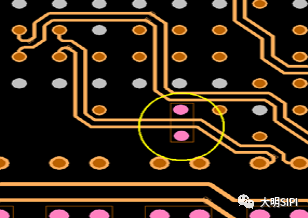

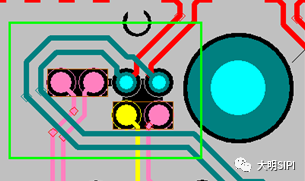

•布线与过孔之间:关键信号不要走进其它信号的antipad区域。其它信号也不能进入关键信号过孔的antipad。

•过孔与过孔之间的垂直耦合:由于信号在流经过孔时,返回路径比较复杂,因此如果过孔之间的间距太近,串扰也会非常严重;

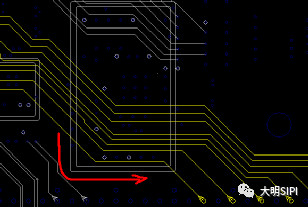

•返回路径之间:如一组总线同时跨分割的情况,虽然信号线间距比较大,但是会存在很多信号的返回路径重叠的情况,也会产生严重的串扰。

•布线与平面之间(电源);如果信号线以高电压、大噪声的电源为参考平面,那么电源噪声也会耦合到信号线上。

-

CMOS

+关注

关注

58文章

5750浏览量

236298 -

PCB板

+关注

关注

27文章

1453浏览量

52090 -

TTL电路

+关注

关注

2文章

65浏览量

15152 -

信号完整性

+关注

关注

68文章

1417浏览量

95690 -

电磁场

+关注

关注

0文章

797浏览量

47441

发布评论请先 登录

相关推荐

DAC信号完整性浅析 DAC信号完整性解决方案

浅析信号完整性中的串扰

浅析信号完整性中的串扰

评论