01

远端簇型拓扑介绍

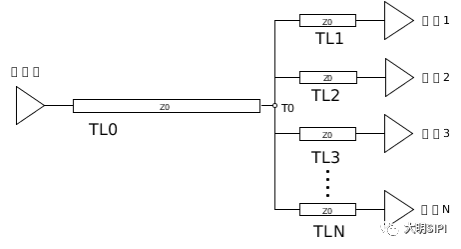

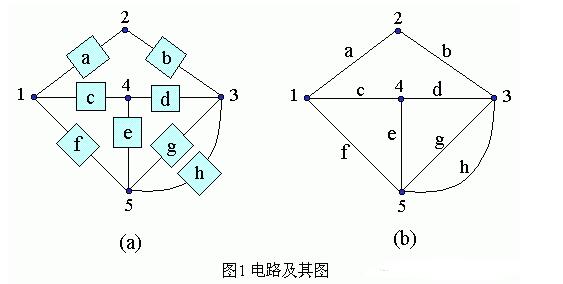

下图为远端簇型拓扑结构的示意图。从驱动器到分支点T0这段传输线TL0的长度相对于分支点到各个负载处传输线TL1~TLN要长很多。这种结构多用于多个负载的位置相对集中的情况。

其拓扑结构有如下特点:

1.链路中只有T0一个阻抗不连续点;

2.负载很多时T0点前后的阻抗突变很大。T0点前阻抗为

,在有N个负载的情况下T0点后的阻抗为

,在有N个负载的情况下T0点后的阻抗为

也就是说负载数越多入射波在T0点发生的负反射越严重。

3.此外,从各个负载反射回源端的反射信号到达T0点也会发生负反射。如果T0点到各个负载的布线TL1~TLN没有严格控制等长的话,负载之间的相互影响就会变得很严重。

4.当TL1~TLN严格控制等长时,所有负载的接收波形一致性会非常好。这也给解决信号完整性问题带来了方便。

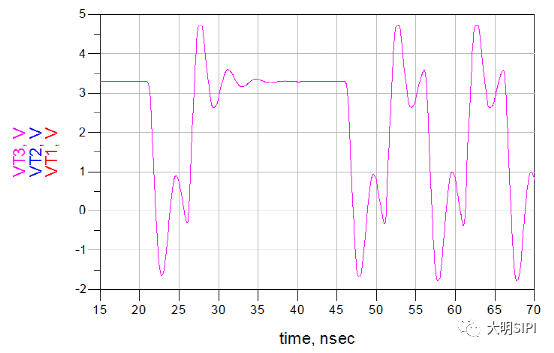

使用ADS搭建一个一驱三的远端簇拓扑。驱动器为3.3VLVCMOS电平,输出阻抗20ohm、上升时间为500ps、下降时间1ns左右;TL0长度为2000mil,TL1=TL2=TL3=1000mil。

传输线的延时按照6mil/ps计算,分支线TL1~TL3的延时为166ps左右,已经达到了上升时间的1/3,分支线能够体现传输线效应。

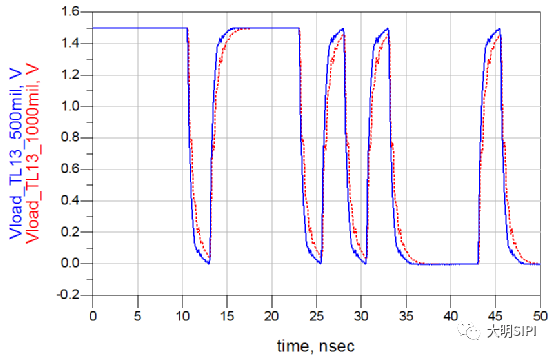

仿真结果如下所示,信号边沿单调、由于驱动器输出过驱动,负载接收波形存在较大的过冲和振铃,且三个负载的接收波形完全重叠。

02

远端簇拓扑的SI分析

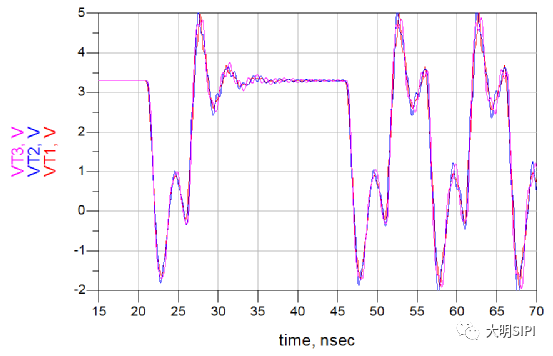

那么当T0点到各个负载的布线长度不同时又会出现什么现象呢?我们将TL1调整到500mil,TL3调整到1500mil,TL2为1000mil不变。此时的仿真结果如下所示:

当T0点到各个负载的布线长度不等长时三个负载的接收波形就出现了差异:

1.所有负载在接收波形在稳定电平处都会有幅度微小的震荡,而且信号的过冲明显超过了TL1、TL2、TL3等长时的幅度。

2.这些震荡和过冲的增大就来自于三个负载之间的相互影响,但这一影响并不足以影响信号质量,而接收波形中存在的过冲显而易见是由于驱动器驱动能力过强导致只需要添加源端匹配即可解决。

3.由此可见一般的LVTTL或者CMOS电平的低速总线的设计,使用远端簇的拓扑大多能够解决信号完整性问题。

ØT0点到负载端布线延时的影响

除了需要保证各个负载所在分支布线等长外,还需要注意分支的延时。虽然相比菊花链拓扑远端簇拓扑已经极大的改善了信号质量,但我们也需要注意拓扑中毕竟还是存在T0点这个阻抗不连续点。在远端簇拓扑中负载的个数、T0点到负载的布线延时、驱动器输出信号的上升时间对负载端接收信号的信号质量都有着密切关系。

我们通常认为:“T0点到负载的布线延时如果小于上升时间的一半时就不会对信号质量有明显的影响,如果T0点到负载的布线延时大于信号上升时间的一半时就会在信号边沿产生明显的回沟或者台阶。” 这只是一个经验法则不一定很精确但却可以帮助我们快速地发现问题。

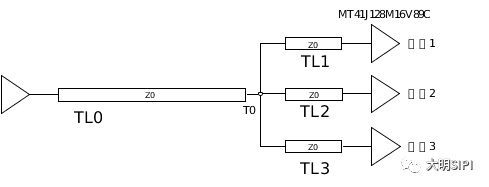

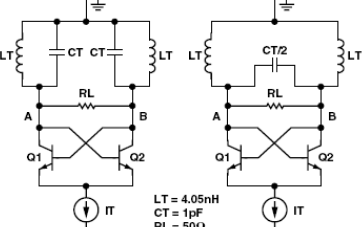

为了验证这一结论我们在ADS中搭建DDR3地址信号的仿真电路进行分析。驱动端使用TI的C6678处理器的DDR3接口地址信号buffer,负载使用美光的DDR3存储器。查看6678的IBIS模型可知其地址信号输出上升下降时间均为260ps左右,输出阻抗40ohm。仿真对比两种情况:(1)设置TL0=2000mil,TL1~TL3长度为1000mil、延时170ps大于上升时间的一半;(2)TL0=2500mil,TL1~TL3长度为500mil、延时85ps小于上升时间的一半。

图1.800Mbps

(1)上图所示红色点虚线的波形,由于TL1TL3的延时大于信号上升时间一半导致在负载端的接收波形上升下降边都存在一个很小的回沟,当然这个回沟也会随着TL1TL3的布线延时、负载的个数的增大而增大;

(2)蓝色实线波形,TL1~TL3的延时小于信号上升时间一半,负载端的接收波形边沿单调。

红色虚线回沟的产生显然是和源端阻抗是否匹配没有太大的关系的,是由于负载和分支点之间的反射导致。对于数据信号在时序余量充足的情况下,很小的回沟或者台阶影响不大;但是如果是时钟信号就要考虑如何消除回沟了。如果由于受布局等因素的限制无法减小分支布线延时,对于单端信号我们可以通过添加戴维南端接来解决这一问题。

标准的戴维南匹配应该是接在拓扑的最末端但对于远端簇拓扑我们也只能添加在分支点T0位置,这就可能导致戴维南匹配起不到预期的效果;

对于差分信号可以考虑在每个负载端都在两根差分线间加跨接电阻,但此时所有跨接电阻的阻值都相当于并联在一起,会使信号的幅度明显减小。也可以只在分支点处加一个跨接电阻,阻值需要通过仿真确定。

最关键的一点需要我们记住,就是时钟信号不到万不得以不要驱动两个以上的负载,对于高速信号的多负载结构消除回沟和台阶需要付出的代价会非常大。由于PCB板以及系统工作中存在太多的不可控因素,无论采用何种方式的匹配都无法完全规避风险。

远端簇拓扑在比较低速的DDR2等总线的设计中有一些应用。当然这需要一定的约束条件,比如说需要考虑:

(1)驱动器的驱动能力;

(2)分支点到负载的布线长度等条件同时也会受到芯片布局的限制;

(3)负载的个数。需要注意负载个数太多会导致分支点处的阻抗突变非常大,同时也可能会导致布线层数的增加使PCB成本上升。

如果负载的个数增加导致远端簇拓扑无法满足要求,我们就需要考虑更换拓扑方式树型拓扑是一个很好的选择被广泛应用于多负载的DDR、DDR2以及DIMM条的设计中。

-

处理器

+关注

关注

68文章

19524浏览量

231768 -

驱动器

+关注

关注

54文章

8365浏览量

147587 -

DDR3

+关注

关注

2文章

277浏览量

42540 -

仿真器

+关注

关注

14文章

1019浏览量

84101 -

CMOS电平

+关注

关注

0文章

19浏览量

7265

发布评论请先 登录

相关推荐

不同的充电拓扑结构介绍

BOOST电路拓扑结构介绍

ddr3菊花链拓扑结构是什么

介绍一种负载比较集中时采用的拓扑结构—远端簇拓扑

介绍一种负载比较集中时采用的拓扑结构—远端簇拓扑

评论