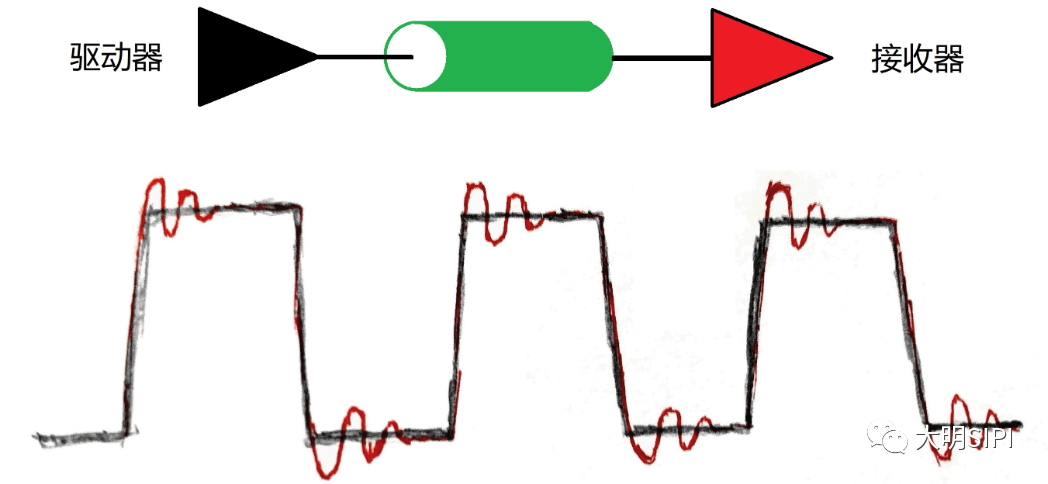

信号在驱动器和接收器之间传输时,由于源端和末端反射的存在就会导致多次反射,反射的结果就是导致接收端的波形产生信号的畸变。当驱动器的驱动能力强时可能导致过冲和振铃;当驱动器的驱动能力比较弱时,可能会导致信号边沿退化严重甚至边沿不单调。

当过冲超过接收器的规范要求就会对器件寿命产生影响;过冲过大也会导致信号链路上产生远高于信号频率本身的高频分量,从而导致更加严重的EMI问题,这也可能导致系统设计失败;当振铃过于严重就会影响信号的有效位宽和噪声裕量,有效位宽减小会导致信号建立、保持时间余量不足,噪声余量减小会导致信号抗干扰能力的降低,串扰和电源噪声都可能导致信号的误判;时钟信号如果存在边沿不单调则也可能导致接收器接收数据错误。因此可以说控制传输路径上的反射是信号完整性分析的首要任务。而控制反射最常用的手段就是源端匹配和终端端接。

01

源端匹配

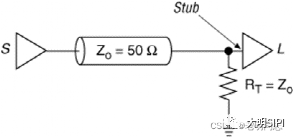

实际设计中最常用的源端匹配方式就是在驱动器输出端加串联电阻。电阻的阻值需要根据驱动器的输出阻抗来决定,匹配电阻加上驱动器输出阻抗等于传输线阻抗时能够完全消除源端的反射。

如上所示,在驱动器输出就近加33ohm匹配电阻Rmatch,使Rmatch+Rs=50ohm。信号进入传输线时在Vdrv点50ohm电阻和50ohm的传输线分压,得到的信号幅值只有1.65V。1.65V的入射电压沿传输线传播到接收端发生全反射,产生1.65V的反射信号。这就导致在接收端接收到的幅值为3.3V,同时反射信号向源端传输,由于源端的阻抗已经匹配,当反射信号到达源端之后就不会再发生反射。

由此可见,源端匹配的作用就是让驱动器输出端的阻抗(包含驱动器内阻和匹配电阻)与传输线阻抗匹配,抑制了终端不匹配导致的反射信号在源端发生二次反射,进而抑制了多次反射的发生。抑制了多次反射,也就抑制了信号的过冲和振铃,无论对器件的寿命还是接收端信号的有效判决都有重要的意义。

采用源端匹配方式时,需要注意匹配电阻阻值的选择和匹配电阻布局这两个方面。源端匹配电阻选择以匹配传输线阻抗为目的,但也并不是选择了合适的阻值就能够起到预期的作用,如果匹配电阻的布局不合理它的效果就会大打折扣。

02

匹配电阻的布局

前面讲传输线的效应时曾经提到,通常认为当信号传输延时小于信号上升时间1/6时,互连线处在集总区域,不会体现出传输线效应。这一点应用到匹配电阻的布局中就要求,源端匹配电阻布局要尽量靠近驱动器。因为只有让匹配电阻和驱动器内阻之间的互连线(TLD2)延时小于信号上升时间的1/6才能够使驱动器内阻和这段互连线加上匹配电阻看作是集总的,将这三部分集总在一起考虑。

下面我们可以仿真对比一下当信号上升时间为50ps时驱动器内阻到匹配电阻的互连线延时分别为8ps(小于50ps的1/6)、20ps、50ps(与信号上升时间相当)时的接收器件接收到的信号波形。

为了更好地观测仿真结果,将三种情况信号的延时分别错开了1ns。

需要注意的是,这里的仿真为了让读者更加清晰的看到驱动器内阻到匹配电阻的互连线延时的影响,将信号的上升时间设置为50ps是非常快,实际应用中除了高速串行链路和DDR等高速并行总线上升时间并不会达到这么快。

从上面的仿真结果可以看出:

1.驱动器内阻到匹配电阻的互连线长度对接收器接收波形有很大影响,会在接收波形稳定电平处产生周期性的过冲和震荡,且过冲的间隔等于传输线延时的两倍。这说明由于驱动器内阻到匹配电阻的互连线的存在使得源端并没有完全匹配,在驱动器和接收器之间还是存在着反射信号;

2.驱动器内阻到匹配电阻的互连线延时小于信号上升时间延时1/6时产生的反射信号对信号质量影响很小;互连线延时超过信号上升时间延时1/6、甚至和信号上升时间相当时产生的反射信号非常大,会产生比较大的过冲,且过冲的幅度随着延时的增大而增大,匹配电阻所起到的匹配效果也会更差。

由此可见,对于一个上升时间有1ns左右的LVTTL或者CMOS电平信号,只要驱动器内阻到匹配电阻之间的延时不超过150ps,匹配电阻就能起到良好的匹配效果。微带线的延时大概140ps/inch,带状线170ps/inch,也就是说只要这段互连线布线长度不超过1inch即可;但是对于DDR等高速内存接口上升时间可能只有几十ps,这对匹配电阻的布局和布线要求就相当严格了,因此这些高速接口常常使用的是芯片内部匹配端接。

03

驱动器的驱动能力

驱动器输出阻抗从一定程度上反映了驱动器的驱动能力。根据输出电阻的大小可以分为过驱动和欠驱动两种情况。下图所示为驱动器输出一个上升时间500ps的3.3V阶跃信号,输出阻抗分别为20ohm、80ohm的时候,在接收端接收到的信号波形。

所谓过驱动就是驱动器输出阻抗(驱动器内阻加上源端匹配电阻)小于传输线阻抗的情况,此时进入传输线的入射电压大于1/2VCCIO,接收端反射回来的信号在源端发生负反射从而使接收端信号产生过冲和振铃,经过多次反射后稳定于VCCIO电平。

欠驱动就是驱动器输出阻抗大于传输线阻抗的情况,此时进入传输线的入射电压小于1/2VCCIO,接收端接收到的电压幅值小于VCCIO,接收端反射回来的信号在源端发生正反射从而使接收端信号产生阶梯状上升的趋势,经过几次反射之后才能到达稳定的VCC电平。总体上看,过驱动时信号边沿很陡并且存在过冲,而欠驱动时信号边沿很缓。

另外,除了使用驱动器输出阻抗来表示驱动器输出能力之外,还可以使用驱动电流来表示驱动能力的大小,比如说xilinx的FPGA中LVTTL、CMOS电平的驱动电流通常在4mA到24mA可调,驱动电流越大说明驱动能力越强。

04

—

信号上升时间

信号上升时间对信号质量有重要的影响。在过驱动情况下,如果上升时间很快,信号将很快达到过冲的峰值,如果信号的上升时间很长那么过冲达到峰值的时间也会变长甚至不能达到峰值;在欠驱动的情况下,信号的上升时间很短会在信号边沿上形成明显的台阶,随着信号上升时间的增大台阶会越来越不明显最后可能消失。无论是过冲还是台阶它们的宽度都和传输线延时有关,由此信号上升时间和传输线延时应该有一定的关系使相互作用对最终信号质量产生影响。

过驱动情况下,驱动器到接收器之间传输线延时为1ns,信号上升时间分别为1ns、2ns、3ns情况接收器接收波形如下图所示:

当信号上升时间小于2倍的传输线延时,接收端过冲能够达到峰值;当信号上升时间大于2倍的传输线延时时, 接收端过冲峰值减小,上升时间越大过冲越不明显。

欠驱动情况下,驱动器到接收器之间传输线延时为1ns,信号上升时间分别为1ns、2ns、3ns情况接收器接收波形如下图所示:

当信号上升时间小2倍的传输线延时时,接收端信号存在台阶,台阶的大小为2倍的传输线延时减去上升时间;当信号上升时间大于2倍的传输线延时时, 接收端台阶不再明显,上升时间越大信号的边沿越缓。这再一次证明了为什么说上升时间越快、传输线长度越长带来的信号完整性问题越严重。

-

驱动器

+关注

关注

52文章

8149浏览量

145945 -

接收器

+关注

关注

14文章

2456浏览量

71789 -

DDR

+关注

关注

11文章

711浏览量

65218 -

信号完整性

+关注

关注

68文章

1397浏览量

95376 -

电源噪声

+关注

关注

3文章

149浏览量

17462

发布评论请先 登录

相关推荐

信号完整性实际设计中最常用的源端匹配方式

信号完整性实际设计中最常用的源端匹配方式

评论