与500ksps以上的ADC通信非常困难。在SPI通信中添加另一个变量(如电平转换器或隔离器)需要对时序以及修改硬件和固件有更多的了解。本应用笔记讨论了如何使用电平转换器或隔离器实现所需的动态性能。

介绍

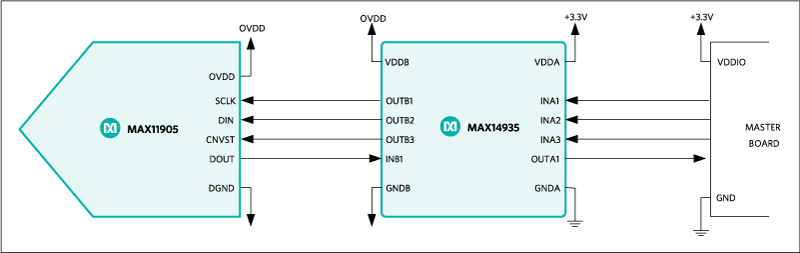

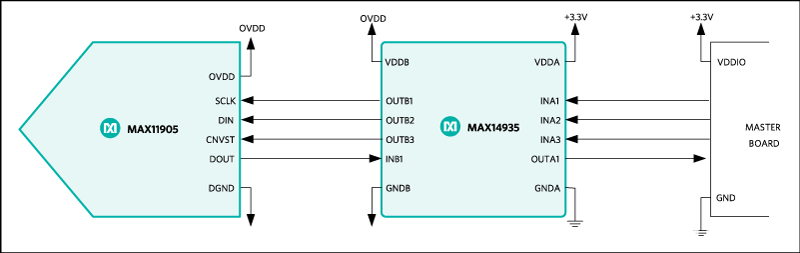

MAX11905为20位、全差分SAR模数转换器(ADC),采样速率为1.6Msps。使用MAX11905设计电路板时,一个要求是测试不同范围的V。奥夫德,1.5V至3.6V。MAX11905评估板采用MAX14935隔离器,工作速率为150Msps,两端支持1.71V至5.5V I/O转换。在ADC和主板之间集成隔离器并不像连接所有I/O信号那么简单。在本应用笔记中,我们将讨论如何实现所需的动态性能。

设计和测试(一般情况)

在一般情况下,图1中的设计工作在低采样速率下,这意味着SPI SCLK在1MHz以下很慢。在这种情况下,主器件以75MHz SCLK运行,以实现1.6Msps。MAX14935具有37.7ns的典型传播延迟,用于PLH和 37.9ns 对于 t菲尔.当MAX11905准备返回数据时,信号通过隔离器两次,典型传播延迟为75.4ns至75.8ns。在处理高速和高分辨率时,每一纳秒都开始变得至关重要。

图1.ADC与隔离器的数字通信电路(一般情况)。

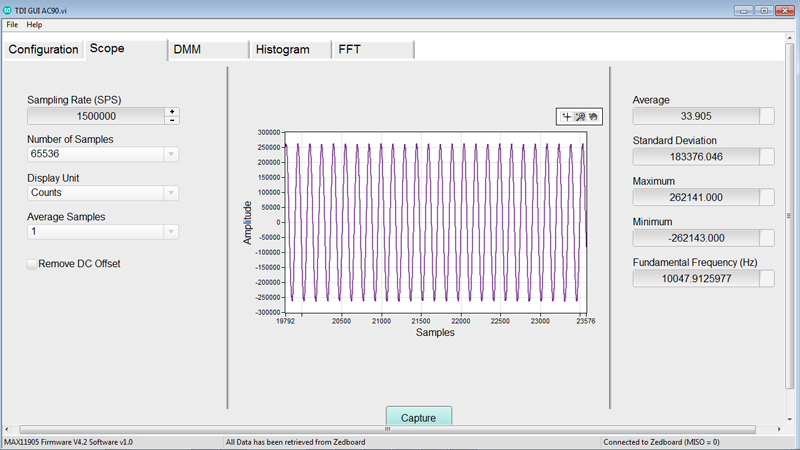

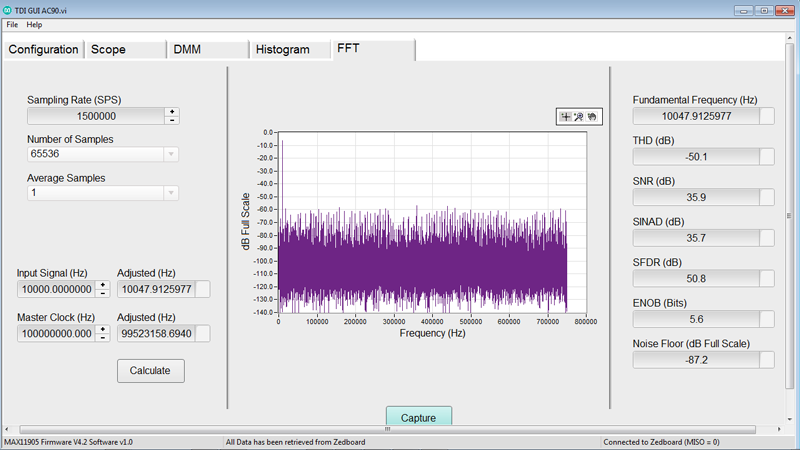

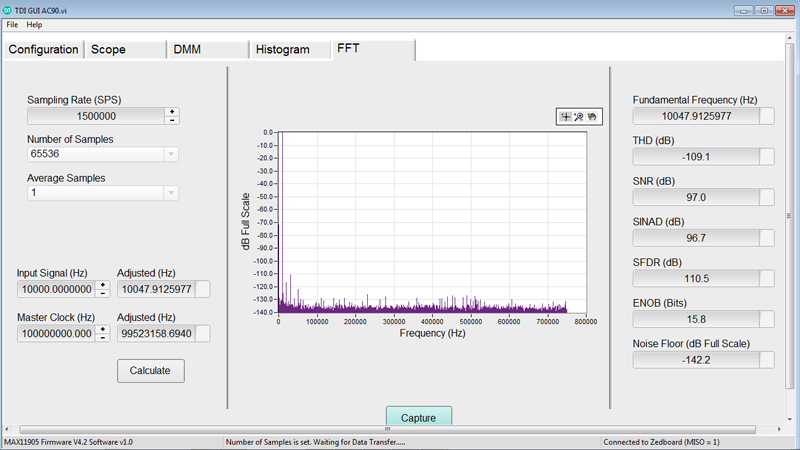

在测试图1电路时,数据不能超过±262,143个计数,并且MAX11905输入端施加满量程正弦波时,正负峰值被削波。图2为使用MAX11905评估板软件采集的数据。预期数据应该接近 ±524,287 计数。由于隔离器的延迟,数据的MSB丢失,只能捕获19位数据,而不是20位。缺失的位极大地影响了动态性能。MAX11905的额定SNR为98.1dB。图3显示信噪比仅为35.9dB。他的问题是如何解决的?

图2.一般情况的数据捕获。

图3.ADC与隔离器的数字通信FFT(一般情况)。

设计和测试(高速案例)

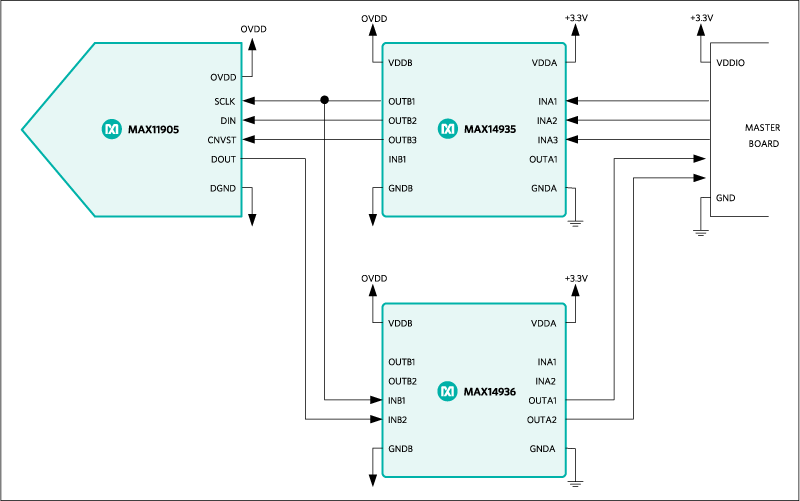

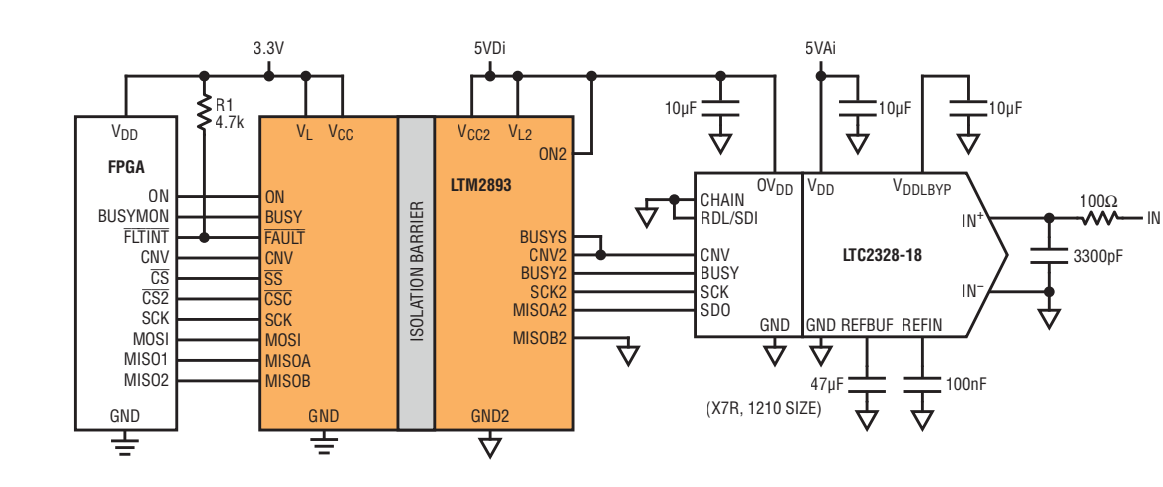

为了便于比较,图4称为高速情况。系统中引入了另一个隔离器MAX14936(相同的器件系列,但不同方向的I/O数量不同)。注意在MAX11905和MAX14935之间有一个SCLK的副本,然后通过MAX14936路由回主器件。使用SCLK的副本,消除了延迟和D外数据使用正确的 SCLK 边沿计时。我们不仅引入了新的硬件,而且设计还需要固件调整以接受返回的SCLK。主设备需要使用 SCLK 的副本来存储数据。要记住的另一个注意事项是将返回的SCLK和DOUT放在同一个隔离器上。不能保证MAX14935/6传播延迟在不同器件之间是相同的。

图4.ADC与隔离器的数字通信电路(高速外壳)。

图5显示了两个隔离器和一个返回SCLK的性能。动态性能更接近MAX11905的预期。

图5.ADC与隔离器的数字通信FFT(高速外壳)。

| 参数 | 一般情况(分贝) | 高速外壳 (dB) |

| 谐波失真 | -50.1 | -114.9 |

| 信 噪 比 | 35.9 | 97.4 |

| 西纳德 | 35.7 | 97.4 |

| SFDR | 50.8 | 118.2 |

| 伊诺布 | 5.6 | 15.9 |

| 本底噪声 | -87.2 | -139.7 |

结论

当使用MAX11905等带有隔离器/电平转换器的器件设计高速、高分辨率ADC时,始终将带有DOUT的SCLK副本返回给主器件。将此设计应用于所有高速、高分辨率ADC,实现所需的动态性能。这样做可以节省创建新硬件和固件的时间和金钱。

审核编辑:郭婷

-

转换器

+关注

关注

27文章

8703浏览量

147181 -

电路板

+关注

关注

140文章

4960浏览量

97847 -

隔离器

+关注

关注

4文章

773浏览量

38332

发布评论请先 登录

相关推荐

在系统中的高速、高分辨率ADC中实现所需的动态性能

ADC信噪比要怎么分析?高速高分辨率ADC电路要怎么实现?

ADC信噪比的分析及高速高分辨率ADC电路的实现

高速ADC产品瞄准大带宽高分辨率应用

高分辨率ADC的板布线分析

基于高分辨率A/D转换器和DL技术实现时钟稳定电路的设计

用于高分辨率1Msps ADC的μModule隔离解决方案

在具有电平转换器/隔离器的高速、高分辨率ADC中实现所需的动态性能

在具有电平转换器/隔离器的高速、高分辨率ADC中实现所需的动态性能

评论