Chris Augusta 和 Martin Murnane

人们常常想当然地为印刷电路板上的电路上电,殊不知这可能造成破坏以及有损或无损闩锁状况。这些问题可能并不突出,直到量产开始,器件和设计的容差接受检验时才被发现,但为时已晚,项目和产品的时间及交货将会受到极大影响,成本大幅攀升。为了解决这一阶段中发现的错误,将需要进行大量修改,包括PCB布局变更、设计更改和额外的异常现象等。

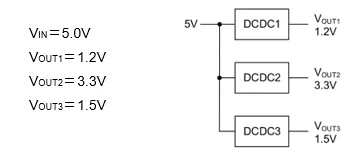

随着集成电路(IC)时代的到来,许多功能模块被集成到一个IC中,因而需要利用多个电源为这些模块供电。这些电源的电压有时候相同,但更多时候是不同的。市场上的片上系统(SoC) IC越来越多,这就产生了对电源进行时序控制和管理的需求

ADI公司的数据手册通常会提供足够的信息,指导设计工程师针对各IC设计正确的上电序列。然而,某些IC明确要求定义恰当的上电序列。对于ADI公司的许多IC,情况都是如此。在使用多个电源的IC中,如转换器(包括模数转换器ADC和数模转换器DAC)、数字信号处理器(DSP)、音频/视频、射频及许多其它混合信号IC中,这一要求相当常见。本质上,包含某种带数字引擎的模拟输入/输出的IC都属于这一类,可能需要特定的电源时序控制。这些IC可能有独立的模拟电源和数字电源,某些甚至还有数字输入/输出电源,详情请参阅下文讨论的具体示例。

本应用笔记讨论设计工程师在新设计中必须考虑的某些更微妙的电源问题,特别是当IC需要多个不同的电源时。目前,一些较常用的电源电压是:+1.8 V、+2.0 V、+2.5 V、+3.3 V、+5 V、−5 V、+12 V和−12 V。

ADI公司在全球销售的产品超过10,000种,但本应用笔记的讨论范围仅限于几款ADC。不过,这些电源时序考虑实际上可以应用于ADI公司的任何混合信号IC。

PULSAR ADC示例——绝对最大额定值

ADI公司的所有数据手册都含有“绝对最大额定值”(AMR)部分,它说明为避免造成破坏,对引脚或器件可以施加的最大电压、电流或温度。

AD7654PulSAR 16位ADC是采用三个(或更多)独立电源的混合信号ADC的范例。这些ADC需要数字电源(DVDD)、模拟电源(AVDD)和数字输入/输出电源(OVDD)。它们是ADC,用于将模拟信号转换成数字代码,因此需要一个模拟内核来处理传入的模拟输入。数字内核负责处理位判断过程和控制逻辑。I/O内核用于设置数字输出的电平,以便与主机逻辑接口(电平转换)。ADC的电源规格可以在相应数据手册的“绝对最大额定值”部分找到。表1摘自AD7654 (Rev. B)数据手册的“绝对最大额定值”部分。

| 参数 | 值 |

| 模拟输入 | |

| INAx, INBx, REFx, INxN, REFGND | AVDD + 0.3 V 至AGND − 0.3 V |

| 地电压差 | |

| AGND, DGND, OGND | ±0.3 V |

| 电源电压 | |

| AVDD, DVDD, OVDD | −0.3 V 至 +7 V |

| AVDD 至 DVDD, AVDD 至 OVDD | ±7 V |

| DVDD 至 OVDD | −0.3 V 至 +7 V |

| 数字输入 | −0.3 V 至 DVDD + 0.3 V |

注意,表1中所有三个电源的范围都是−0.3 V至+7 V。相对于DVDD和OVDD,AVDD的范围是+7 V至−7 V,这就确认了AVDD和DVDD无论哪一个先上电都是可行的。此外,AVDD和OVDD无论哪一个先上电也是可行的。然而,DVDD与OVDD之间存在限制。技术规格规定,OVDD最多只能比DVDD高0.3 V,因此DVDD必须在OVDD之前或与之同时上电。如果OVDD先上电(假设5 V),则DVDD在上电时比OVDD低5 V,这不符合“绝对最大额定值”要求,可能会损坏器件。

模拟输入INAx、INBx、REFx、INxN和REFGND的限制是:这些输入不得超过AVDD + 0.3 V或AGND − 0.3 V。这说明,如果模拟信号或基准电压源先于AVDD存在,则模拟内核很可能会上电到闩锁状态。这通常是一种无损状况,但流经AVDD的电流很容易逐步升至标称电流的10倍,导致ADC变得相当热。这种情况下,内部静电放电(ESD)二极管变为正偏,进而使模拟电源上电。为解决这个问题,输入和/或基准电压源在ADC上电时应处于未上电或未连接状态。

同样,数字输入电压范围为−0.3 V至DVDD + 0.3 V。这说明,数字输入必须小于DVDD + 0.3 V。因此,在上电时,DVDD必须先于微处理器/逻辑接口电路或与之同时上电。与上述模拟内核情况相似,这些引脚上的ESD二极管也可能变为正偏,使数字内核上电到未知状态。

AD7621、AD7622、AD7623、AD7641和AD7643等PulSAR ADC速度更快,是该系列的新型器件,采用更低的2.5 V电源(AD7654则采用5 V电源)。AD7621和AD7623具有明确规定的上电序列。表2摘自AD7621 (Rev. 0)数据手册的“绝对最大额定值”部分。

| 参数 | 额定值 |

| 模拟输入/输出 | |

|

IN+, IN−, REF, REFBUFIN, TEMP, INGND, REFGND to AGND |

AVDD + 0.3 V 至 AGND − 0.3 V |

| 地电压差 | |

| AGND, DGND, OGND | ±0.3 V |

| 电源电压 | |

| AVDD, DVDD | –0.3 V 至 +2.7 V |

| OVDD | –0.3 V 至 +3.8 V |

| AVDD 至 DVDD | ±2.8 V |

| AVDD 至 OVDD | +2.8 V 至 −3.8 V |

| OVDD 至 DVDD | ≤ +0.3 V(如果DVDD < 2.3 V) |

| 数字输入 | −0.3 V 至 +5.5 V |

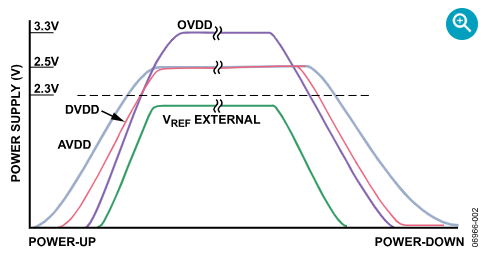

同样,OVDD与DVDD之间存在限制。“绝对最大额定值”规定:OVDD必须小于或等于DVDD + 0.3 V,而DVDD则必须小于2.3 V。一旦DVDD在上电期间达到2.3 V,该限制便不再适用。如果不遵守该限制,AD7621(和AD7623)可能会受损(见图1)。

图1. 可能的上电/关断序列—AD7621 (Rev. 0)

因此,一般上电序列可能是这样的:AVDD、DVDD、OVDD、VREF。但是,每个应用都不一样,需要具体分析。注意,器件关断与器件上电同样重要,切记遵守同样的规格要求。图1所示为AD7621的典型上电/关断序列。

对于这些ADC,模拟输入和基准电压源的情况与上文所述相同。对任何模拟输入引脚施加电压都可能导致ESD二极管变为正偏,从而使模拟内核上电到未知状态。

这些ADC的数字输入和输出略有不同,因为这些器件应支持5 V数字输入。这些ADC是AD7654的速度升级版本,数字输入和输出均与OVDD电源相关,因为它能支持更高的3.3 V电压。注意:数字输入限制为5.5 V,而AD7654则为DVDD + 0.3 V。

Σ-Δ型ADC示例

AD7794Σ-Δ型24位ADC是另一个很好的例子。表3摘自AD7794 (Rev. D)数据手册的“绝对最大额定值”部分。

| 参数 | 额定值 |

| AVDD 至 GND | −0.3 V 至 +7 V |

| DVDD 至 GND | −0.3 V 至 +7 V |

| 模拟输入电压至GND | −0.3 V 至 AVDD + 0.3 V |

| 基准输入电压至GND | −0.3 V 至 AVDD + 0.3 V |

| 数字输入电压至GND | −0.3 V 至 DVDD + 0.3 V |

| 数字输出电压至GND | −0.3 V 至 DVDD + 0.3 V |

该ADC的问题与基准电压有关,它必须小于AVDD + 0.3 V。因此,AVDD必须先于基准电压或与之同时上电。

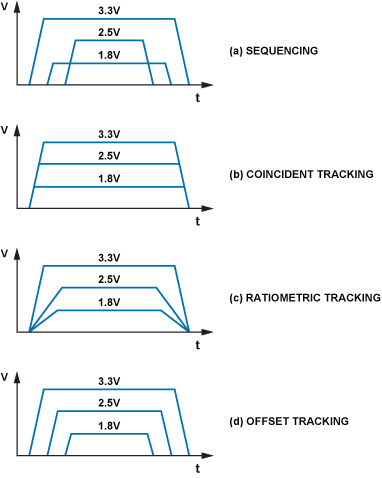

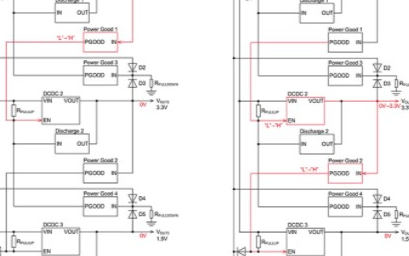

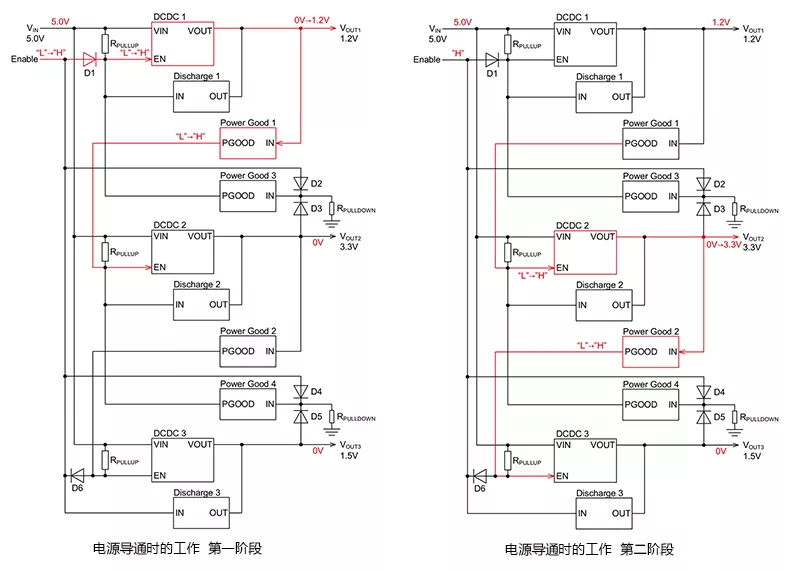

电源时序控制器

ADI公司提供许多电源时序控制器件。一般而言,其工作原理是:当第一个调节器的输出电压达到预设阈值时,就会开始一段时间延迟,延迟结束后才会使能后续调节器上电。关断期间的程序与此相似。时序控制器也可以用于控制电源良好信号等逻辑信号的时序,例如:对器件或微处理器施加一个复位信号,或者简单地指示所有电源均有效。欲了解ADI公司的电源时序控制器,请访问:http://www.analog.com/sequence。

建议

如今大部分要求高速和低功耗的电路PCB上都需要多个电源,例如:+1.8 V、+2.0 V、+2.5 V、+3.3 V、+5 V、−5 V、+12 V和−12 V。为PCB上的这些电源供电并不是一件轻而易举的事情。必须仔细分析,设计一个正确可靠的上电和关断序列。采用分立设计变得越来越困难,解决之道就是采用电源时序控制IC,只要改变一下代码就能改变上电顺序,而不用变更PCB布局布线。

审核编辑:郭婷

-

电源

+关注

关注

184文章

17715浏览量

250124 -

集成电路

+关注

关注

5388文章

11545浏览量

361789 -

soc

+关注

关注

38文章

4165浏览量

218236

发布评论请先 登录

相关推荐

AN-932: 电源时序控制

AN-932: 电源时序控制

评论