Q.我需要数据转换器来适应狭小的空间,我怀疑串行接口会有所帮助。我需要知道什么才能选择和使用一个?

A.让我们首先看看串行接口的工作原理,然后将其与并行接口进行比较。通过这样做,我们将消除一些关于串行数据转换器的神话。

图中所示为连接到ADSP-7890数字信号处理器(DSP)串行端口的8通道多路复用12位串行模数转换器(ADC)AD2105。图中还显示了DSP用于与ADC通信的时序。构成转换结果的12位作为串行数据流通过单行传输。数据流还包括三个额外的位,用于标识AD7890多路复用器当前选择的输入通道。为了区分串行数据流的位,必须提供时钟信号(SCLK),通常由DSP提供;但是,有时ADC会提供此时钟作为输出。DSP通常(但并非总是)提供一个额外的成帧脉冲,该脉冲在通信开始时激活一个周期,或者如图所示(TFS/RFS)在传输期间处于活动状态。

在本例中,DSP的串行端口用于对ADC中的内部5位寄存器进行编程。寄存器的位控制诸如选择要转换的通道、将器件置于省电模式以及开始转换等功能。很明显,在这种情况下,串行接口必须是双向的。

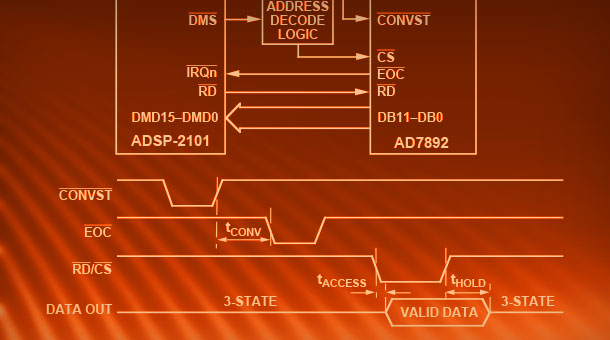

另一方面,并行ADC直接(或可能通过缓冲器)连接到与其接口的处理器的数据总线。图中显示了与ADSP-7892接口的AD2101。转换完成后,AD7892中断DSP,DSP通过单次读取ADC的解码存储器地址来响应。

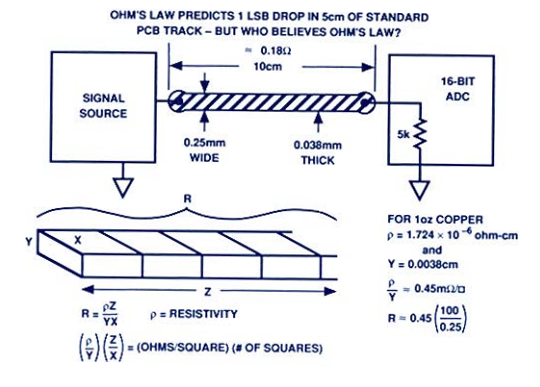

串行和并行数据转换器之间的主要区别在于所需的接口线数量。从节省空间的角度来看,串行转换器具有明显的优势,因为减少了器件引脚数。这样就可以将12位串行ADC或DAC封装在8引脚DIP或SO封装中。更重要的是,由于串行接口连接需要更少的PCB走线,因此节省了电路板空间。

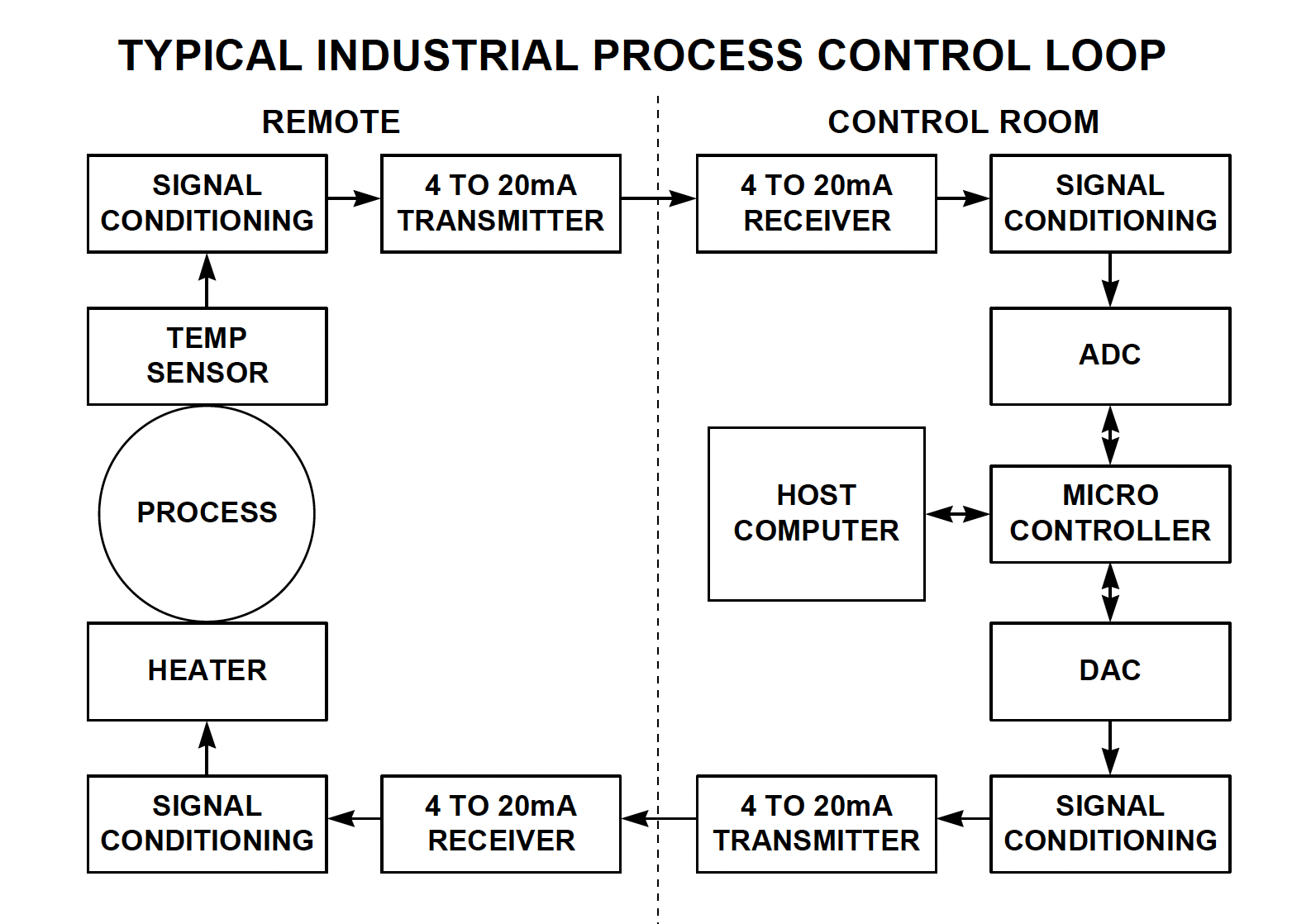

Q.我的数模转换器必须在物理上远离中央处理器,并且彼此远离。解决这个问题的最佳方法是什么?

A.最初,您必须决定是使用串行DAC还是并行DAC。使用并行 DAC,您可以将每个 DAC 映射到内存映射的 I/O 位置,如图所示。然后,只需对适当的 I/O 位置执行写入命令即可对每个 DAC 进行编程。但是,这种配置有一个明显的缺点。它需要一条并行数据总线以及一些控制信号,连接到所有远程位置。显然,可以只有两根电线的串行接口更经济。

串行转换器通常不能映射到处理器的内存中。但是许多串行DAC可以连接到处理器的串行I / O端口。然后,处理器上的其他端口可用于生成芯片选择信号,以单独启用DAC。片选信号需要从每个器件到接口的线路。但是处理器上可以配置为传输芯片选择信号的线路数可能存在限制。

解决此问题的一种方法是使用可以菊花链连接在一起的串行DAC。该图显示了如何将多个DAC连接到单个I/O端口。每个DAC都有一个串行数据输出(SDO)引脚,该引脚连接到链中下一个DAC的串行数据输入(SDI)引脚。LDAC 和 SCLK 并联馈送到链中的所有 DAC。由于时钟输入SDI的数据最终出现在SDO(N个时钟周期后),因此单个I/O端口可以寻址多个DAC。但是,端口必须输出长数据流(每个DAC的N位乘以链中的设备数量)。这种配置的最大优点是不需要设备解码。所有设备实际上都位于同一 I/O 位置。菊花链的主要缺点是可访问性(或延迟)。为了改变单个DAC的状态,处理器仍必须从I/O端口输出完整的数据流。

Q.如果串行数据转换器节省了如此多的空间和电线,为什么它们不能用于每个空间敏感型应用?

A.串行接口的一个主要缺点是速度与空间的权衡。例如,要对并行DAC进行编程,只需将数据放在数据总线上,然后用单个脉冲将其时钟输入DAC。但是,当写入串行DAC时,这些位必须按顺序输入(N位转换器为N个时钟脉冲),然后是负载脉冲。处理器的 I/O 端口花费相对较大的时间与串行转换器通信。因此,吞吐速率高于500 ksps的串行转换器并不常见。

Q.我的 8 位处理器没有串行端口。有没有办法将AD12等串行7893位ADC连接到处理器的并行总线?

A.当然,可以使用外部移位寄存器来完成,该寄存器串行(和异步)加载,然后时钟进入处理器的并行端口。但是,如果问题的意义是“没有外部逻辑”,则可以像1位并行ADC一样连接串行ADC。将转换器的 SDATA 引脚连接到处理器的数据总线线路之一(它连接到图中的 D0)。使用一些解码逻辑,可以将转换器映射到处理器的存储器位置之一,以便可以使用 12 个连续的 Read 命令读取转换结果。然后,其他软件命令将读取的 12 字节的 LSB 集成到单个 12 位并行字中。

这种技术有时被称为“位敲击”,从软件的角度来看效率非常低。但在处理器运行速度比转换器快得多的应用中,这可能是可以接受的。

Q.在最后一个示例中,处理器写入信号的门控版本用于在AD7893上开始转换。这种方法有问题吗?

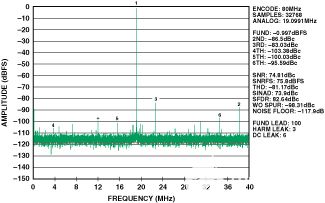

A.我很高兴你发现了这一点。在本例中,可以通过对AD7893的映射存储器位置进行虚拟写入来启动转换。不交换数据,但处理器提供开始转换所需的写入脉冲。从硬件的角度来看,这种配置非常简单,因为它避免了生成转换信号的需要。但是,不建议将该技术用于必须定期对信号进行采样的交流数据采集应用。即使处理器被编程为定期写入ADC,写入脉冲上的相位抖动也会严重降低可实现的信噪比(SNR)。门控过程可能会使写入信号抖动更加严重。例如,采样时钟相位抖动电平仅为1 ns,会使理想的100 kHz正弦波的SNR降低到约60dB(小于10 dB有效分辨率)。还有一个额外的危险,即采样信号上的过冲和噪声会进一步降低模数转换的完整性。

Q.什么时候应该选择异步串行接口的转换器?

A.异步链路允许设备相互交换未计时的数据。设备最初必须编程为使用相同的数据格式。这涉及设置特定的数据速率(通常以波特或每秒比特数表示)。一项规定如何启动和结束传输的公约也是必要的。我们使用称为开始位和停止位的可识别数据序列来做到这一点。传输还可能包括便于错误检测的奇偶校验位。

该图显示了AD1B60数字化信号调理器如何连接到PC的异步COM端口。这是一个 3 线双向接口(为清楚起见,省略了接地线)。请注意,接收和传输线路在线路的另一端交换角色。

异步数据链路在设备仅偶尔通信的应用程序中非常有用。由于每次传输都包含开始位和停止位,因此设备可以随时通过简单地输出其数据来启动通信。设备之间的连接数量减少,因为不再需要时钟和控制信号。

Q.我正在考虑的ADC数据手册建议在串行接口上使用非连续时钟。为什么?

A.该规范可能要求在转换过程中时钟保持非活动状态。一些ADC之所以需要这样做,是因为连续数据时钟会馈入器件的模拟部分,并对转换的完整性产生不利影响。如果I/O端口具有成帧脉冲,则在转换期间可以中断连续时钟信号;它用作门控信号,仅在数据传输期间使串行时钟连接到转换器。

Q.是什么使器件与SPI或MICROWIRE兼容?

A.SPI(串行外设接口)和MICROWIRE是分别由摩托罗拉和美国国家半导体开发的串行接口标准。大多数同步串行转换器可以很容易地连接到这些端口;但在某些情况下,可能需要额外的“胶水”逻辑。

问:好的我决定抛开偏见,在当前的设计中使用串行ADC。我刚刚按照数据表的规定将其连接起来。当我的微读取转换结果时,ADC似乎总是输出FFFHEX。发生了什么事情?

A.也许您遇到了通信问题。我们需要查看ADC和处理器之间的连接,以及时序和控制信号是如何设置的。我们还需要查看中断结构。下一期将回到这个问题,讨论设计串行接口时遇到的问题。

审核编辑:郭婷

-

dsp

+关注

关注

552文章

7962浏览量

348289 -

接口

+关注

关注

33文章

8511浏览量

150850 -

adc

+关注

关注

98文章

6438浏览量

544119

发布评论请先 登录

相关推荐

数据转换器的工程师指南

ADI高级系统应用工程师Rob Reeder专访

模数转换器应用中国工程师百问

应用工程师咨询:宽带A/D转换器前端设计注意事项II

应用工程师咨询:串行转换器的接口-II

咨询应用工程师:关于Wire

应用工程师咨询:串行转换器接口

应用工程师咨询:串行转换器接口

评论