Q.在上一期的讨论结束时,我在ADC和微控制器之间建立通信时遇到了问题。如果您还记得,无论模拟输入上的电压如何,微控制器似乎总是在读取FFF(HEX)的转换结果。可能是什么原因造成的?

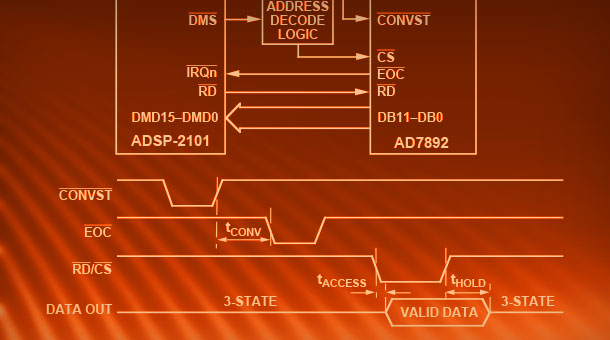

A. 有许多可能与计时相关的错误源。您可以通过将所有定时信号连接到逻辑分析仪或多通道示波器(至少需要三个通道才能同时查看所有信号)来开始解决此问题。您在屏幕上看到的内容类似于下图中的时序图。首先确保正在生成启动转换命令 (CONVST)(来自微振荡器或独立振荡器)。一个常见的错误是应用极性错误的CONVST信号。转换仍会执行,但不会在您期望时执行。同样重要的是要记住,CONVST信号通常有一个最小脉冲宽度要求(通常约为50 ns)。来自快速微处理器的标准写入或读取脉冲可能无法满足此要求。如果太短,可以通过插入软件等待状态来延长脉冲宽度。

确保微在读取周期开始之前等待转换完成。您的软件应该记录转换所需的时间,或者等待ADC的转换结束(EOC)指示器在微中生成中断。确保EOC信号的极性正确,否则ADC将在转换过程中引起中断。如果微处理器没有响应中断,则应检查软件中中断的配置。

同样重要的是,当串行时钟线(SCLK)不寻址转换器时,考虑串行时钟线的状态。正如我在前面的讨论中提到的,某些DAC和ADC不能在连续串行时钟下正常工作。除此之外,某些设备还要求 SCLK 信号始终处于一种特定状态。

问:好的我已经发现并纠正了我的软件中的一些错误,事情似乎正在改善。转换器的数据随着输入电压的变化而变化,但转换结果似乎没有可识别的格式。

A.同样,有许多可能的错误源。ADC将以直接二进制或二进制补码格式输出其转换结果(BCD数据转换器不再广泛使用)。检查您的微处理器是否配置为接受适当的格式。如果不能将微配置为直接接受二进制补码,您可以通过将数字与 100 进行独占或 . . . .00 二进制。

通常,串行时钟的前沿(上升或下降)将使能数据从ADC流出并进入数据总线。然后,后缘将数据计时到微处理器中。确保微型和ADC在同一约定下工作,并且满足所有建立和保持时间。转换结果恰好是人们期望的一半或两倍,这是一个迹象,表明数据(尤其是MSB)的时钟在错误的边缘。同样的问题在串行DAC中表现为输出电压是预期值的一半或两倍。

驱动转换器的数字信号应该是干净的。除了可能对设备造成长期损坏外,过冲或下冲还会导致转换和通信错误。该图显示了一个具有大过冲尖峰的信号,该信号驱动单电源转换器的时钟输入。在这种情况下,时钟输入驱动PNP晶体管的基极。按照通常的做法,器件的P型基板在内部连接到可用的最负电位 - 在这种情况下,接地。SCLK线路上地下超过0.3伏的偏移足以开始打开N型基极和P型基板之间的寄生二极管。如果这种情况经常发生,从长远来看,可能会导致设备损坏。

在短期内,虽然不会造成损坏,但为通常惰性的基板通电会影响器件中的其他晶体管,并可能导致为每个施加的脉冲检测到多个时钟脉冲。由此产生的抖动在串行转换器中是一个严重的问题,但在并行转换器中则不是一个问题,因为读写周期通常取决于第一个施加的脉冲;后续脉冲将被忽略。但是,如果在转换过程中存在此类信号,串行和并行转换器的噪声性能都会受到影响。

该图显示了如何轻松减少过冲。一个小电阻串联在导致问题的数字线路上。该电阻将与数字输入的寄生电容C(par)结合,形成一个低通滤波器,该滤波器应消除接收信号上的任何振铃。通常建议使用 50W 电阻,但可能需要进行一些实验。如果数字输入的内部电容不足,则可能还需要从输入端增加一个外部电容到地。同样,实验是必要的 - 但一个好的起点是大约10 pF。

Q.您提到时钟过冲会降低转换器的噪声性能。从接口的角度来看,我还能做些什么来获得良好的信噪比吗?

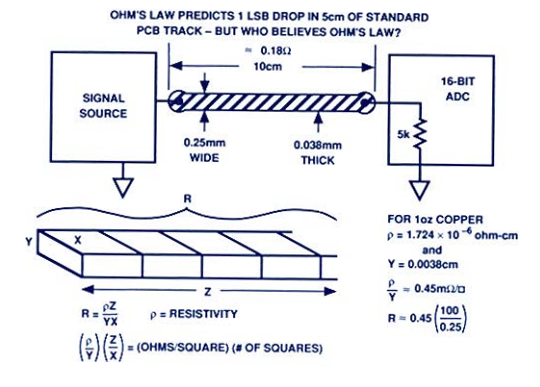

A.由于您的系统在混合信号环境(即模拟和数字)中运行,因此接地方案至关重要。您可能知道,因为数字电路是嘈杂的,因此模拟和数字接地应保持独立,仅在一个点连接。这种连接通常在电源上进行。事实上,如果模拟和数字器件由公共电源供电,例如+5 V或+3.3 V单电源系统,则别无选择,只能将接地连接回电源。但是转换器的数据手册中可能有一条指令,用于连接器件上的引脚AGND和DGND!那么,如何避免在接地连接在两个地方时产生接地环路呢?

下图显示了如何解决这一明显的困境。关键是转换器引脚上的AGND和DGND标签是指这些引脚所连接的转换器部件。整个设备应被视为模拟设备。因此,在AGND和DGND引脚连接在一起后,应该有一个连接到系统的模拟地。诚然,这将导致转换器的数字电流在模拟接地层中流动,但这通常比将转换器的DGND引脚暴露在嘈杂的数字接地层中要小得多。本例还显示了一个数字缓冲器(称为数字地),用于将转换器的串行数据引脚与噪声串行总线隔离开来。如果转换器与微处理器建立点对点连接,则可能不需要此缓冲器。

该图还显示了如何应对使用单个电源为混合信号系统供电的日益常见的挑战。与接地情况一样,我们将单独的电源线(最好是电源层)连接到电路的模拟和数字部分。我们将转换器的数字电源引脚视为模拟。但与模拟电源引脚进行一些隔离(电感形式)是合适的。请记住,转换器的两个电源引脚都应具有单独的去耦电容。数据手册将推荐合适的电容,但一个好的经验法则是0.1 μF。如果空间允许,每个器件还应包括一个 10μF 电容器。

Q.我想使用光隔离器在ADC和微控制器之间设计一个隔离的串行接口。使用这些设备时,我应该注意什么?

A.光隔离器(也称为光耦合器)可用于创建简单且廉价的高压隔离栅。转换器和微型之间存在电流隔离栅也意味着不再需要连接模拟和数字系统接地。如图所示,AD7714精密ADC和常用的68HC11微控制器之间的隔离串行接口只需三个光隔离器即可实现。

但是,设计人员应该意识到,即使串行通信以较慢的速度运行时,将上升和下降时间相对较慢的光隔离器与CMOS转换器一起使用也会引起问题。

CMOS逻辑输入设计为由确定逻辑零或逻辑零驱动。在这些状态下,它们提供和吸收最少量的电流。但是,当输入电压在逻辑零和逻辑一之间转换(0.8 V至2.0 V)时,栅极将消耗更多的电流。如果所使用的光隔离器的上升和下降时间相对较慢,则在死区中花费的时间过长会导致栅极自热。这种自发热倾向于将逻辑门的阈值电压向上移动,这可能导致转换器将单个时钟边沿解释为多个时钟脉冲。为了防止这种阈值抖动,来自光隔离器的线路应使用施密特触发电路进行缓冲,以便为转换器提供快速、锋利的边沿。

审核编辑:郭婷

-

CMOS

+关注

关注

58文章

5685浏览量

235153 -

振荡器

+关注

关注

28文章

3813浏览量

138894 -

微处理器

+关注

关注

11文章

2247浏览量

82326

发布评论请先 登录

相关推荐

数据转换器的工程师指南

ADI高级系统应用工程师Rob Reeder专访

模数转换器应用中国工程师百问

应用工程师咨询:宽带A/D转换器前端设计注意事项II

应用工程师咨询:串行转换器接口

咨询应用工程师:关于Wire

应用工程师咨询:串行转换器的接口-II

应用工程师咨询:串行转换器的接口-II

评论