Noam Levine 和 David Skolnick

到目前为止,我们已经描述了DSP处理器的物理架构,解释了DSP如何提供与传统模拟电路相比的一些优势,并研究了数字滤波,展示了DSP的可编程特性如何适用于此类算法。现在,我们来看看在硬件平台ADSP-2 EZ-Kit Lite&tm;上实现有限脉冲响应(FIR)滤波器算法的过程(在第2100部分中简要介绍,在ADSP-2181系列汇编代码中实现)。该实现已扩展为处理数据 I/O 问题。

使用数字滤波器

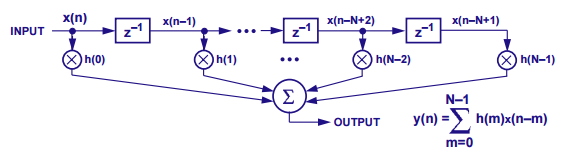

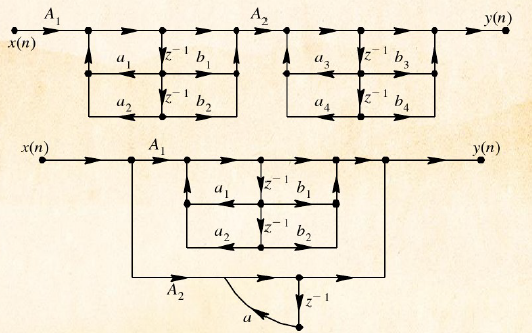

DSP的许多架构特性,例如执行零开销环路的能力,以及在单个处理器周期中获取两个数据值的能力,对于实现此滤波器非常有用。简要回顾一下,FIR滤波器是一种全零滤波器,它是通过将具有滤波器系数的输入数据点序列进行卷积来计算的。其控制方程和直接形式表示如图1所示。

图1.直接形式的FIR滤波器结构。

在此结构中,每个“z–1“框表示输入数据历史记录的单个增量,采用 z 变换表示法。将每个连续延迟的样本乘以适当的系数值 h(m),并将结果加在一起,生成一个值,表示对应于第 n 个输入样本的输出。延迟元件或滤波器抽头的数量及其系数值决定了滤波器的性能。

滤波器结构通过使用DSP进行计算来建议实现此算法所需的物理元素。对于计算本身,每个输出样本都需要多次等于滤波器长度的乘法累加运算。

输入数据的延迟块和系数值列表需要 DSP 中保留的内存区域来存储数据值和系数。DSP的增强型哈佛架构允许程序员将数据存储在程序存储器和数据存储器中,从而在每个周期内从DSP的内部SRAM执行两次同时存储器访问。通过数据存储器保存传入的样本,程序存储器存储系数值,可以在一个周期内获取数据值和系数值以进行计算。

此 DSP 架构支持使用循环缓冲的程序(在第 2 部分和本期后面的部分中简要讨论)。这意味着地址指针只需要在程序开始时初始化,循环缓冲机制确保指针不会离开其分配的内存缓冲区的边界 - 这是FIR滤波器代码中广泛用于输入延迟线和系数的功能。一旦确定了程序的元素,下一步就是开发DSP源代码来实现算法。

开发 DSP 软件

ADSP-2100系列的软件开发流程包括以下步骤:架构描述、源代码生成、软件验证(调试)和硬件实现。图 2 显示了一个典型的开发周期。

图2.软件开发流程。

架构说明:首先,用户创建运行算法的硬件系统的软件描述。系统描述文件包括系统中的所有可用内存和任何内存映射的外设。以下是使用ADSP-2181 EZ-Kit Lite的此过程示例。

源代码生成:从理论到实践,这一步——将算法思想转化为在DSP上运行的代码——通常是过程中最耗时的步骤。有几种方法可以生成源代码。一些程序员更喜欢用高级语言(如 C)编写算法;其他人更喜欢使用处理器的本机汇编语言。对于程序员来说,C 语言的实现可能更快,但编译的 DSP 代码由于没有充分利用处理器的架构而缺乏效率。

汇编代码通过充分利用处理器的设计,可以产生高效的实现。但是程序员需要熟悉处理器的本机汇编语言。最有效的方法是将C语言与系统的时间关键型数学密集型部分的汇编代码相结合。在任何情况下,程序员都必须了解处理器的系统约束和外设细节。本文中的FIR滤波器系统示例使用ADSP-2100系列的本机汇编语言。

软件验证(“调试”): 此阶段使用称为模拟器的软件工具测试代码生成的结果,以检查程序的逻辑流并验证算法是否按预期执行。模拟器是DSP处理器的模型,它a)提供对所有存储器位置和处理器寄存器的可见性,b)允许用户连续运行DSP代码或一次运行一条指令,c)可以模拟向处理器馈送数据的外部设备。

硬件实现:在这里,代码在真正的DSP上运行,通常分几个阶段:a)在EZ-Kit Lite等评估平台上试用;b) 在线仿真,以及 c) 生产 ROM 生成。试用提供程序操作的快速通过/不通过确定;此技术是本文中使用的实现方法。在线仿真监控系统中的软件调试,其中EZ-ICE等工具可以™控制目标平台上的处理器操作。所有调试完成后,可以生成最终代码的引导ROM;它用作最终的生产实现。

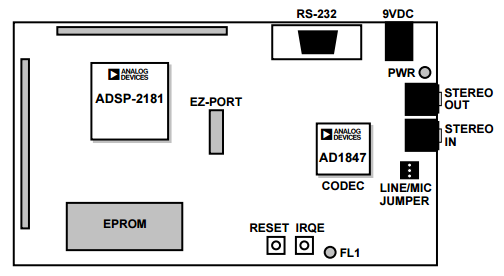

使用ADSP-2181 EZ-Kit Lite

我们的开发周期示例介绍了整个过程,使用ADSP-2181 EZ-Kit Lite(开发包ADDS-21xx- EZLITE)作为滤波器算法的目标硬件。EZ-Kit Lite是一款低成本演示和开发平台,由一个33 MHz ADSP-2181处理器、一个AD1847立体声音频编解码器和一个插座式EPROM组成,后者包含用于通过RS-232连接将新算法下载到DSP的监控代码(图3)。

图3.EZ-Kit Lite 板的布局。

要完成架构描述阶段,需要知道DSP可用的存储器和存储器映射外设。程序员将此信息存储在系统描述文件中,以便开发工具软件可以为目标系统生成适当的代码。EZ-Kit Lite不需要DSP外部的存储器,因为片上可用存储器由ADSP-16的程序存储器(PM)SRAM的384,2181个位置和数据存储器(DM)SRAM的16,352个位置组成。(用于系统控制寄存器的 32 个 DM 位置不可用于工作代码)。有关ADSP-2181、EZ-Kit Lite架构和相关主题的更多信息,请参见本文末尾提到的文本。

可用的系统资源信息记录在系统描述文件中,供ADSP-2100系列开发工具使用。系统描述文件具有.SYS扩展名。以下列表显示了系统描述文件 [EZKIT_LT.SYS]:

.系统EZ_LITE; /* 为这个系统命名 */

.adsp2181; /* 指定处理器 */

.mmap0; /* 指定系统引导,并且 */,

/* PM 位置 0 在内部存储器中 */

.seg/PM/RAM/ABS=0/code/data int_pm[16384];

.seg/DM/RAM/ABS=0 int_dm[16352];

.endsys; /* 结束描述 */

该列表将 PM 的 16,384 个位置声明为 RAM,从地址 0 开始,以便将代码段和数据值都放置在那里。还声明了 16,352 个可用位置的数据存储器作为 RAM,从地址 0 开始。由于这些处理器使用具有两个不同内存空间的哈佛体系结构,因此 PM 地址 0 不同于 DM 地址 0。ADSP-2181 EZ-Kit Lite的编解码器使用串行端口连接到DSP,该串行端口未在系统描述文件中声明。要使系统描述文件可用于其他软件工具,系统组装器实用程序 BLD21 会将.SYS文件转换为体系结构或 。呵呵,文件。系统构建器的输出是一个名为 EZKIT_LT 的文件。哎呀。

编写完代码后,下一步是生成可执行文件,即将代码转换为DSP可以执行的指令。第一个组装DSP代码。这会将程序文件转换为其他开发工具可以处理的格式。汇编还会检查代码是否存在语法错误。接下来,使用体系结构文件中声明的可用内存链接代码以生成 DSP 可执行文件。链接器将源代码中的所有代码和数据放入内存空间;输出是一个DSP可执行文件,可以下载到EZ-Kit Lite板。

生成过滤器代码

本系列的第 2 部分 [模拟对话 31-2,第 14 页,图 6] 介绍了 FIR 滤波器的小型汇编代码列表。在这里,该代码被增强以包含一些特定于 EZ-Kit Lite 的功能,特别是编解码器初始化和数据 I/O。核心滤波器算法元素(乘法累加、使用循环缓冲区对数据和系数进行数据寻址,以及对零开销循环效率的依赖)不会改变。

输入数据将使用板载AD1847编解码器进行采样,该编解码器具有可编程采样速率、输入增益、输出衰减、输入选择和输入混频功能。其可编程特性使系统具有灵活性,但它也增加了编程任务,以便为DSP系统初始化它。

访问数据

在本例中,编解码器的一系列控制字(将在列表第一部分中的程序开头定义)将初始化编解码器,使其具有8 kHz采样率,每个输入通道上的增益值适中。由于AD1847是可编程的,用户通常会重复使用接口和初始化代码段,仅更改不同应用的特定寄存器值。此示例会将特定的筛选器段添加到 EZ-Kit Lite 软件中找到的现有代码段。

此接口代码声明内存中用于数据 I/O 的两个区域:“tx_buf”(用于从编解码器传输出的数据)和“rx_buf”(用于接收传入数据)。这些内存区域或缓冲区中的每一个都包含三个元素:控制或状态字、左通道数据和右通道数据。对于每个采样周期,DSP 将从编解码器接收状态字、左通道数据和右通道数据。在每个采样周期,DSP必须向编解码器提供发射控制字、左声道数据和右声道数据。在此应用程序中,发送到编解码器的控制信息不会更改,因此传输数据缓冲区中的第一个单词将保持原样。我们假设源是使用右声道的单声道麦克风(无需担心左声道输入数据)。

使用EZ-Kit Lite软件中的I / O shell程序,我们只需要参与标有“input_samples”的代码部分。当从准备处理的编解码器接收到新数据时,将访问此部分代码。如果只需要正确的通道数据,我们需要读取位于数据存储器中位置rx_buf + 2的数据,并将其放入数据寄存器中以馈入滤波器程序。

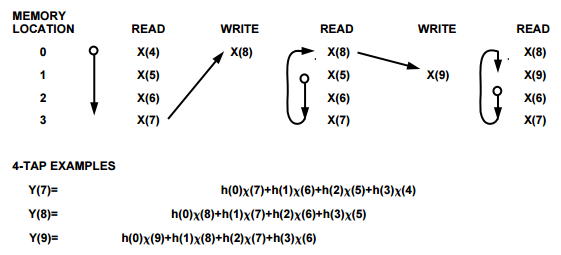

来自编解码器的数据需要使用ADSP-2181的循环缓冲功能通过输入延迟线馈入滤波器算法。输入延迟块的长度由滤波器使用的系数数决定。由于数据缓冲区是循环的,因此缓冲区中最早的数据值将位于上次访问筛选器后指针指向的任何位置(图 4)。同样,每次通过滤波器始终以相同的顺序访问的系数也放置在程序存储器的循环缓冲区中。

图4.对筛选数据使用循环缓冲区的示例 输入。

算法代码

要对接收到的数据进行操作,只需进行少量修改即可使用上一期中发布的代码部分。为了实现这个过滤器,我们需要使用乘法/累加(MAC)计算单元和数据地址生成器。

ADSP-2181的MAC将结果存储在40位寄存器中(32个2位字的乘积为16位,8位允许总和扩展而不会溢出)。这允许中间筛选器值根据需要增长和收缩,而不会损坏数据。使用的代码段是通用的(即,可用于任何长度的过滤器);因此,MAC的额外输出位允许运行具有未知数据的任意过滤器,而不必担心丢失数据。

为了实现FIR滤波器,对滤波器在每个数据点上的所有抽头重复乘法/累加操作。为此(并为下一个数据点做好准备),MAC 指令以循环的形式编写。ADSP-21xx的零开销环路功能允许在指定数量的计数内重复MAC指令,而无需编程干预。计数器设置为抽头数减一,循环机制自动减少每个循环操作的计数器。将循环计数器设置为“taps–1”可确保数据指针在执行完成后最终位于正确的位置,并允许最终 MAC 操作包括舍入。由于AD1847为16位编解码器,因此具有舍入功能的MAC可提供四舍五入到最接近的16位值的统计无偏结果。此最终结果将写入编解码器。

为了获得最佳代码执行,每个指令周期都应执行有意义的数学计算。ADSP-21xxs通过多功能指令实现这一点:处理器可以在同一指令周期内执行多种功能。对于FIR滤波器代码,每个乘法累加(MAC)操作可以与两个数据访问并行执行,一个来自数据存储器,一个来自程序存储器。此功能意味着在每次循环迭代中都会执行 MAC 操作。同时,正在获取下一个数据值和系数,并且计数器会自动递减。所有这些都不会浪费时间维护循环。

当为每个输入数据样本执行滤波器代码时,MAC环路的输出将被写入输出数据缓冲区,tx_buf。虽然该程序仅处理单通道输入数据,但结果将通过写入内存缓冲区地址 tx_buf+1 和 tx_buf+2 写出到两个通道。

最终的源代码列表显示在第 15 页。过滤器算法本身列在“中断服务例程”下。其余代码用于编解码器和 DSP 初始化以及中断服务例程定义。这些主题将在本系列的后续部分中探讨。

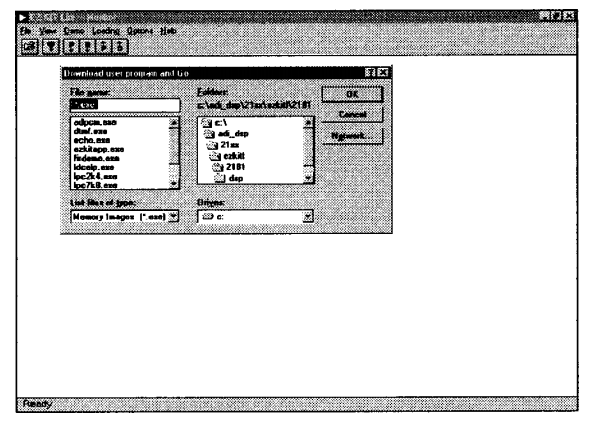

The EZ-Kit Lite

EZ-Kit Lite随附的基于Windows的监控软件可以将可执行文件加载到EZ-Kit Lite板上的ADSP-2181中。这是通过下拉的“加载”菜单选择“下载用户程序并转到”来完成的(图5)。这会将滤波器程序下载到ADSP-2181并开始程序执行。

图5.EZ-Kit 精简版下载菜单。

本文的目的是概述从算法描述到可在硬件开发平台上运行的 DSP 可执行程序的步骤。引入的问题包括软件开发流程、架构描述、源代码生成、数据 I/O 和 EZ-Kit Lite 硬件平台。

与每个主题相关的许多细节级别,这篇简短的文章无法公正地对待。更多信息可在以下参考资料中找到。本系列将继续在此应用程序的基础上构建其他主题。下一篇文章将通过处理器中断结构更详细地研究数据输入/输出 (I/O) 问题,并讨论简单滤波器算法的其他功能。

审核编辑:郭婷

-

处理器

+关注

关注

68文章

19313浏览量

230060 -

dsp

+关注

关注

553文章

8011浏览量

349160 -

滤波器

+关注

关注

161文章

7834浏览量

178266

发布评论请先 登录

相关推荐

[共享] 数字信号处理及其MATLAB实现

如何去使用数字信号处理算法

数字信号处理—理论、算法与实现

数字信号处理的FPGA实现

如何使用FPGA实现数字信号处理算法的研究

数字信号处理:在硬件平台上实现算法

数字信号处理:在硬件平台上实现算法

评论