ADI公司的两款CMOS高速16位过采样A/D转换器,用于在需要低功耗、小尺寸和低成本单芯片解决方案的应用中处理具有宽动态范围的宽带信号。

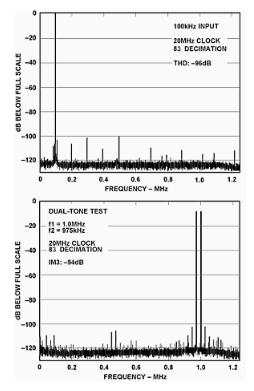

AD9260在20倍过采样模式下使用8 MSPS时钟(图1),能够以16.2 MHz字速率输出5位信号,提供1.01 MHz信号通带、0.004 dB纹波和100 dB SFDR(无杂散动态范围)。AD7723具有19.2 MHz时钟,采用16倍过采样,能够以16.460 MHz输出字速率为1 kHz输入提供2位性能。在要求较低的应用中,为了节省电池容量,AD9260的功耗要求可以从585 mW降至150 mW;AD7723的500 mW功率可以减半。AD7723还具有200 μW待机模式。该表提供了一些额外的比较点。

图1.AD9260 SFDR:单音(100 dB)和双音(95 dB)性能。

两个器件都有内部基准;AD7723提供2.5 V电压,AD9260的基准电压源具有1.0和2.5 V模式。它们采用44引脚QFP封装,AD9260采用MQFP封装,AD7723采用PQFP封装。两款器件均采用+5 V模拟和数字电源供电,但AD9260的数字电源额定工作电压为+3 V,以实现功耗经济性和最小噪声。评估板适用于每种类型。

|

特征 |

AD9260 |

AD7723 |

|

分辨率 |

16 | 16 |

|

采样率,MSPS |

20 | 19.2 |

|

输出数据速率,MSPS @ OSR |

2.5 @ 8× |

1.2 @ 16× |

|

过采样率选择 |

1×, 2×, 4×, 8× |

16×、32× |

|

滤波特性 |

LP |

LP, BP |

|

功耗,mW (最大值) |

630 | 500 |

|

功耗降低,毫瓦 |

至 150 |

50%,200 μW |

|

内部基准,V |

1,2.5 |

2.5 |

|

SFDR,dB(低频信号) |

100 | 90 |

|

信噪比,分贝,1.2 MHz 直通量 |

88.5 类型 |

83 分 |

|

44 引脚封装 |

MQFP |

PQFP |

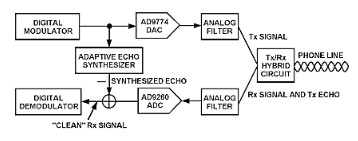

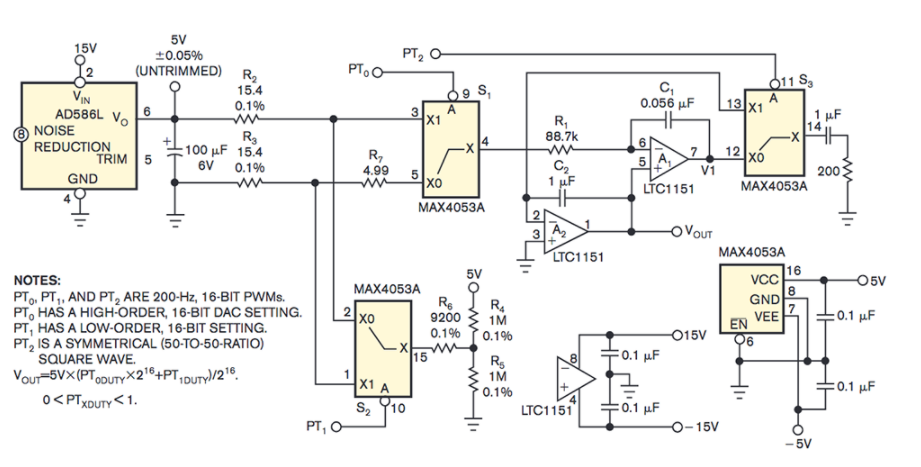

典型应用:宽带宽和高采样率下的16位性能在通信设备中特别有用。一个关键的例子是用于全双工通信的调制解调器中的回声消除,其中共享同一通道以同时发送和接收信号(图 2)。在这种设备中,强发射信号(及其回波)和弱接收信号在时间或频率上可能非常接近。为了使用DSP技术对信号进行分类,必须首先将信号转换为数字信号,而不会损失噪声中的小分量,也不会因失真大分量而产生杂散分量(杂散)。这就要求采用具有高SFDR、低失真(谐波和互调)和低量化噪声的宽动态范围器件。

图2.全双工数字错误消除调制解调器。

AD9260已成功针对有线和无线通信应用进行了评估,例如宽带蜂窝基站、回声消除ADSL调制解调器、单对HDSL调制解调器、导航系统和宽带CDMA基站。这两款器件的高速、动态范围、低功耗、高集成度和低价格使其可用于声纳、无线电、仪器仪表、测试设备以及其他信号捕获和分析应用。当吞吐速率合适时,AD7723的低成本和特殊特性可用于需要待机条件、需要选择串行或并行操作和/或需要16或更高过采样比的带通应用。

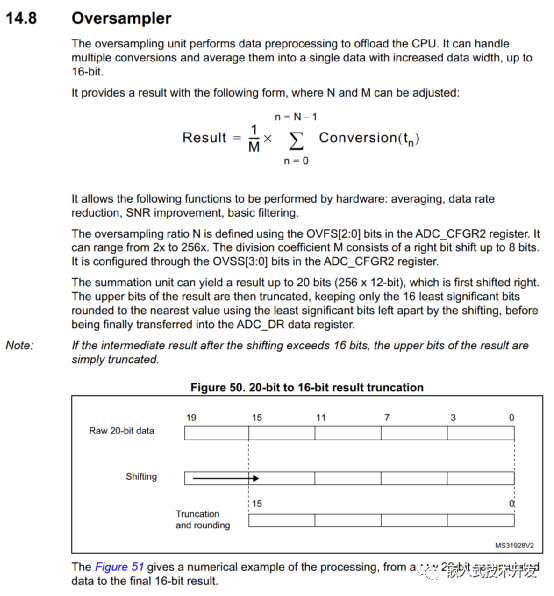

体系结构注意事项

传统上,Σ-Δ A/D转换器以低成本为工业、音频和低频通信应用提供高分辨率,但分辨率和速度之间的权衡通常将带宽限制在200 kHz以下。二阶单位比特调制器可以满足工业市场的高分辨率要求,但代价是过采样比(OSR)大,并且固有地不适合高输出数据速率(ODR)应用。

单环路调制器通常通过增加环路中的积分阶数来增加带宽。例如,使用七阶调制器的AD7722在7 kHz输出数据速率下具有90 dB SNR,时钟频率为195.12 MHz。通过提高此类转换器的ODR速率来提高带宽将很困难,因为这需要更昂贵的制造工艺和能够建立到所需精度的耗电积分放大器。因此,出于实际考虑,单环路单位比特架构的输出数据速率为5-100 kHz。

为了扩展分辨率/带宽边界,需要新的架构。虽然细节超出了本次简要讨论的范围,但值得注意的是,AD9260涉足新领域,以实现最先进的巡回赛解决方案;AD7723成功实现了先进的级联设计方法。我们的大多数Σ-Δ型ADC中使用的单比特DAC虽然保证了出色的失真,但会产生大量量化噪声,从而降低SNR。通过在调制器中使用多位DAC,并采用随机混频技术对DAC的非线性进行随机化,AD9260实现了高分辨率和良好的失真。为了进一步降低量化噪声的影响,在AD9260和AD7723中,首先测量DAC增加的量化噪声,然后以数字方式减去。

特点和性能

AD9260(图3)通过将Σ-Δ技术与高速流水线模数转换器相结合,以适中的8×过采样比实现了高动态范围和极宽输入信号带宽。差分模拟输入被馈入采用2位闪存量化器和5位反馈的二阶Σ-Δ调制器。同时,5位流水线A/D转换器可以更精确地量化闪存转换器的输入。环路架构提供相当于具有 12 位量化器和 12 位反馈的稳定二阶环路,不受空闲音调和其他有时与高阶单比特 Σ-Δ 调制器相关的特性的影响。

图3.AD9260原理框图

调制器输出馈入三级抽取滤波器,MODE控制允许输出旁路任何或所有级,提供时钟速率(1×或抽取2×、4×或8×的输出选择。抽取滤波器的阻带抑制1.25至18.75 MHz之间的频率,大大放宽了模拟输入的抗混叠要求。片内提供带缓冲器的基准电压源。在2.5 V模式(最佳噪声和失真)下,可以处理4 V p-p满量程差分输入。在 1V 模式下,量程为 1.6 V 峰峰值。也可通过外部电阻分压器提供任意可编程值。偏置调整使功耗与时钟速率成比例,从而在时钟速率从20 MSPS降至5 MSPS和585至150 mW时降低功耗(和性能)。

AD7723(图4)使用多个级联一阶和二阶Σ-Δ调制器,每个调制器由一个或多个积分器、一个比较器和一个1位DAC组成。第一个调制器执行实际的模数转换,随后的调制器及其校正逻辑依次消除前一个调制器贡献的量化噪声,同时通过向上移动自己的量化噪声来降低自身的本底噪声。为了满足AD7723的性能要求,采用了5阶噪声整形,导致输出仅包含输入信号和调制器5的4阶整形量化噪声。

图4.AD7723原理框图

AD7723的时钟频率最高可达19.2 MHz。5级FIR抽取滤波器用于降低输出数据速率并消除带外量化噪声。ADC输出可从第4个或第5个滤波器获取。来自第四个滤波器的数据的输出数据速率(ODR)为1.2 MHz,SINAD为85 dB,而来自第五个滤波器的数据的ODR为5 kHz,但SINAD更高,为600 dB。第88个滤波器也可以配置为高通滤波器,使AD5可用作带通ADC。

AD7723提供灵活的串行或并行接口、高过采样率(OSR),以最大限度地降低抗混叠滤波器的复杂性,并接受单极性或双极性输入,以便与输入驱动电路进行简单接口。工作温度范围为 -40 至 +85° C。

审核编辑:郭婷

-

转换器

+关注

关注

27文章

9448浏览量

156963 -

滤波器

+关注

关注

162文章

8467浏览量

186255 -

dac

+关注

关注

44文章

2856浏览量

197603

发布评论请先 登录

ADC的在24位分辨率时的有效位数是多少呢?

ADC的噪声、ENOB及有效分辨率

如何在Δ∑ADC上达到20位分辨率

请问有采样率250MHz左右、分辨率为12位,管脚兼容8位分辨率的adc吗?

AD9260:2.5 MHz输出字率下16位分辨率的高速过采样CMOS ADC数据表

过采样ADC,实现16位分辨率

过采样ADC,实现16位分辨率

评论