Jeff Sondermeyer, Jeritt Kent, Martin Kessler, 和 Rick Gentile

在 1970 年代和 80 年代,高速混合信号设计最常受到数字电路的限制,而不是模拟电路的限制。例如,自10年代以来,ADI公司(ADI)等行业领导者就提供高速并行转换器(>1970 MSPS)。现在,模数转换器和数模转换器(ADC和DAC)正在以更高的采样速率(例如,14位,>50 MSPS)处理高分辨率数据。此外,越来越多的应用需要密集的实时算法。这些因素要求使用更快的可编程通用(GP)数字信号处理器(DSP)来应对高速数据速率带来的挑战。

直到最近,大多数设计人员还必须将高速并行转换器连接到专用IC(ASIC)或快速现场可编程门阵列(FPGA)。像这样的设备能够解决许多所需的同步并行数字操作;但它们通常不灵活,而且可能非常昂贵。现在,随着最近黑鳍金枪鱼的推出™DSP(如ADSP-21535)用户提供可编程通用(GP)16位定点矢量DSP(具有支持300 MHz的内核),可以处理处理来自许多可用高速转换器的数据所需的持续输入/输出(I/O)和内核吞吐量。根据内核时钟频率,可以实现133MHz的最大系统时钟(SCLK)。[此 SCLK 不应与串行外设接口 (SPI) 的串行时钟混淆]。

为什么选择通用DSP?

GP DSP 的成本通常远低于最接近的数字处理对应产品 FPGA 和 ASIC,而且易于编程。此外,由于GP DSP设计周期要短得多,因此上市时间可以更快。对于FPGA/ASIC,用户必须经常聘请或咨询具有专业设计技能的专业人员。他们甚至可能被要求将其知识产权 (IP) 发送到外部,从而给硬件、固件和软件的机密性带来风险。另一方面,GP DSP代码可以存储在只读存储器(ROM)中,也可以屏蔽到DSP中(例如ADSP-2153x系列的成员),从而进一步保护IP。最后,GP DSP是完全可编程的,与ASIC实现相反,在ASIC实现中,每个更改都需要昂贵的重新设计(时间和金钱)。这些因素很容易促使许多工程师考虑将GP DSP作为首选解决方案,特别是当内核速率接近“奔腾级”芯片时。®

ADSP-21535是ADI公司Blackfin系列的首款产品,设计用于在计算机总线环境中实现最佳工作,而即将推出的较新设计(年内)将具有并行外设接口(PPI),专门设计用于处理I/O数据。但是,在此期间,ADSP-21535的电源可以与少量现成的外部电路配合使用,用于无线应用等急需的设计。

存在哪些问题?通常,为了保证足够的数据处理带宽,DSP需要比转换器的采样速率快一个数量级(10倍)的最小时钟速度。反过来,所需的处理带宽量取决于DSP的接口能力,而DSP的接口能力又受到其他几个因素的影响。这些注意事项包括:块处理与样本处理、是否存在直接内存访问 (DMA) 控制器、多端口内存以及是否使用外部 FIFO。幸运的是,ADSP-21535具有独立于内核工作的完整DMA控制器,具有多端口1级(L1)和2级(L2)存储器。内核速度、独立DMA控制器和大型多端口板载存储器(308 KB)相结合,使ADSP-21535能够以高数据速率执行高效的模块处理。例如,如果使用符合修订版 2.2 的 33-MHz、32 位(4 字节)外围组件互连 (PCI) 接口(本应用程序中未显示),则可以实现接近 132 MB/s 的传输带宽。

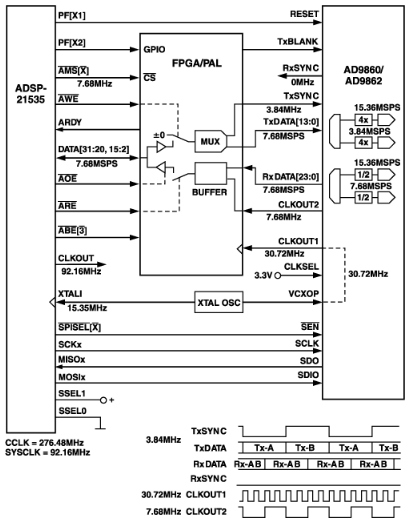

图1.ADSP-21535与AD9860/AD9862之间的外部逻辑连接。

ADSP-21535的外部总线接口单元(EBIU)提供异步(ASYNC)外部存储器接口。如果PCI总线必须用于其他系统通信,则EBIU是将ADSP-21535连接到高速转换器的唯一可用并行接口。将DSP掌握的该端口异步控制与转换器的同步连续数据流相结合,可能会给系统设计人员带来一些挑战。

本文介绍一种特定的硬件实现,它利用低引脚数、低成本、常用的“胶合逻辑”器件,如可编程阵列逻辑芯片 (PAL)、复杂可编程逻辑器件 (CPLD) 或 FPGA。该逻辑在AD9860/62混合信号前端(MxFEÔ)和ADSP-21535的异步外部存储器总线之间执行控制功能。图1所示的应用适用于正交频分复用(OFDM)无线便携式终端。ADC 和 DAC 通过 DSP 的异步接口实现分时(时分复用或 TDM)。(此处提供的信息同样适用于其他并行高速ADC和DAC。

工程师对工程师 注意 EE-162 可用,描述了互连方案的详细信息。假设读者手头有关于ADSP-21535和AD9860/2的信息,包括“ADSP-2153x/21535 BlackfinÔ DSP硬件基准”和AD9860/AD9862的数据手册。

设计目标

该项目的早期设计目标之一是最大限度地减少连接DSP和转换器所需的外部控制逻辑量。在成本的驱动下,工程部门希望消除外部逻辑器件中的任何FIFO或存储器。另一个限制是避免通过逻辑路由数据总线,从而减少引脚数量、封装尺寸和逻辑器件的成本。图1所示的初始设计将所有功能(包括数据锁存)组合到单个逻辑器件中。然而,这种设计的量产模型将使用由逻辑器件驱动的廉价三态锁存器。这些锁存器或缓冲器会将从DSP存储器接口的样本多路复用(打包)到12/14位DAC,并将10/12位ADC样本缓冲或解复用(解包)到DSP存储器接口。

设计挑战

任何混合信号/DSP设计的关键因素之一是充分了解器件之间的约束和随之而来的权衡取舍。以下讨论将说明将ADC/DAC与ADSP-21535接口时必须考虑的各种权衡。

一些主要的设计约束是:

该设计的OFDM调制方案驱动了所需的15.36 MSPS转换器采样速率

AD9860/2内置一个双通道、10/12位、64 MSPS ADC和一个双通道12/14位、128 MSPS DAC。

与具有DMA请求和DMA授权(即DMA可以从外部设备控制)的SHARC处理器不同,ADSP-21535只有一组内部存储器DMA通道(memDMA),必须从DSP控制。®

此外,当ADSP-21535异步接口连接到不包含FIFO或存储器的器件时,必须彻底了解所有延迟。例如,每次 memDMA 在突发 8 次传输后放弃总线时,都需要 10 个 SCLK 周期才能开始下一次传输。

未来的Blackfin系列产品将具有DMA控制器的可编程优先级,以及专用的高速并行接口 - 具有DMA请求和DMA授权信号。有了专用的PPI,这些未来的Blackfin产品将不需要异步存储器接口来连接并联转换器。

此处使用的方法假定存储器接口专用于转换器。使用转换器多路复用外部SRAM/SDRAM存储器将很困难,不建议这样做,特别是考虑到只有一个memDMA,并且需要共享。大容量板载L2存储器(256K字节)的存在最大限度地减少了对任何外部存储器的需求。但是,允许在初始引导过程中使用闪存或EPROM多路复用并行转换器。

该设计采用TDM时间片方法在ADC和DAC之间共享外部总线,因为由于单个存储器接口执行读取或写入,并且只有一组memDMA通道(源和目标),因此无法同时访问。

ADSP-21535将支持133 MHz的最大SCLK(峰值DMA带宽)。在此速率下,无需外部FIFO,memDMA可以维持32 MSPS/133的传输(10位字)速率(总线采集需要1个周期,下一次传输需要13个周期)或3.21535 M字/秒。但是,ADSP-1的SCLK源自内核时钟(CCLK)。CCLK反过来通过PLL分频器生成,其可用比率为31比2,并且只有四种可用分频比:0.2、5.3、0.4和0.133。因此,允许 266 MHz SCLK 的 CCLK 和除数的一种可能组合是 CCLK = 2 MHz 和 CCLK/SCLK = 300。但是,如果内核必须以120 MHz运行,例如在此应用中,则可以获得的最高SCLK为2 MHz(除数= 5.133),以保持在最大<> MHz以下。

现在,由于 ASYNC 存储器接口的宽度为 32 位,因此每个字最多可以打包两个 16 位样本(在本例中为 I 和 Q)。这有效地将DSP必须处理的字速率减半(对于15.36 MSPS转换器采样速率,DSP将“看到”7.68 MSPS)。在这些条件下,memDMA支持的最高外部转换器采样速率为2 x 120/10 = 24 MSPS。此外,SCLK必须是转换器采样速率的整数倍,以确保转换器时序和DSP时序之间的正确相位对齐,并且无需任何外部FIFO。因此,ADSP-21535在300 MHz内核速率下支持的最高转换器采样速率为2 x 120/10 M = 24 MSPS,或memDMA速率的两倍,如诫命#10中所述。由于DSP仅以该速率的一半处理打包数据,因此12 MSPS是memDMA可以承受的最大速率,即12 M字/秒。如果转换器和EBIU之间包含小型外部FIFO,则ADSP-21535可以处理更高的采样速率。

表 1.ADSP-21535的可能参数方案。

|

转换器 采样率 (兆字节) |

CCLK (MHz) |

CCLK/SCLK 分率 |

高铁 (兆赫) |

memDMA (Mwrites/s) |

高清晰度/转换器 采样率 |

|

15.360* 24.000 26.600 20.000 15.000 10.000 8.8670 0.8867 企业社会责任 <= 26.6 |

276.48 300 266 300* 300* 300 266 26.6 CCLK < 300 |

3.0 2.5 2.0 3.0 4.0 2.5 2.0 2.0 2.0、2.5、3.0 或 4.0 |

92.16 120 133* 100 75 120 133* 13.30 SCLK < 133 |

9.216 12.0 13.3 10.0 7.5 12.0 13.3 1.33 内存DMA < 13.3 |

6 5 5 5 5 12 15 15* 5 <= 整数 <= 15 |

*表示驱动参数

现在回想一下,OFDM 要求决定了 15.36 MSPS 转换器采样速率。要获得该转换器采样速率的整数倍的SCLK,必须选择锁相环(PLL)乘法器,该乘法器是四个可用除数比(2.0、2.5、3.0或4.0)之一的整数倍。当PLL乘法器为18时,允许的最大CCLK为276.48 MHz。这反过来又将 SCLK 限制为 3 的整数倍,因为 276.48/3 = 92.16 MHz(分频比为 2 将使 SCLK 超过最大值 133 MHz)。在这些约束下,memDMA可以支持的最大持续速率为92.16/10 = 9.21 M字/秒。

DMA 注意事项

必须仔细考虑组合的、必需的、“持续的”DMA 性能。由于 memDMA 是 DMA 总线 (DAB) 上的共享资源,因此在此总线上仲裁其他 DMA 活动。此应用要求串行端口 (SPORT) 上有一个 10 Mbit/s 串行通道,该串行通道还必须针对 DAB 进行仲裁。这将在 625 位/字的 DMA 带宽下额外消耗 16 K 字/秒。ADSP-21535最多可支持133 M字/秒(峰值)DMA带宽,并且SPORT的仲裁优先级高于memDMA(见表1)。因此,SPORT DMA应该有效地利用上述十个周期的延迟,并允许memDMA使用大部分(如果不是全部)9.21 M字/秒。有 9.21M – 15.36 M/2 = 1.53 M 字/秒的额外带宽,这应该提供足够的裕量来维持 7.68 MSPS 速率。

表2:仲裁优先权

| 民建联大师 | 仲裁优先权 |

| 运动0 遥控 DMA 控制器 | 0 - 最高 |

| 运动1 遥控 DMA 控制器 | 1 |

| 运动0 XMT DMA 控制器 | 2 |

| 运动1 XMT DMA 控制器 | 3 |

| USB DMA 控制器 | 4 |

| SPI0 DMA 控制器 | 5 |

| SPI1 DMA 控制器 | 6 |

|

UART0 遥控控制器 |

7 |

| UART1 遥控控制器 | 8 |

| UART0 XMT 控制器 | 9 |

| UART1 XMT 控制器 | 10 |

| 内存 DMA 控制器 | 11 - 最低 |

对ADSP-21535中的DMA引擎的分析揭示了其他一些考虑因素。虽然 DMA 引擎支持两种类型的 DMA 传输(基于描述符和基于自动缓冲区),但 memDMA 控制器不支持基于自动缓冲区的 DMA。因此,必须使用基于描述符的传输。从 L1/L2 内存获取描述符涉及两个 5 字块移动,一个用于源描述符,另一个用于目标描述符。此外,memDMA 具有一个 16 个条目的 32 位 FIFO,该 FIFO 从源填充并从目标清空。如果同时加载两个描述符,则需要从 L39 加载 2 个 SCLK 周期(最坏情况)。目标描述符加载优先于源负载,以避免超出 FIFO。因此,在本例中,同时加载两个描述符所需的时间为 (1/92.16 M) x 39 = 423 ns。从 L2 内存加载描述符时,DMA 引擎描述符加载性能最佳。如果描述符位于 L1 内存中,则存在额外的延迟。来自 L1 的最坏情况源加目标描述符加载时间为 65 个 SCLK 周期。为了在这些采样率下有效地处理数据,通常使用乒乓缓冲器(在此设计中,使用两个1024字缓冲器)。此技术允许将数据填充到一个缓冲区中,而内核处理另一个缓冲区。作为参考,ADI公司提供了完整的VisualDSP++Ô 2.0项目程序。

必须分析两个工作阶段:DSP 必须从 ADC 接收样本(接收器 TDM 相位);并且样本必须从DSP传输到DAC(发射器TDM相位)。

接收器 TDM 相位

在接收机阶段,数据移动方式为:ADC–>EBIU–>(源)–>memDMA–>FIFO–>L1/L2(目的地)。在 15.36MHz 转换器采样速率下,每 32/1.7M = 68.130 ns 就有一个新的 2 位采样到达 DSP。从描述符加载时间延迟(423 ns)可以看出,必须采取一些措施来避免DSP过载和丢失样本。幸运的是,转换器连接到外部总线,并且没有使用地址总线。因此,将样本移动到DSP中时,可以设置最大传输计数为65536字的源描述符,以及具有预期乒乓缓冲传输大小为1024字的目标描述符。这样,每 1024 个字从内核中断一次时,仅重新加载目标描述符,加载时间减少到 20 SCLK x 1/92.16M = 217 ns。如前所述,该设计采用TDM方案,其中ADC和DAC占用单独的时间片。多路复用速率为5至8 ms的可变值。由于ADC和DAC数据是交错的,在最坏的情况下,接口每8 ms从接收器到发射器再回来一次。因此,65536字x 130.2 ns或8.5 ms就足够了,并且只需在每个接收器TDM阶段开始时设置一次源描述符。最后,16 个条目的 memDMA FIFO “隐藏”了目标描述符加载时间,因为当目标描述符从内存加载时,源仍在填充 FIFO。在最坏的情况下,memDMA FIFO只会在重新加载描述符之前积累一些数据样本。然后,这些样本被突增到内存中。因此,无需在接收器侧使用外部FIFO,并且不会丢失任何样本。

发射器 TDM 相位

在传输阶段(数据到DAC),数据移动方向相反:L2/L1(源)–>memDMA–>FIFO–>EBIU (目标)–>DAC。与接收模式不同,源描述符必须每 1024 个单词更新一次。这将需要 20 个 SCLK 周期或 217 ns。但是,由于memDMA(9.21M字/秒)的运行速度略快于采样率(7.68M字/秒),因此在memDMA FIFO中应保持16个样本,这将在描述符加载时馈送DAC。目标描述符传输计数可以固定为 65536 个单词。同样,不需要外部FIFO,也不会丢失样品。

逻辑概述和时序

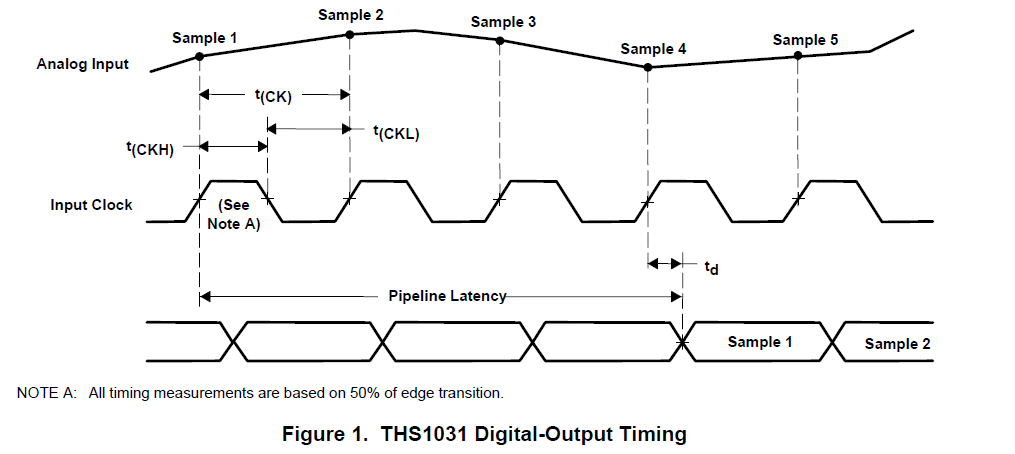

为了避免外部逻辑中需要FIFO,将转换器时钟与DSP系统时钟SCLK同步仍然很重要。这限制了可用的ADSP-21535时钟选项,具体取决于采样速率。至少,SCLK 必须可被转换器采样率整除,并且 CCLK 可能还需要被转换器采样率整除(只有一个非整数除数 2.5 - 在某些情况下可能不可用)。必须使用外部锁存器或缓冲器使来自转换器的数据与DSP的时序对齐(有关采样偏斜和延迟,请参见图2和图3)。四线DSP SPI端口直接连接到AD9860/AD9862 SPI端口。为确保正确的电源排序和初始化,DSP应复位转换器。为了进一步减少外部逻辑的引脚数,AD9860/AD9862的另一个选项(此处未显示)允许将两个10/12位ADC值时间复用到一条10/12位RXDATA总线上。虽然这将消除两条10/12位总线之一,但它需要外部逻辑在将数据传输到DSP之前对数据进行解复用。

所有数据移动都由DSP中的memDMA控制或控制。读取ADC数据时(见图2),必须由外部逻辑驱动数据和ARDY信号。外部逻辑必须对/AOE引脚进行采样,以检查何时可以将数据驱动到ADSP-21535。/AOE 信号向外部逻辑指示 DMA 控制器已准备好获取数据。接收器三态机如图底部所示。

图2.接收计时和状态机。

当数据发送到DAC时(见图3),外部逻辑必须对/AWE信号进行采样,然后驱动ARDY。/AWE 向外部逻辑指示 DMA 控制器何时准备好使用新数据。变送器四态机如图底部所示。

图3.传输定时和状态机。

结论

尽管ADSP-21535并非专门设计用于连接高速并行转换器,但它具有许多其他优点,可用于需要快速上市的设计。具有专用并行外设接口(PPI)的ADSP-BF532等新一代器件将很快推出,以更低的成本为此类应用提供更明确的解决方案。为了满足紧急需求,我们建议使用一种低成本的“无先进先出”解决方案,直到下一代零件批量生产为止。这将使目前的300 MHz ADSP-21535能够与采样速率高达24 MSPS的ADC和DAC接口。如果ADSP-21535内核的时钟频率可以专门定时为266 MHz,则最高转换器采样速率仅受ADSP-21535可以支持的最大SCLK(133 MHz)和突发间10周期memDMA延迟的限制:2 x 133 M/10 = 26.6 MHz。

审核编辑:郭婷

-

FPGA

+关注

关注

1630文章

21763浏览量

604524 -

转换器

+关注

关注

27文章

8734浏览量

147507 -

asic

+关注

关注

34文章

1205浏览量

120589

发布评论请先 登录

相关推荐

如何用TIFIFOS和TMS320DSP实现高速数据转换器接口的英文资料概述

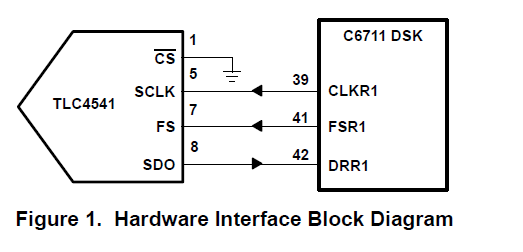

如何将TLC4541模数转换器连接到TMS320C6711 DSP的方法详细概述

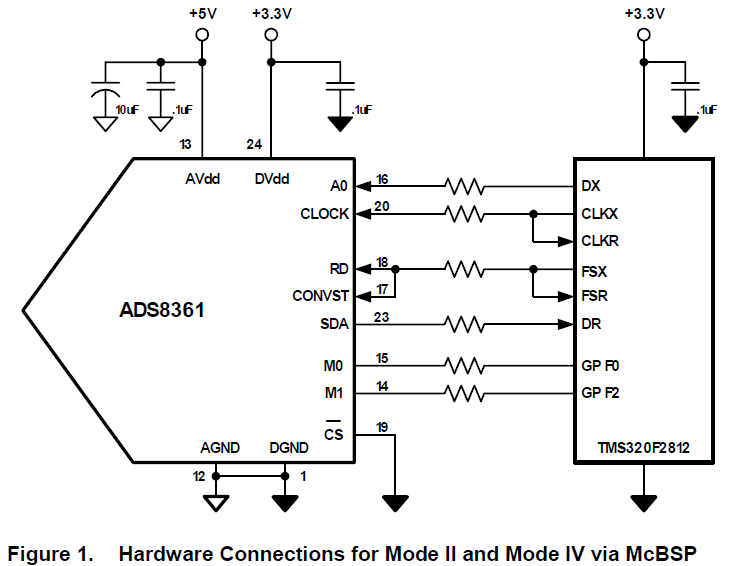

几种将ADS8361数字转换器连接到TMS320F2812 DSP的方法的详细概述

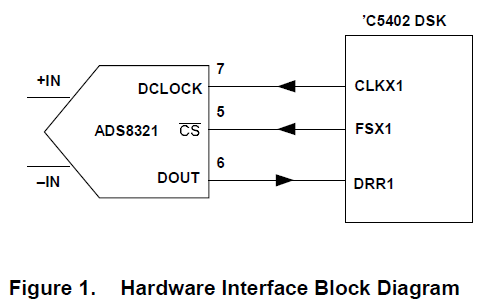

如何将ADS8320模数转换器连接到TMS320C5402 DSP的方法详细概述

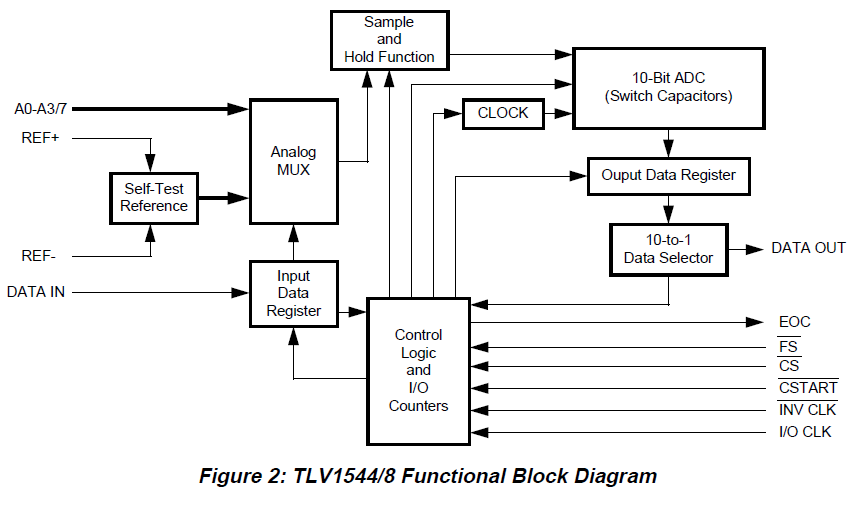

将AD转换器连接到DSP和MCU的软硬件要求详细概述

EE-258:将Micron MT9V022图像传感器连接到Blackfin®处理器

EE-300:将Blackfin®EZ-KIT Lite®板连接到CMOS图像传感器

EE-302:将ADSP-BF53x Blackfin®处理器连接到NAND闪存

EE-234:通过串行端口将T1/E1收发器/成帧器连接到Blackfin®处理器

EE-162:通过外部存储器总线将ADSP-BF535 Blackfin处理器连接到高速转换器(如AD9860/2上的转换器)

EE-321:将Blackfin处理器连接到AD7656 SAR ADC

EE-245: AD7276高速数据转换器与ADSP-BF535 Blackfin处理器的接口

EE-162:通过外部存储器总线将ADSP-BF535 Blackfin处理器与高速转换器连接

将Blackfin DSP连接到无线应用的高速转换器

将Blackfin DSP连接到无线应用的高速转换器

评论