上拉和下拉电阻是许多数字电路的组成部分。了解什么是上拉电阻或下拉电阻很重要?为什么将其用于数字电路?以及如何选择这些的价值?本文将回答这三个问题,并让您更好地了解它。

什么是上拉或下拉电阻:

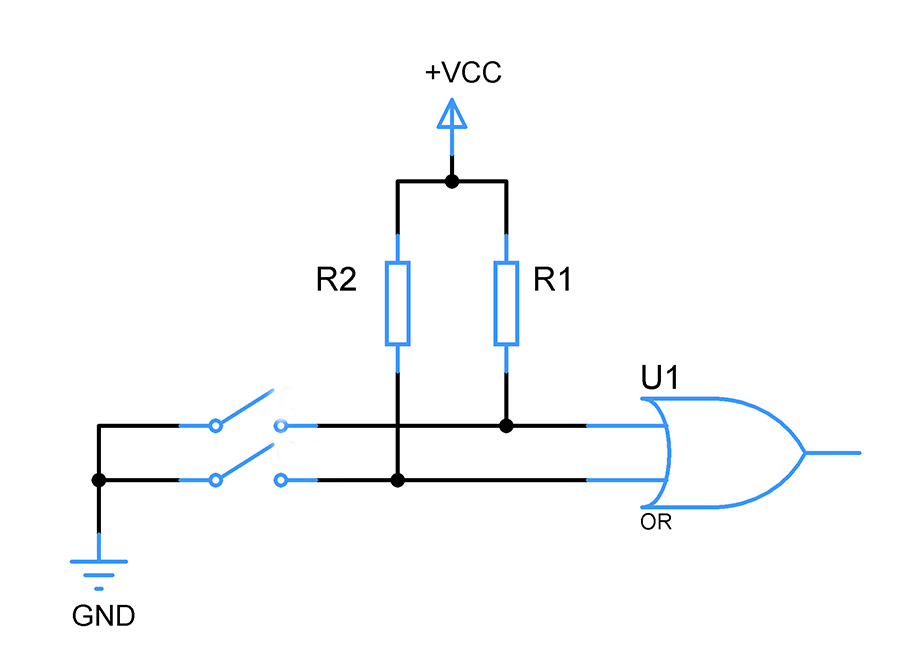

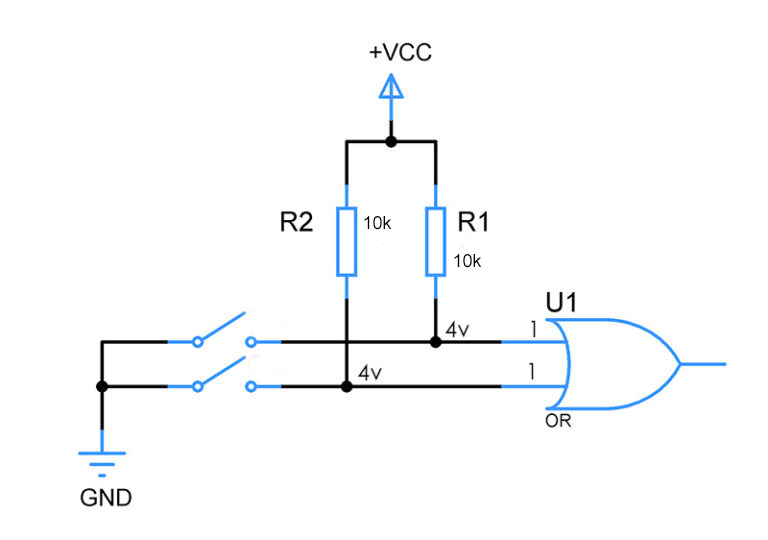

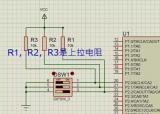

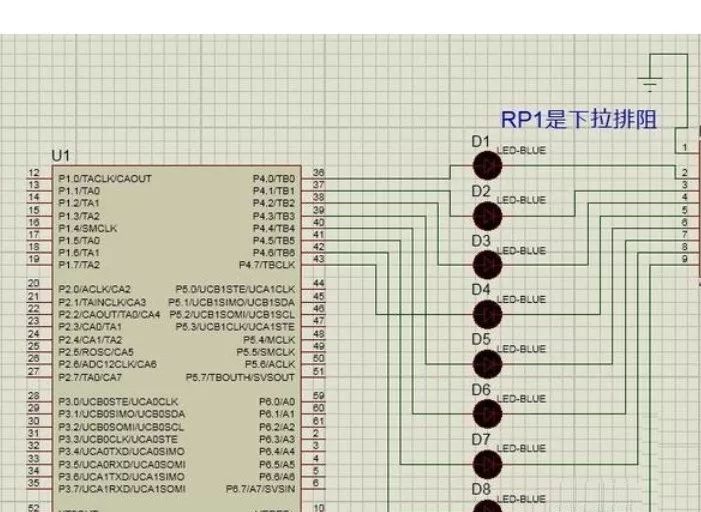

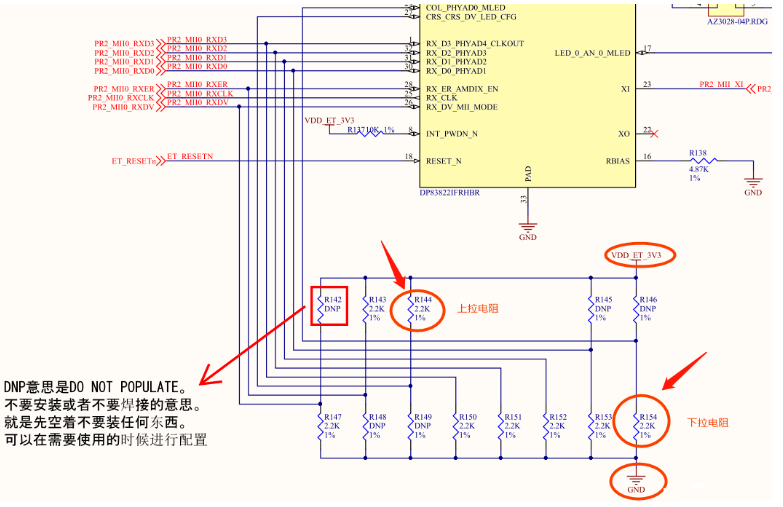

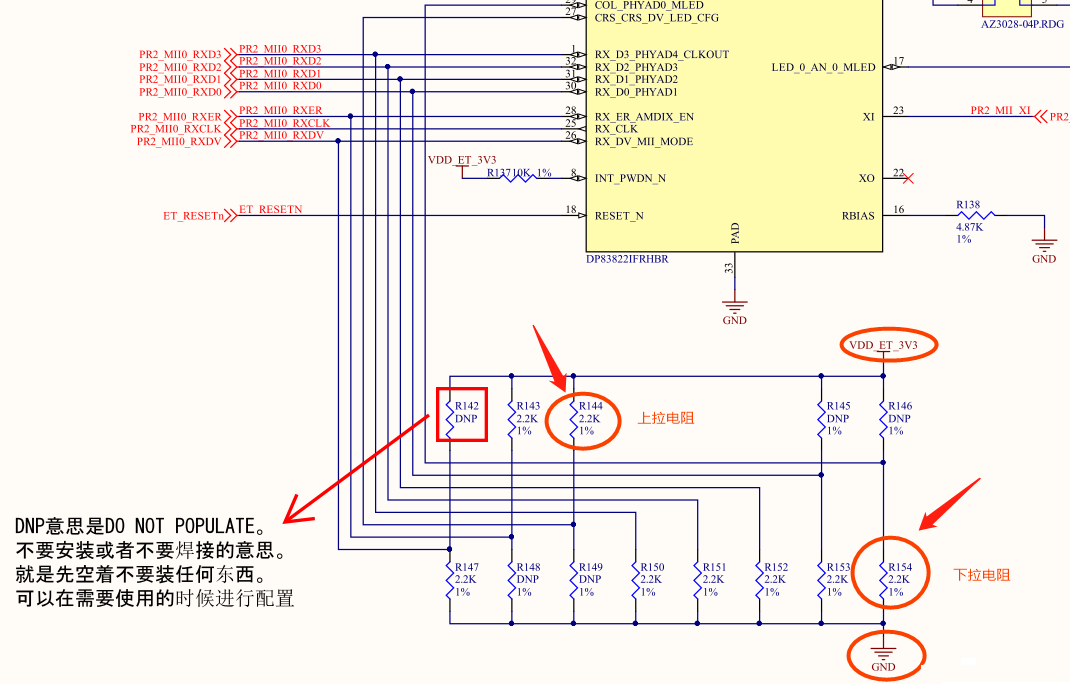

这些是将数字输入引脚连接到VCC或接地的常用电阻器。这些电阻的目的是调出相当于地或VCC电压的输入引脚。参考上面的电路图,电阻R1和R2是上拉电阻。这些电阻将输入引脚的电压拉高到VCC电平。

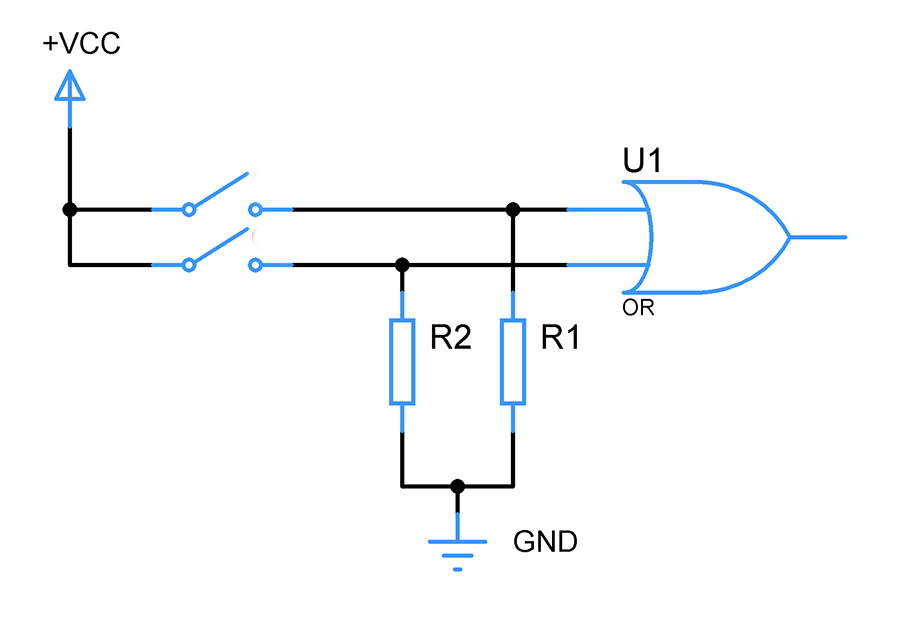

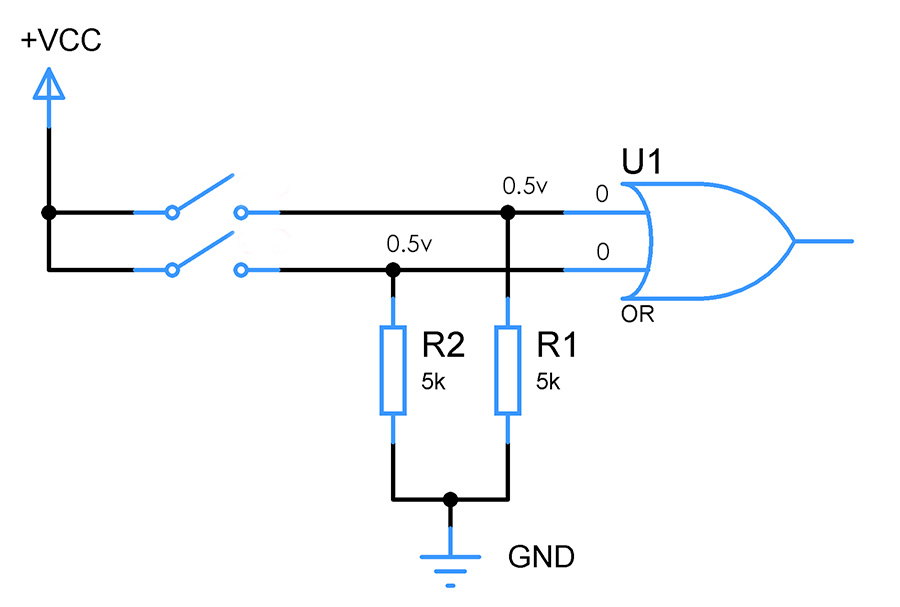

现在看上面的电路图,这里的电阻R1和R2充当下拉电阻。这些电阻将输入引脚的电压下拉至接近GND电平。

为什么使用上拉或下拉电阻:

简而言之,上拉或下拉电阻的目的是使数字引脚的输入保持在稳定状态 - 上拉电阻为1,下拉电阻为0。为了进一步解释这一点,我们需要了解 Logic

家族以及每个家族之间的区别。

逻辑电平:

逻辑电平只不过是决定数字电路中的输入或输出如何解释为“1”(高状态)或“0”(低状态)的电压范围。数字系统中存在许多逻辑家族。TTl,CMOS,RTL,DTL是少数几个系列,其中TTL和CMOS非常有名且常用。

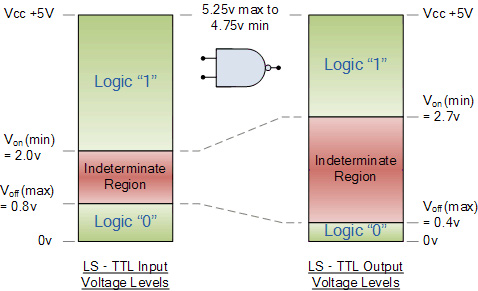

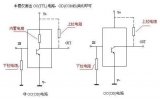

上图显示了+5VccTTL逻辑系列的逻辑电平图。正如您在输出图和输入图中观察到的那样,每种逻辑状态都有一个电压范围。参考输入电压电平,您可以观察到

栅极读取逻辑 1 – 输入电压范围必须在 2v 至 5v 之间

栅极读取逻辑 0 – 输入电压范围必须在 0 至 0.8v 之间

不确定区域是陷阱,这意味着当输入电压从0.8到2v之间时,栅极将无法理解它,并且它将以不希望的方式起作用。输出可以是 0 或

1,我们无法预测它们。

最后一种情况对于设计数字电路来说太糟糕了,因为它可能会使整个电路失效,而您的设计将毫无用处。

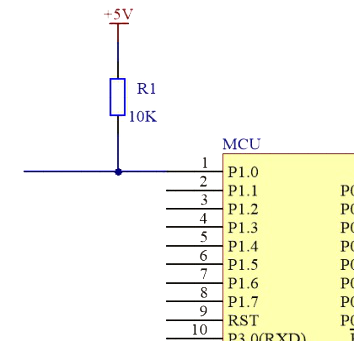

浮动状态:

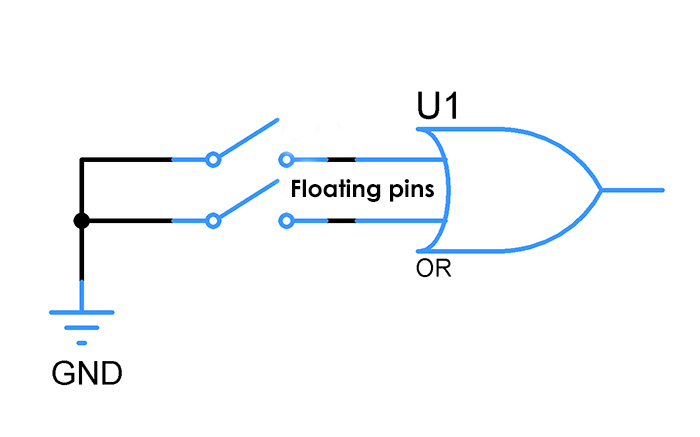

现在看一下上面的电路,其中开关连接到OR门的输入引脚。当开关未连接时,引脚被称为浮动状态,这意味着其中没有显示定义的电压。在这个瞬间,来自周围的电噪声或电磁波会在这些引脚中感应出一些电压,因此输入电压很有可能落入0.8至2v的不确定区域,从而推动我们的整个系统失效。在最坏的情况下,噪声和电磁波会产生波动的电压,使整个系统不稳定。

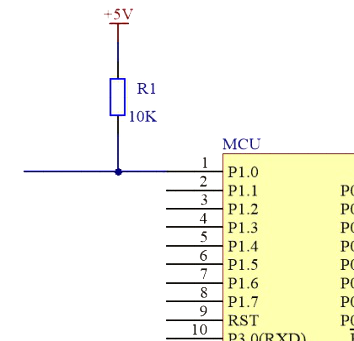

为了摆脱上述情况,请在两个输入引脚上添加一个电阻,并将它们连接到Vcc。通过这样做,输入引脚电压将被上拉,电压将几乎等于Vcc。这使得逻辑门检测输入电压作为逻辑1并采取相应的行动。

计算电阻值:

每个数字输入引脚都会消耗一些电流,并具有一些内部阻抗。由于这些原因,这些上拉电阻两端存在压降。因此,在选择电阻值时,我们应该确保

电阻不要太高,因此输入引脚不会有足够的电流工作

太小,以至于多余的电流流过并导致短路。

上拉电阻:

假设OR门的数字引脚在+100Vcc时消耗5uA电流。为了选择电阻器,我选择了4v作为上拉电压,因为它会从2v提供一些不错的空间,超出该空间是不确定的区域。您不能选择5v,因为如上所述,电阻器两端会有一些压降,因此选择低于Vcc电平是安全的。

应用欧姆定律和这些值,

R = 5 – 4 / 100uA

= 1 / 100uA

= 10科姆

下拉电阻:

对于上述100uA的消耗电流,我将选择0.5v的下拉电压,因为它从0.8v提供了一个空间,高于该空间的输入进入不确定区域。在这里应用欧姆定律将得到电阻值

R = 0.5V / 100uA

= 5科姆

注意:

查看数据手册,了解数字芯片的输入电流和输入阻抗,并执行上述计算,为您的数字电路找到完美的上拉或下拉电阻。

切勿尝试在没有电阻的情况下尝试上述设置,您最终会短路电源,因为没有电阻器关闭开关会导致电流过大,因为没有阻抗可用。

-

上拉电阻

+关注

关注

5文章

366浏览量

31746 -

下拉电阻

+关注

关注

4文章

154浏览量

21443 -

数字电路

+关注

关注

193文章

1669浏览量

83590

发布评论请先 登录

什么是上拉或下拉电阻?为什么使用上拉或下拉电阻?

什么是上拉或下拉电阻?为什么使用上拉或下拉电阻?

评论