这一期我们来讨论一些名词,就是标题里满满当当的英文单词。当然,其中最核心也是最基本的,就是OCV。什么是OCV?它又有什么含义呢?或许后端的朋友们对它相对熟悉些。

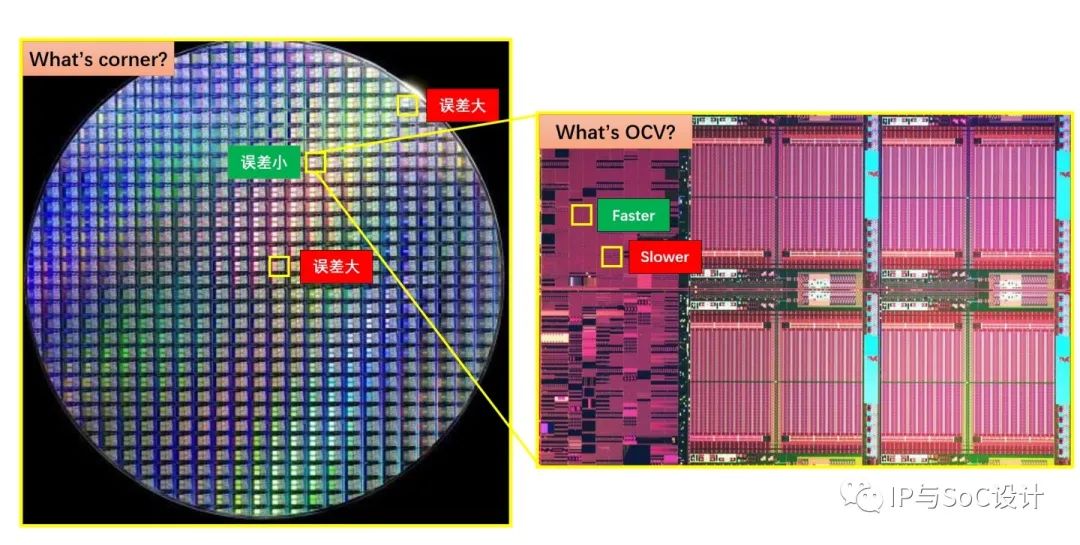

某种意义上来说,芯片很脆弱。在生产中,外界环境的各种变化,比如PVT,都可能会使芯片产生不同的误差,从而导致同一晶圆上不同区域上的芯片里的晶体管速度变快或变慢,从而产生corner的概念。

由于这些偏差的存在,不同晶圆之间,同一晶圆的不同芯片之间,同一芯片的不同区域之间,情况都是不相同的。造成这些差异的因素有很多种,这些因素造成的不同主要体现:

1,IR Drop造成局部不同的供电的差异;

2,晶体管阈值电压的差异;

3,晶体管沟道长度的差异;

4,局部热点形成的温度系数的差异;

而OCV就可以描述PVT在单个芯片所造成的影响,我们在时序分析时引入derate参数模拟OCV效应,其通过改变时延迟的早晚来影响设计。

在了解OCV和它的演进历程之前,我们不妨多了解些概念,可以有助于我们更全面地去理解它。

工艺角(Process Corner)

与双极晶体管不同,在不同的晶片之间以及在不同的批次之间,MOSFETs 参数变化很大。为了在一定程度上减轻电路设计任务的困难,工艺工程师们要保证器件的性能在某个范围内。如果超过这个范围,就将这颗IC报废了,通过这种方式来保证IC的良率。

传统上,提供给设计师的性能范围只适用于数字电路并以“工艺角”(Process Corners)的形式给出。其思想是:把NMOS和PMOS晶体管的速度波动范围限制在由四个角所确定的矩形内。这四个角分别是:快NFET和快PFET,慢NFET和慢PFET,快NFET和慢PFET,慢NFET和快PFET。

例如,具有较薄的栅氧、较低阈值电压的晶体管,就落在快角附近。从晶片中提取与每一个角相对应的器件模型时,片上NMOS和PMOS的测试结构显示出不同的门延迟,而这些角的实际选取是为了得到可接受的成品率。因此,只有满足这些性能的指标的晶片才认为是合格的。在各种工艺角和极限温度条件下对电路进行仿真是决定成品率的基础。

工艺角分析,corner analysis,一般有五种情况:

fast nmos and fast pmos(ff)

slow nmos and slow pmos(ss)

slow nmos and fast pmos(sf)

fast nmos and slow pmos(fs)

typical nmos and typical pmos(tt)

t,代表typical(平均值)

s,代表slow(电流小)

f,代表fast(电流大)

PVT(process,voltage,temperature)

设计除了要满足上述5个corner外,还需要满足电压与温度等条件,形成的组合称为PVT(process,voltage,temperature) 条件。

设计时设计师还常考虑找到最好最坏情况,时序分析中将最好的条件(Best Case)定义为速度最快的情况, 而最坏的条件(Worst Case)则相反。

根据不同的仿真需要,会有不同的PVT组合。以下列举几种标准STA分析条件:

WCS(Worst Case Slow):slow process,high temperature,lowest voltage

TYP(typical):typical process,nominal temperature,nominal voltage

BCF(Best Case Fast):fast process,lowest temperature,high voltage

WCL (Worst Case @ Cold):slow process, lowest temperature, lowest voltage

在进行功耗分析时,可能是另外的一些组合,如:

ML(Maximal Leakage):fast process,high temperature,high voltage

TL(typical Leakage):typical process,high temperature,nominal voltage

三种STA(Static Timing Analysis)分析方法:

1,单一模式,用同一条件分析setup/hold;

2,BC_WC模式,用worst case计算setup,用best case计算hold;

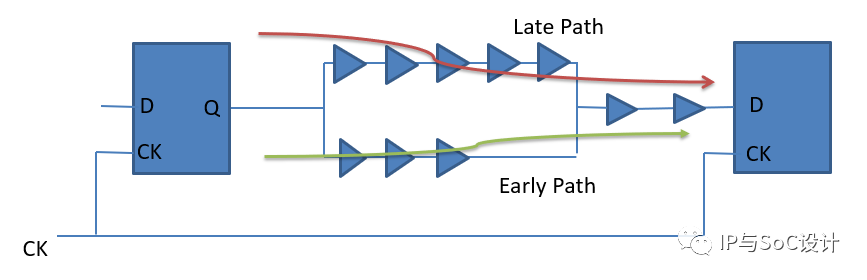

3,OCV模式,计算setup 用计算worst case数据路径,用best case计算时钟路径;计算hold 用best case计算数据路径,用worst case计算时钟路径。

Tip:

BC-WC:即为best case corner和worst case corner,分别代表两种不同的PVT环境。BC时,timing-arc的时间最短,WC时,timing-arc的时间最长。

考虑到芯片运行环境的变化,以及在芯片制作中难以克服的工艺原因造成的Die to Die的参数不同,在原来Single Mode中通过分析的芯片,在真实芯片运行中,未必能完成所设定的功能。

考虑到single mode的粗糙性,在130nm以下的工艺中基本上已经不用了。因此设计人员引进了BC-WC(best corner-worst corner)分析模式。BC-WC模式下,工具会分析芯片所可能出现的最好和最坏的运行情况,保证这两种极端情况下芯片功能的完整性。

而OCV模式,AOCV模式,POCV模式等均是在不同PVT(不同corner)的基础上添加derate。

什么是OCV

OCV,也就是On chip variation。

与corner同理,同一块芯片上的晶体管也会有变快或者变慢的现象,因此产生了OCV的概念。

在设计中引入OCV的目的在于从设计角度考虑芯片在实际生产中可能出现的各种差异(variation),从而适度增加设计余量(margin),减少不必要的设计悲观量(pessimism)。

随着芯片工艺的发展,对于STA的要求也越来越高,并且设计的复杂度不断提升。传统的WC-BC模式已无法准确的反应芯片的实际真实时序。OCV正是在这种情况下被提出并实际应用到STA中。

OCV在path上设置统一的derate,悲观度较高。derate数值是指对launch、capture、data line的cell或者net上添加一个比理想情况更为悲观的倍数,比如针对setup,launch的derate统一设置为1.1,表示delay时间增加值原来的1.1倍,capture的derate统一设置为0.9,表示delay时间变为原来的0.9倍。从而使设计能够覆盖实际生产过程中产生的variation。针对common path,利用cppr将悲观量移除。

Tip:

CPPR (Clock Reconvergence Pessimism Removal),共同路径悲观去除

实现方式:

(1)运用于主PVT库对应的微小差异PVT库

(2)set_timing_derate命令设置全局derate值

Tip:

timing derate,我们可以称为时序增减因子。在芯片的生产过程中,由于刻蚀、不同点的温度、金属不均匀、串扰、晶体管沟道长度等影响因素,导致片上各个位置单元延迟不一样。因此,我们需要一个缩放因子来让设计更加严格。

timing derate是计算OCV的一种简单方法,在某单一条件(BC-WC)下,把指定path的delay放大或者缩小一些,这个比率就是derate。

OCV中电压的考虑

电压需要分为电压全局偏差,电压局部偏差来理解。

同样以ffg 0.88v来check hold为例。我们可以将0.88v作为全局电压。在这个电压下,device的速度最快。但是,由于对于clock的lauch,capture都采用的最快的device,并不能覆盖所有的最差情况。

因此,在ocv中增加一部margin来覆盖这一部分情况也就可以理解了。

OCV中温度的考虑

温度同样可以划分为全局温度偏差,局部温度偏差。全局温度偏差,将在PVT中得以体现。由于温度反转的影响,仅采用极限温度-40c,125c有时候并不能覆盖全局温度偏差中的最差情况。有时需要增加额外的温度的corner。

而由于芯片内部不同位置之间,由于device翻转速率,电压降等不同,导致局部相同的时序路径中,温度也有偏差。采用相同的温度仍然不能覆盖所有最差情况。

在进行signoff时,需要增加ocv余量,覆盖温度局部偏差。

OCV分析

-OCV建立时间分析,暂不考虑CPPR

-OCV保持时间分析,暂不考虑CPPR

-timing derate

-CPPR

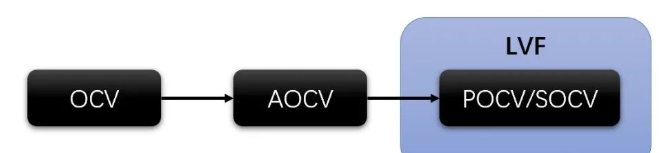

关于AOCV、POCV和LVF

什么是AOCV呢?

随着半导体工艺的进步以及芯片设计的日趋复杂化,传统OCV约束方式已经越来越不符合45nm及以下工艺的千万门级高速芯片设计。相对于传统OCV在path上设置统一derate值的方法,AOCV更为科学与合理的根据path的实际情况加上不同的derate值。通过科学合理的方法降低了derate值的悲观度。

在传统OCV上引入了对路径长度和整个路径在物理上所跨越的距离的考虑。在实际设计中,通过对一条line中cell在不同的逻辑深度时的仿真,以及基于前后级在物理中不同距离来得到一个更精确的derate值来进行时序分析,而不是OCV传统的粗放式的统一的derate。

AOCV,即Advanced OCV。它在传统OCV分析方法的基础之上更进一步,在传统OCV上引入了对路径长度和整个路径在物理上所跨越的距离的考虑。

随着数据路径的增长,OCV效应会减弱;随着跨越距离的增加,OCV效应又会增强。AOCV就是要通过考虑这些OCV效应的变化从而避免过度悲观的OCV分析。如何来有效 降低OCV的过度悲观,是我们提高时序分析准确性的关键。

因此设计人员想到了通过仿真以及结合芯片的实际物理情况,对每个cell给出更贴近实际情况的derate值,将能有效的帮助我们得到更准确的时序分析。由此我们引入了AOCV分析模式,在AOCV中,我们将通过对cell在不同的逻辑深度时的仿真,以及基于前后级在物理中的不同距离来得到一个更精确的derate值来进行时序分析,而不是传统的粗放式的统一的derate。

AOCV derate table:

(1)path depth:基于cell在整条时序路径中所处的深度或者级数来考虑derate

(2)path distance:基于路径中cell或net跨越的物理距离来给出相应的derate

也正是因为OCV存在以下缺点:在实际中的variation,绝少是一个统一的数值,而大概率是服从正态分布的。所以AOCV才应运而生。

既然有了AOCV,为什么要有POCV?

1,当工艺进化到14nm后,AOCV分析模式中动态设置时序减免值的方法已经不能满足精度要求,其分析结果的悲观型也无法很好地改变。

2,AOCV需要先分析逻辑深度和物理距离两个因素,再设置时序减免值,导致CPU工作量巨大,时序分析计算时间增加。

3,时序优化过程中增加或者删除缓冲器会改变逻辑深度,然后又需要根据逻辑深度重新选择时序减免值,重新时序计算,迭代次数和时间增加。

POCV (Parametric On Chip Variation)

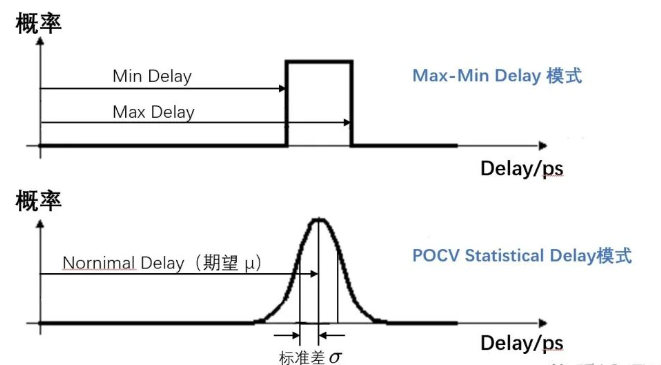

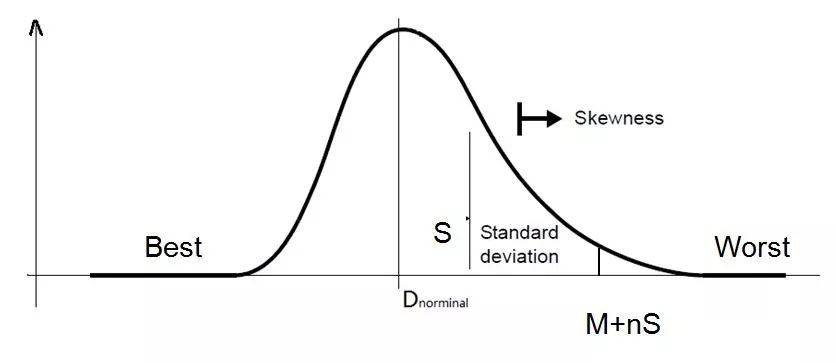

POCV,又称SOCV(Statistical On Chip Variation),如下图所示,POCV和AOCV一样将delay模拟成一个正态分布。每个cell的delay最高概率出现在期望值u周围,整体落在正负3倍标准差区间内的概率为99.7%。

以上介绍的时序分析方法就是POCV,也叫SOCV,全称为Statistic OCV。这是一种比AOCV更加先进的分析模式,它放弃了用最worst和最best的情况去标记delay,取而代之的是M+nS和M-nS的值,因此timing的情况会比OCV以及AOCV更加乐观。

至于LVF是什么呢

LVF,liberty variation format。是一种和liberty库文件(.lib)有关的数据格式。

POCV的内容可以集成到类似于liberty文件中,有助于时序分析。

审核编辑:汤梓红

-

芯片

+关注

关注

456文章

50886浏览量

424178 -

晶圆

+关注

关注

52文章

4922浏览量

128047 -

晶体管

+关注

关注

77文章

9698浏览量

138323 -

OCV

+关注

关注

0文章

25浏览量

12548 -

POCV

+关注

关注

1文章

6浏览量

12464

原文标题:科普:OCV、AOCV、POCV、LVF

文章出处:【微信号:IP与SoC设计,微信公众号:IP与SoC设计】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

用Labview vision assistant怎么做OCV识别急求

为什么要有POCV?

基于开路电压(OCV)的电量计设计

获取锂离子(Li+)电池参数,用于基于开路电压(OCV)的电

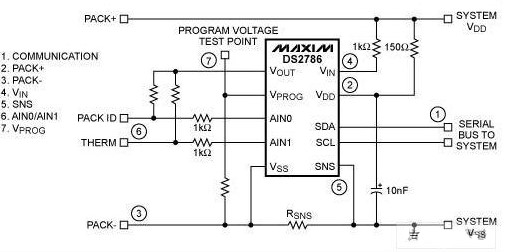

基于开路电压(OCV)的电量计DS2786

AOCV时序分析法降低工作电压

基于DS2786 OCV电路板的编程及测试步骤

OCV、AOCV、POCV、LVF都是些什么?

解释DS2786的开路电压(OCV)电量计

AOCV时序分析概念介绍

科普:OCV、AOCV、POCV、LVF

科普:OCV、AOCV、POCV、LVF

评论