引言

在电路设计自动化的时代,综合工具的作用不言而喻,通过综合,设计人员能够获得自己所设计模块的规模、时序性能和关键路径等有用信息,进而指导自己优化设计结构。本文就来说说综合工具DC工作的全流程,希望对设计人员和DC的初级使用者有所启发。

DC (Design compiler) 是Synopsys 公司综合核心工具,内嵌六种工具:DC Explorer、HDL Compiler、Library Compiler 、Power Compiler,DFT Compiler and DFTMAX 和Design Vision,在综合的不同阶段DC调用相应的工具实现所需的功能。DC包含以下功能技术:DC Expert,DC Ultra 和DC Graphical。DC Expert 能够进行功耗、面积和时序的优化,采用线性负载模型计算延时;DC Ultra所采用的优化算法也更先进,且DC Ultra提供拓计算技术,即在拓扑模式下不采用线性负载模型而是采用Synopsys的布局优化技术,以保证综合结果和最终物理设计更好的相关性;DC Graphical具有DC Expert和DC ultra 所有特性,并且能够优化multicorner-multimode 设计、减少布线拥堵和进行初步floorplan。

DC Expert:启动命令dc_shell,综合命令compile。

DC Ultra:拓扑模式启动命令dc_shell -topo,综合命令complie_ultra。

DC Graphical:启动命令dc_shell -topo,综合命令complie_ultra -spg。

Synopsys对综合的定义十分形象Synthesis=Translation + Logic Optimization +Gate Mapping,这正好表示出使用DC综合的过程,将RTL设计translate成GTECH门级网表,再根据施加的约束对电路优化并向特定工艺库映射。本文力求解释清楚综合过程,不涉及具体综合脚本和施加约束方法。

DC是调用HDL Compiler来将读取的设计转换成不依赖于工艺的GTECH门级网表的。这里需要说明的是GTECH网表中不仅仅只有与非门、异或门这种门电路符号,还有时序器件符号SEQGEN,如果设计中使用加、减、乘和比较等运算,GTECH会将其提取出来并用以带有OP标识的符号表示,这方便后续进行高级别电路优化;另外,设计中避免不了使用选择逻辑,如不特别声明,DC在这一阶段对选择逻辑用SELECT_OP表示,且在后续的映射阶段并不一定将SELECT_OP映射成多路选择器,而是采用与非门电路来实现其功能,如果想要映射成多路选择器,那么需要在RTL中声明synopsys infer_mux。

接下来DC根据综合人员设置的约束对GTECH网表进行优化,可分为组合优化和时序优化。

组合逻辑优化是先对组合逻辑设计进行工艺无关的逻辑级优化,从GTECH门电路提取出布尔表达式集合,这样可以对通过对布尔表达式的化简和变形实现对电路结构的化简和变形;

再向工艺库映射,映射的过程中根据速度和面积的目标选择适合的电路结构;

最后在对工艺依赖的门电路进行门级优化,这一阶段DC主要进行延时优化、功耗优化、DRC修正和面积优化。

时序优化分为两步,第一步向工艺库中的时序器件进行映射,此时组合逻辑还没有完成映射,也就没有具体的延时信息,时序器件的选择也不就不是最优的,时序优化是在映射后进行的,且进行时序器件替换时是将时序电路附近的组合逻辑一起考量的。

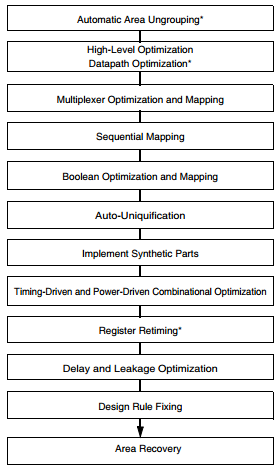

具体来说DC的优化流程是如图1所示的12步完成的,其中星号表示 DC Expert不支持。

1)如果使用compile_ ultra,默认首先自动进行ungroup操作,ungroup操作会将设计展平,展平设计必然会对内部信号重命名,这一操作会为后仿调试带来困难,所以建议先关闭这一功能,首次综合compile_ultra –no_auto_ungroup后,如果时序确实很紧张再打开这一功能,或者使用set_ungroup命令来实现局部ungroup操作。

2)high-level optimization是在时序和面积的约束下进行的资源提取和共享。如果使用DC Ultra工具,那么还可以对 datapath进行加减等运算operator进行提取优化。

3)Multiplexer Mapping and Optimization,即将组合逻辑中多路选择标识首先映射成单个多路选择器或者多路选择树,且为了能够共享多路选择树、减少面积,DC会重新调整选择信号的顺序。

4)Sequential Mapping阶段,DC将 SEQGEN代表的时序单元映射到 target Library中实际的时序器件。

5)Structuring and Mapping,即将设计中可以析出的子函数或者说子表达式作为中间变量,通过复用多次使用的中间变量可以减少面积,并将组合逻辑对工艺库进行映射。

6)Automatic uniquification,这个操作相当于综合人员使用了uniquify命令,该命令通过对多次例化的子设计进行复制和重命名的方式,实现每一个instance都有唯一设计与之对应,从而解决同一子设计多次例化问题。

7)implementing Synthetic Parts,在高级别优化阶段,类似+或者*这样的operator将其用一个抽象符号代表,称为Synthetic Part,此时将这些 Synthetic Part映射为具体不同结构的加法器或者乘法器等。

8)timing-driven combinational optimization,此步骤DC对关键路径再次进行重构,即增加总变量和复制中间变量等操作来提升速度,并且对关键路径再次进行operator的Implementing,比如将串行加法器替换为行波进位加法器。

9)Register Retiming,该步骤仅DC Ultra支持,该操作简单说就是对寄存器的移位、合并或者拆散复制等操作来减少违例。如果使用 optimize registers命令,那么寄存器的 retiming 更适合 pipelined designs;如果在 compile_ultra命令后带- retime选项,DC会自动进行局部 retiming操作,这更适合通用的non- pipeline design。

10)Delay and Leakage Optimization这一步骤,DC试图修复延时违例,DC再次对关键路径的电路结构进行评估,如果不满足约束,那么再次进行结构选择并进行替换;至于leakage优化,DC是将非关键路径的库单元替换为库中leakage更低的单元,比如选择库中高阈值电压单元。

11)Design Rule Fixing,DC 通过插入buffer或者 resize gate进行设计规则违例修正。

12)Area Optimization,此过程DC 默认是在不影响延时性能进行的。如果使用DC Ultra工具,综合人员可以使用 compile_ultra 命令后,再施加optimize_ netlist -area命令,在不影响时序性能的前提下进一步提升面积优化效果。

四、总结

另外,如果想要获得更好的QoR,从RTL code中提取数据路径块是十分重要,设计人员可以在compile_ultra前使用analyze_datapath_extraction命令来查看设计中算术内容并得到设计建议反馈。若想以html格式显示报告,带-html选项即可,HTML格式文件里面可以直接链接到RTL代码,便于检阅和修改。有时候观测一下设计的最小面积和时序性能的极限很有意义,不加任何约束,compile_ultral会综合出面积最小的情况;使用set_cost_priority -delay命令,将延时优化的优先级提前到DRC优先级前,可观测设计时序性能的极限。

审核编辑:汤梓红

-

电路设计

+关注

关注

6747文章

2826浏览量

220609 -

HDL

+关注

关注

8文章

332浏览量

49076 -

DC

+关注

关注

12文章

3696浏览量

686824 -

RTL

+关注

关注

1文章

395浏览量

62940 -

时序

+关注

关注

5文章

411浏览量

39049

原文标题:一文让你理解DC综合全过程!

文章出处:【微信号:芯司机,微信公众号:芯司机】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

Simulink是什么?Simulink的工作流程是怎样进行的?

英特尔图形性能分析器(GPA)的Windows DirectX工作流程分析

KiCad的工作流程解析

如何将机械设计工作流程集成到电气设计工具中?

工作流程图怎么用?有哪些绘制工作流程图的软件

浅谈无刷电机的工作流程

NX CAD软件:数字化工作流程解决方案(CAD工作流程)

浅谈DC综合工具的工作流程

浅谈DC综合工具的工作流程

评论