门控时钟的分类

通过门控方式不同,一个门控时钟通常可以分为下面基类,

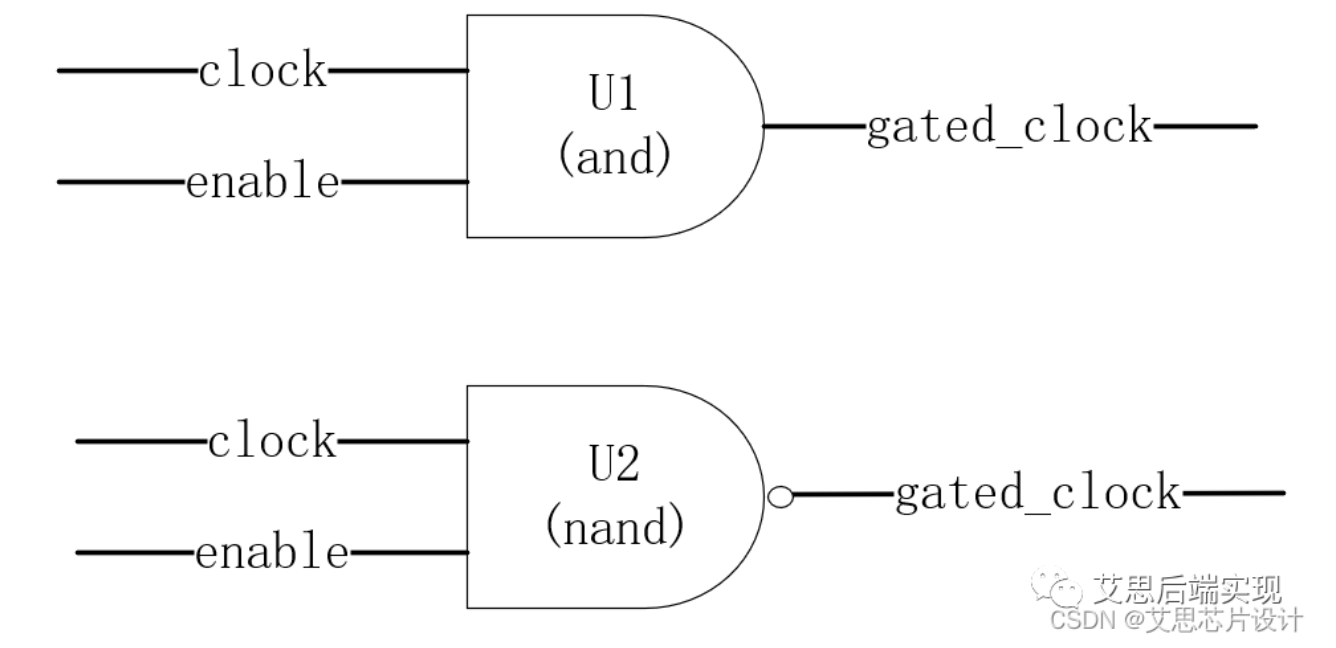

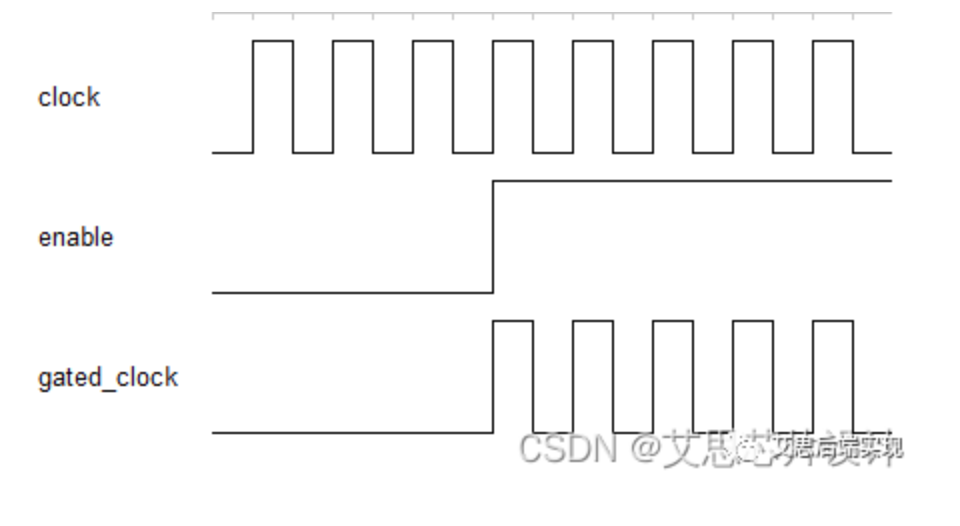

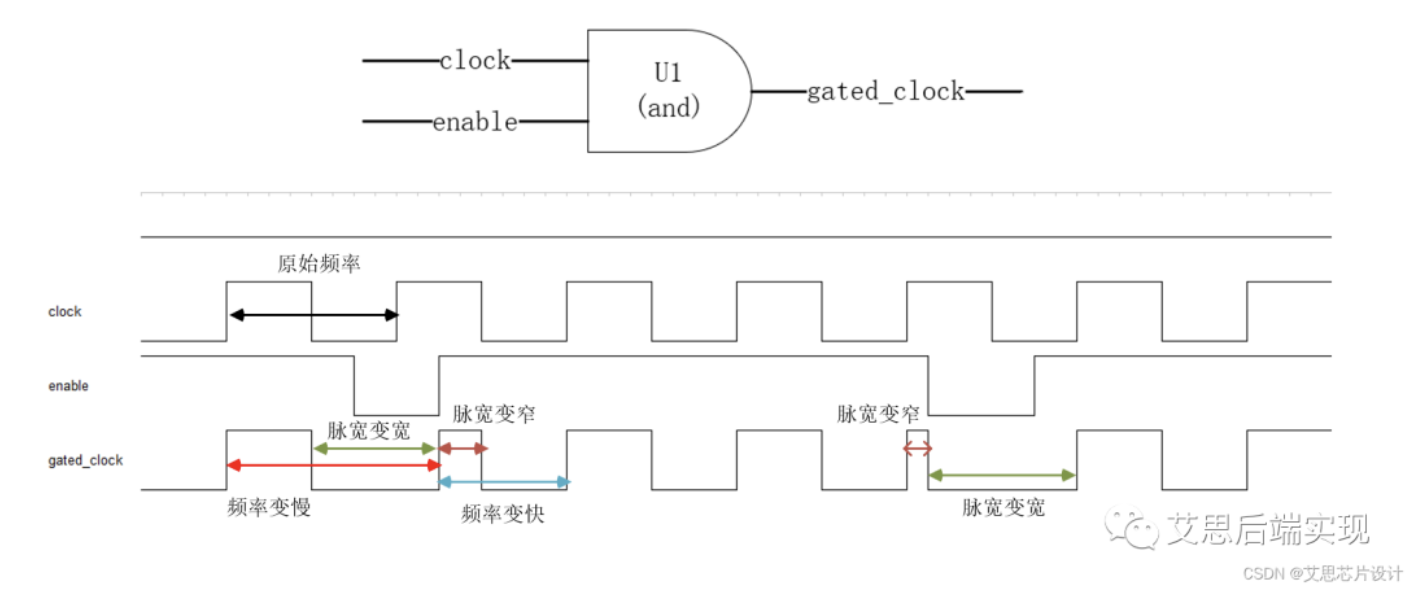

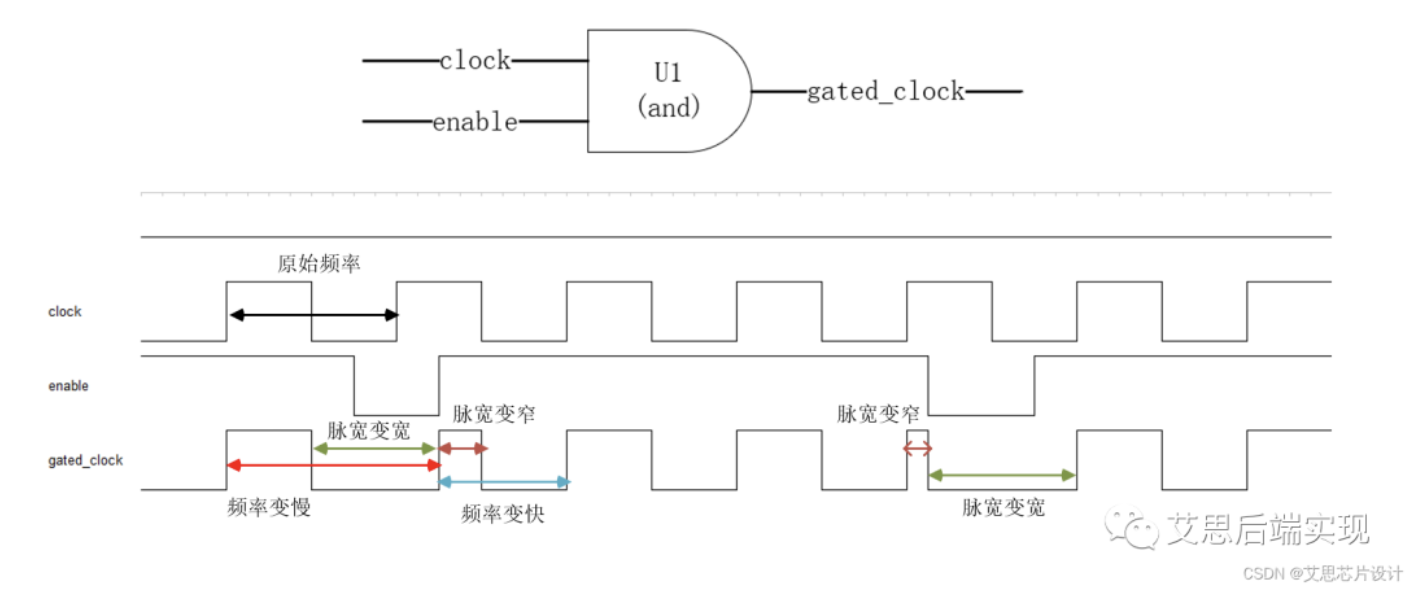

高有效(Active High)门控时钟

通常使用与门(and)或者与非门(nand)实现,

当使能信号为高的时候,时钟才可以被释放出去. 如果是nand,则输出的时钟是一个反向时钟的波形

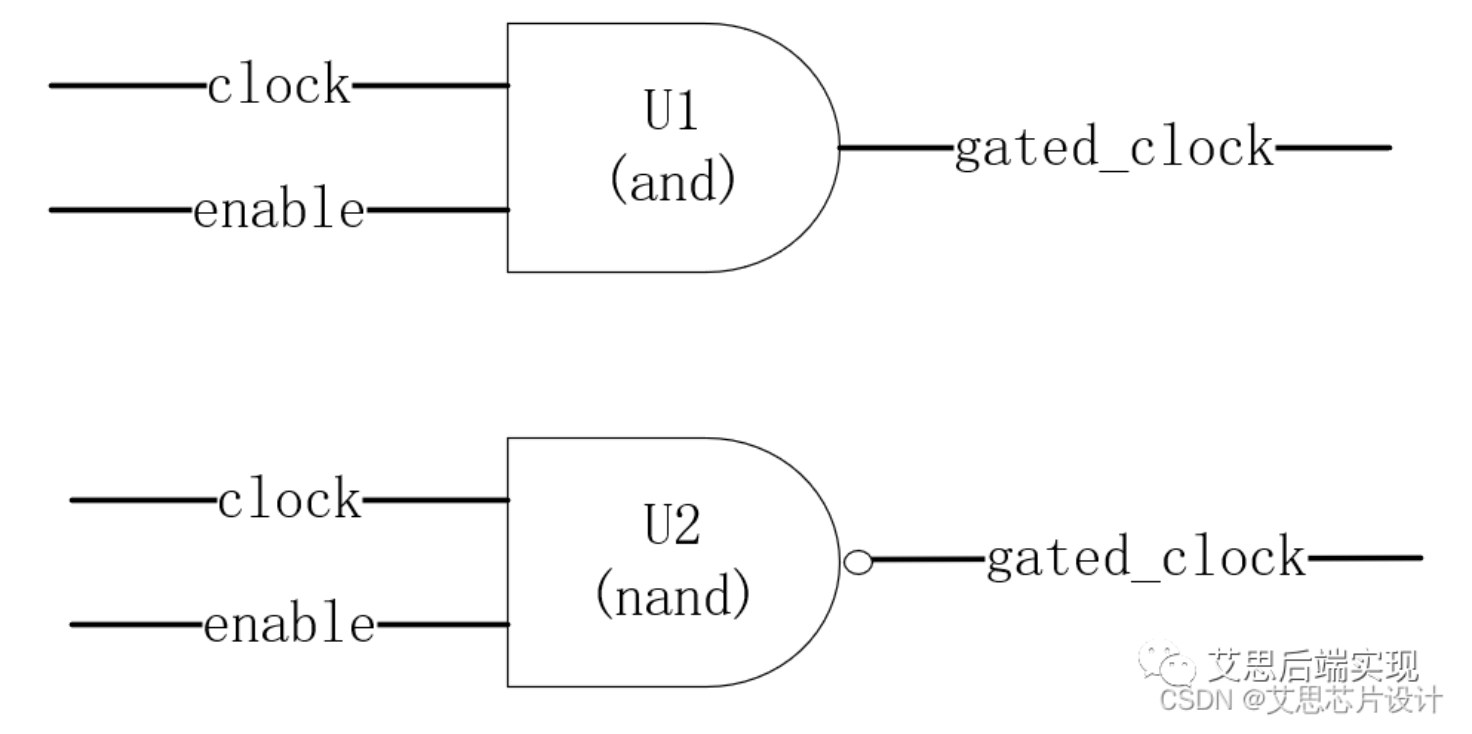

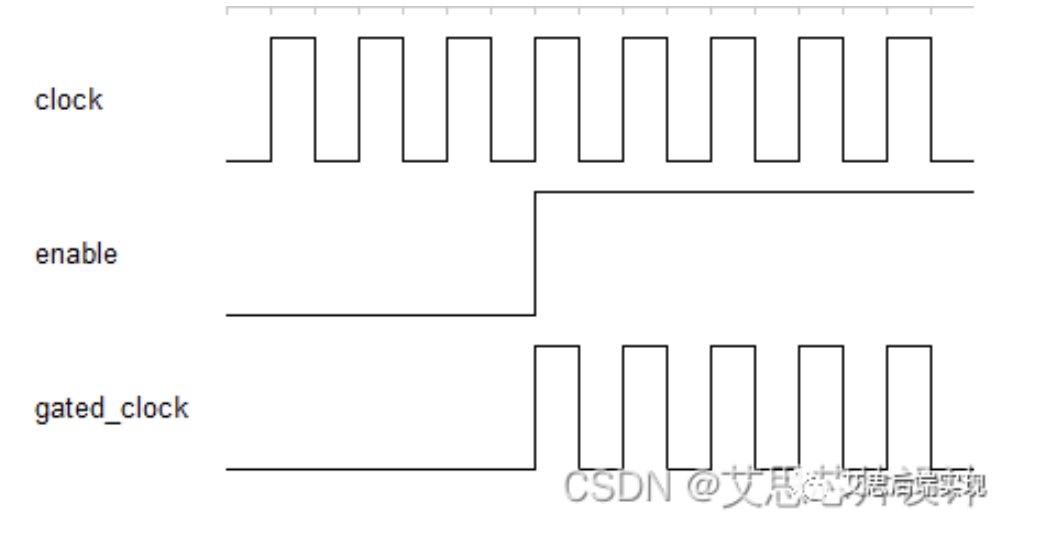

低有效(Active High)门控时钟

通常使用与门(and)或者与非门(nand)实现,

当使能信号为低的时候,时钟才可以被释放出去. 如果是nor,则输出的时钟是一个反向时钟的波形

除过上述的情况,有时候也会使用复杂一些的clock gating结构,这里的波形就会复杂一些

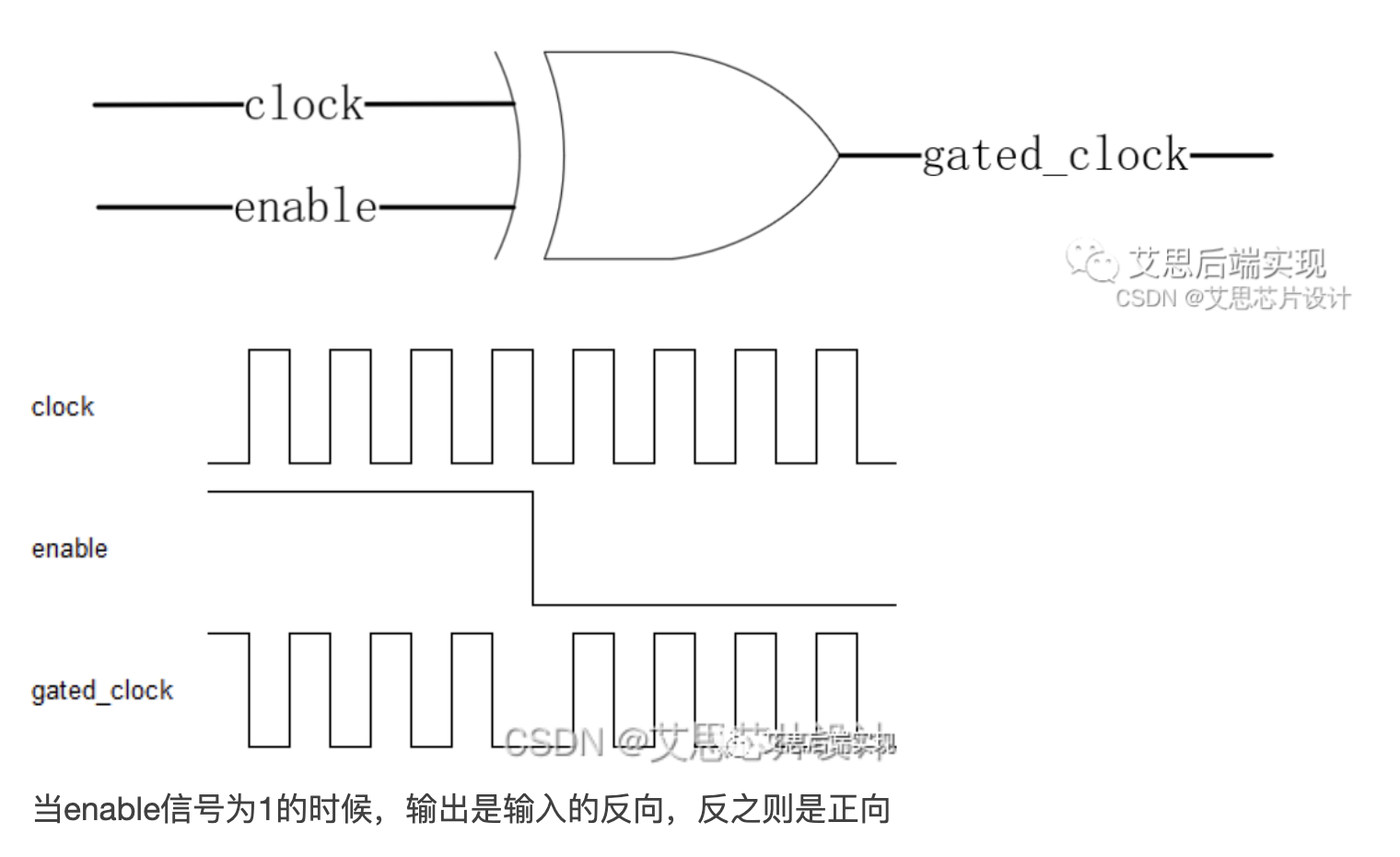

XOR结构的门控时钟

当enable信号为1的时候,输出是输入的反向,反之则是正向

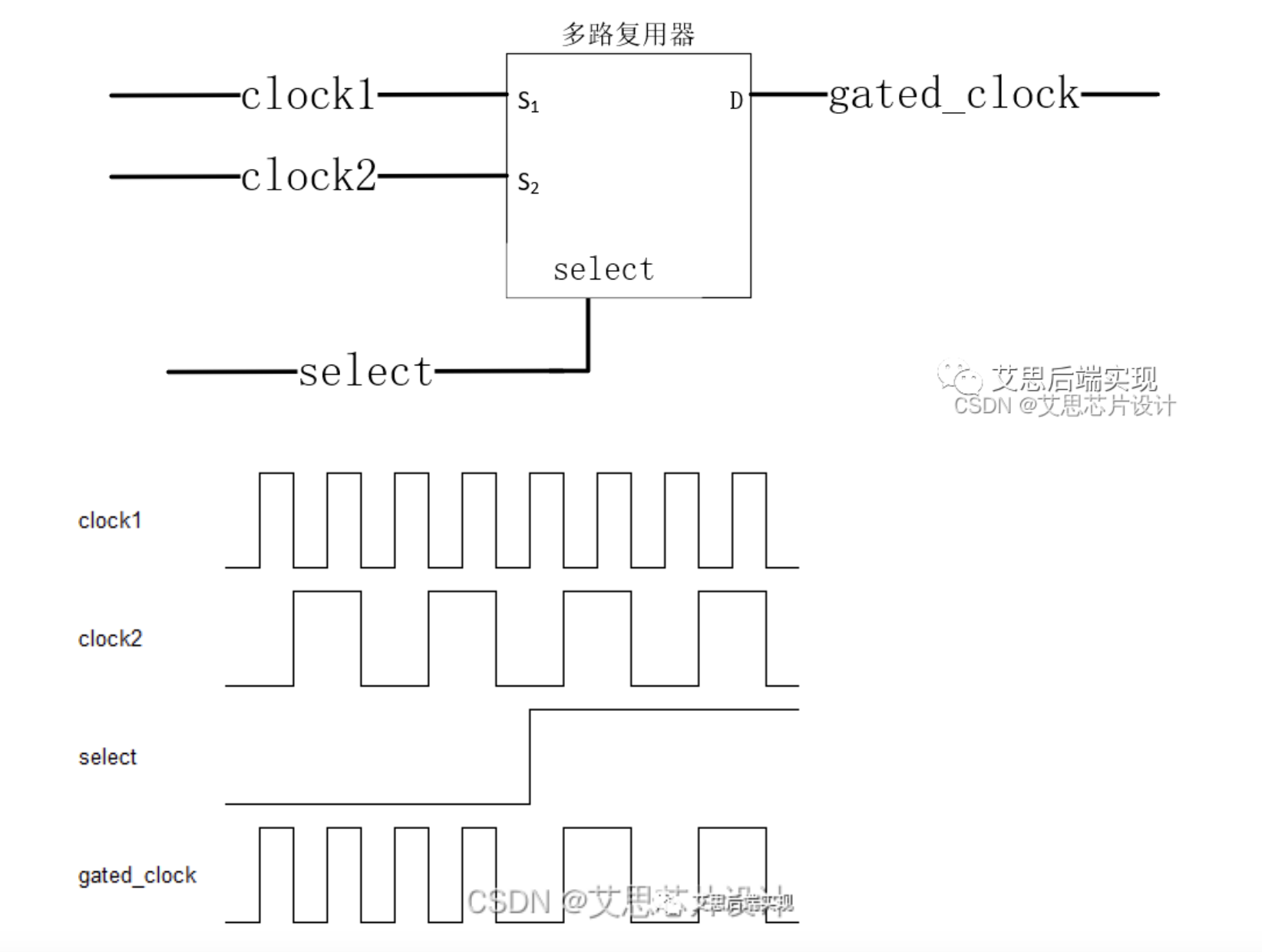

MUX结构的门控时钟

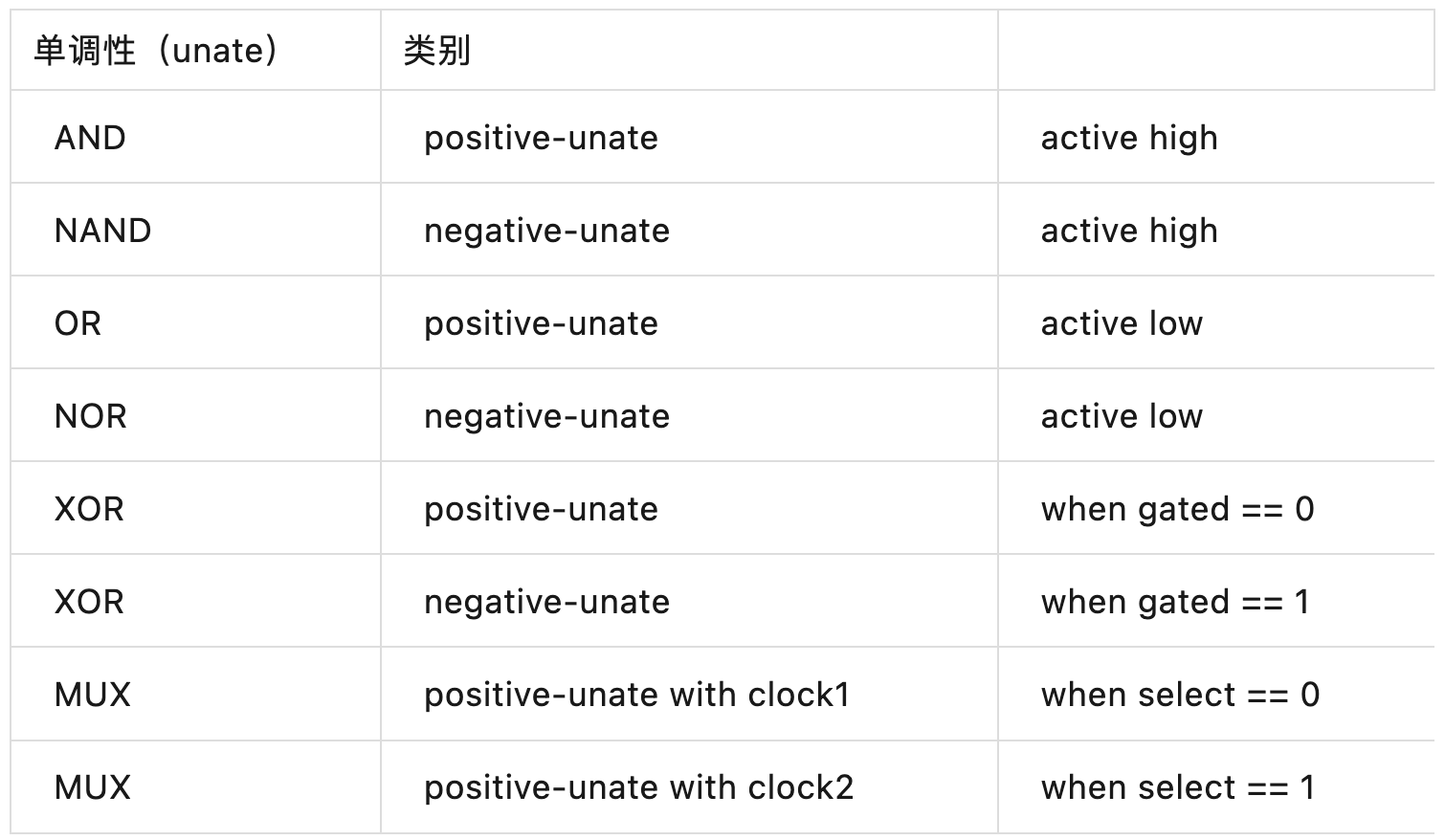

时钟传播单调性(unate)

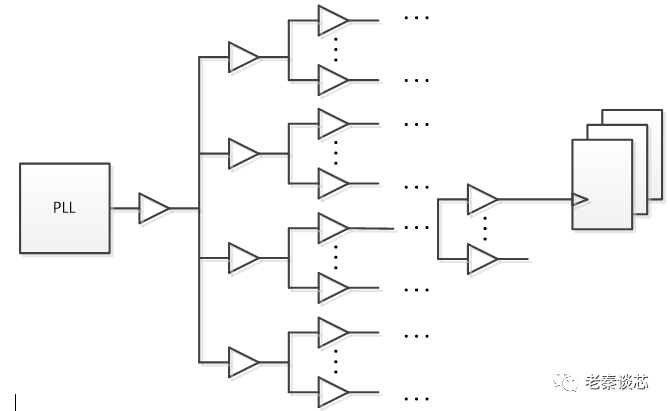

静态时序分析的基本原理是信号传播,对于拥有明确单调性的传播是构建正确STA环境的基础,数据通路对单调性(unate)通常不敏感,但是时钟通常是边沿敏感信号,所以时钟网络的单调性在STA时序分析的形态中尤为重要。STA工具也只有在单调性明确的时钟网络上做正确的时序分析,否则大概率会在实际芯片里边出现和STA不一致的情况。这点对于时钟网络的设计非常重要。

通过上述几种门控始终结构,从单调时钟的(unate)的角度来看,可以总结为下表

gating结构

所以,对于所有在时钟网络上的门控时钟,用户都需要明确其单调性,以便STA进行正确的分析。

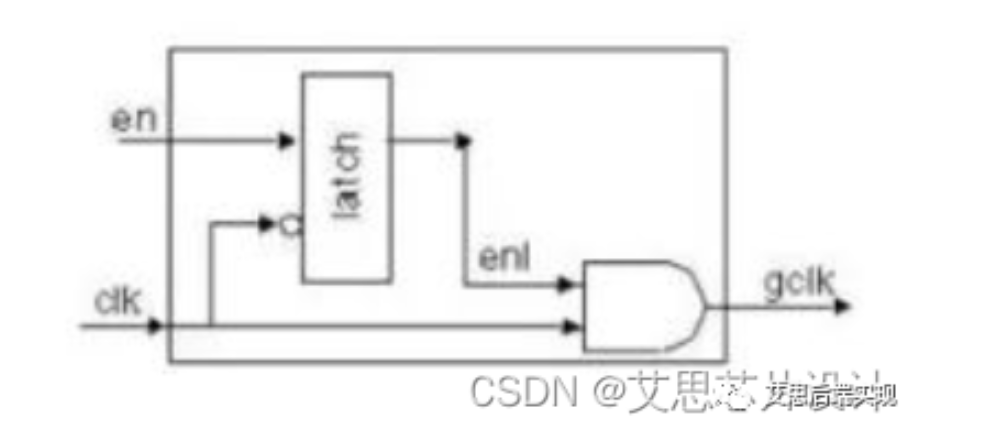

门控时钟的的检查(clock gating check)

通过上述描述,可以看到始终网络对于静态时序分析的重要性,所以在门控时钟在时钟网络的传播路径上的检查尤为重要。同样,基于clock gating的结构,对于active high,active low的门控时钟,通过STA工具。可以自动推断(infer)出相应的门控时钟检查(clock gating check),用户可以理解,这里的clock gating结构被STA所覆盖。所以用户在需要理解STA自动推断的原理,从而确保自己的时钟路径被STA覆盖

定义

工具判断门控时钟的基本标准如下

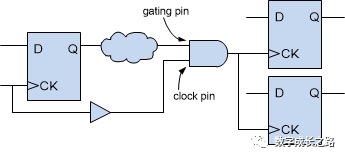

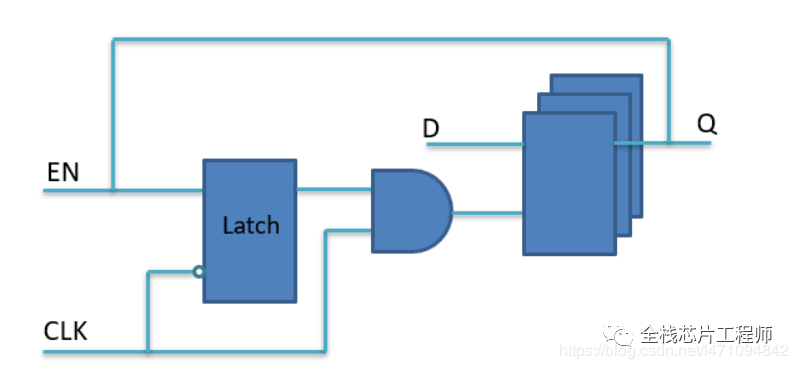

- 输入的时钟到输出必须存在一个组合逻辑的传播路径。常规的与或非,或者常规的latch based 的clock gating结构(见下图),但是register的分频结构,就不是一个clock gating。

-

输入的端口必须包含clock,但是输入到输出的传播必须包含数据路径(gated 信号)。

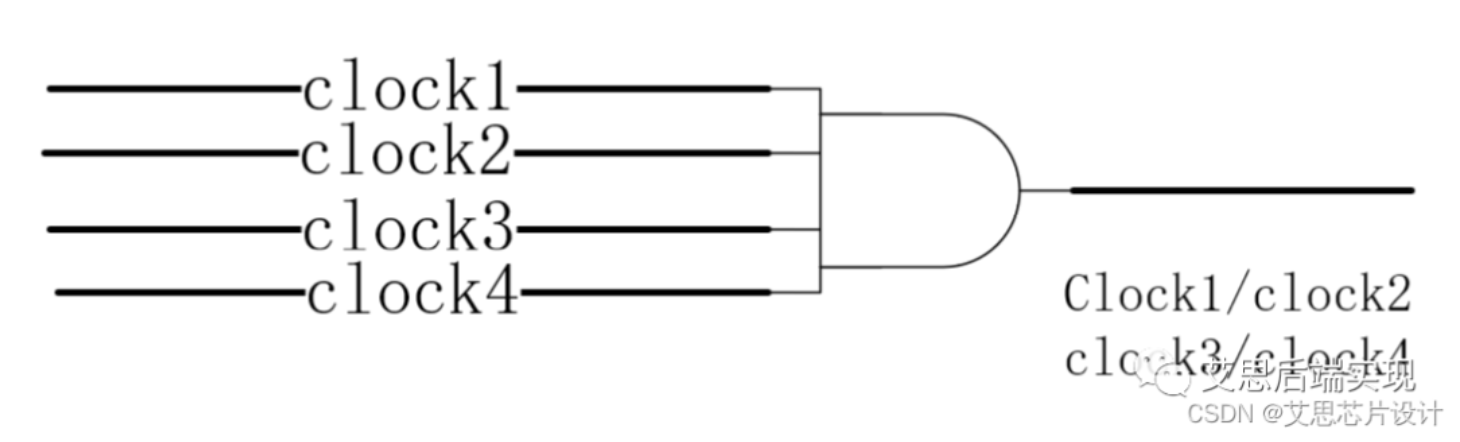

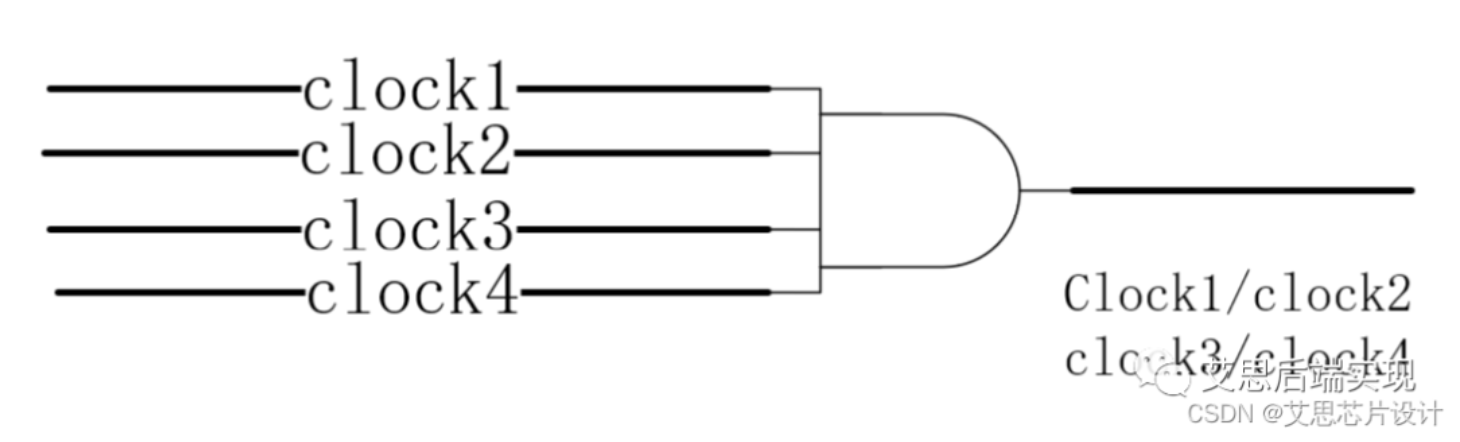

示例1: 组合逻辑的输入都是clock,STA会自动将时钟传播到输出,这样输出的会看到四个clock,这样的结构是无法判定为clock gating结构的,需要用户在使用的时候,当clock1有效的时候,clock2/3/4需要维持一个常1,否则输出的clock会出现混乱

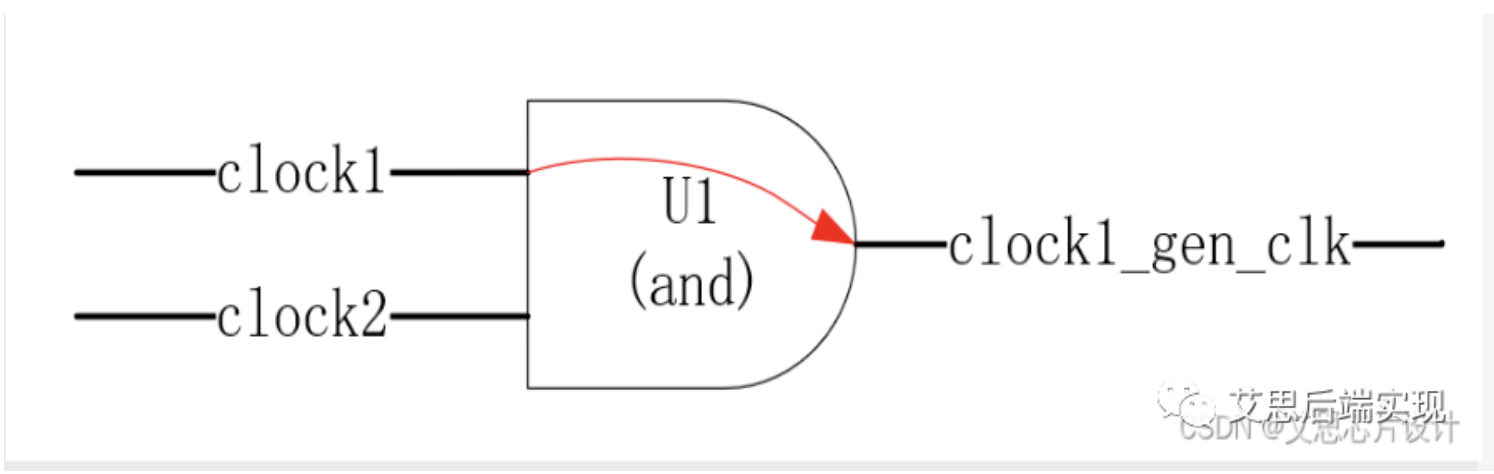

示例2: 输入都是clock,但是用户使用下列命令在输出创建了一个gen-clockcreate_generated_clock -name clock1_gen_clk -divide_by 1 \\ -source clock1 [get_pins U1/Z]

由于这个AND只有clock1传播过去,STA会自动推断出这是一个clock gating结构,clock1到clock2的gating 检查,clock2信号就是一个门控信号(enable)

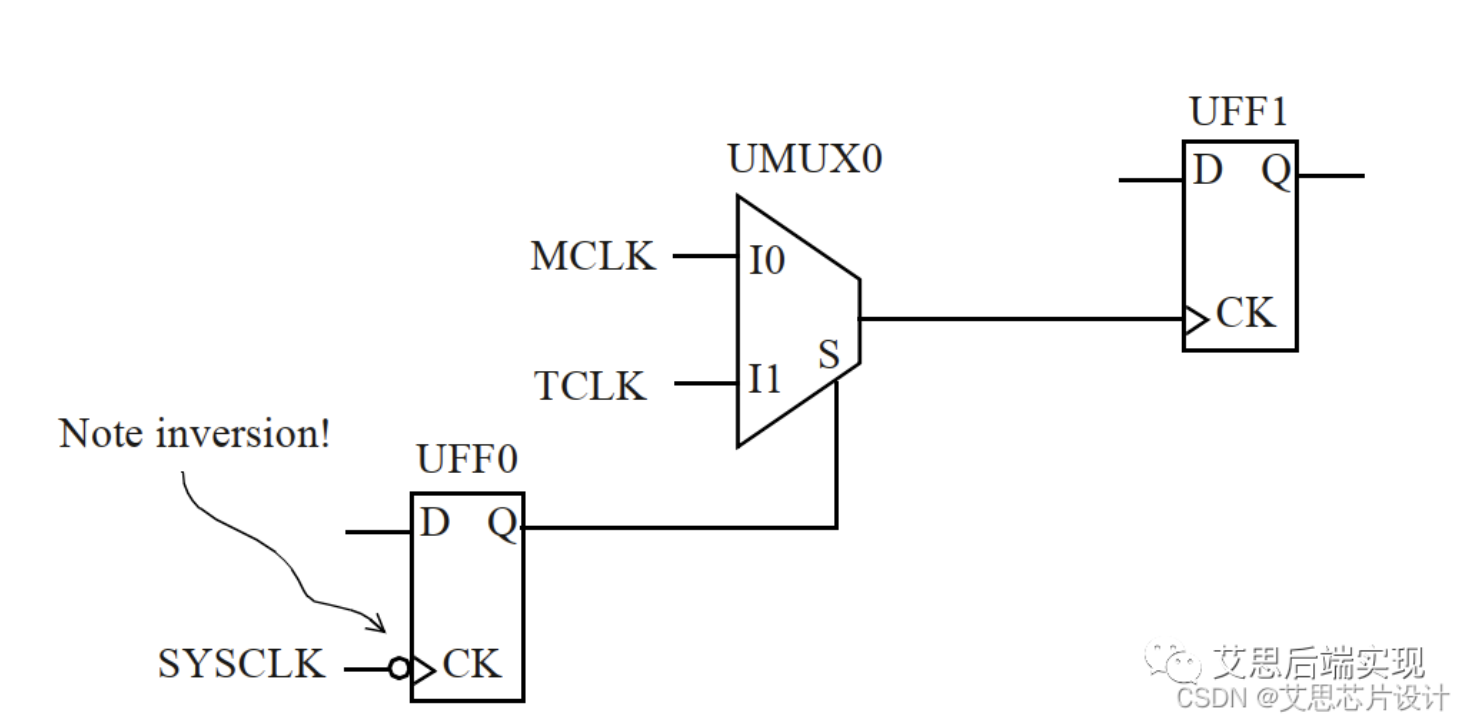

示例3 :对于一个复杂的门控时钟无法自动推断

这里的UMUX0满足clock gating的结构

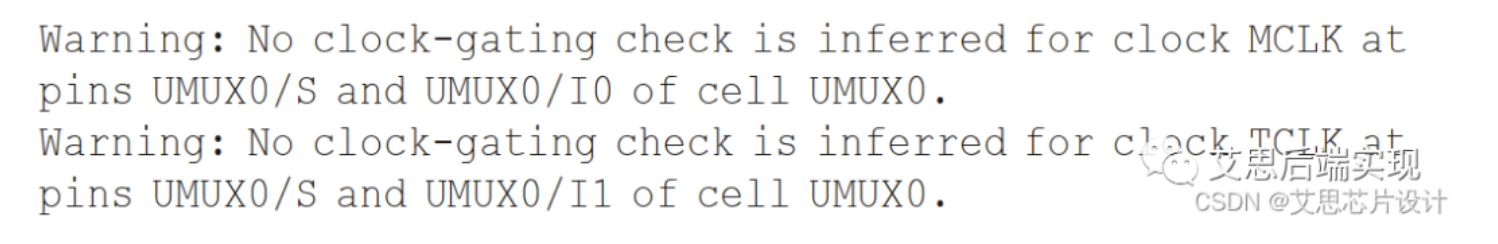

但是由于MUX结构是一个非单调性传播(none-unate),这样一个clock gating结构是无法自动推断(auto-infer)出来的,所以在clock 传播路径上存在风险,这样工具会给出如下的提示。需要用户进一步处理

挑战

门控时钟是在clock的传播路径插入了与或非逻辑,设计人员通过一定的逻辑控制达到对时钟的操作:

-

时钟分频:使用低频门控信号与高频时钟和做AND操作:

clock_slow = clock_fast * slow_enable -

时钟开合:使用半静态信号(近乎于始终关断控制):

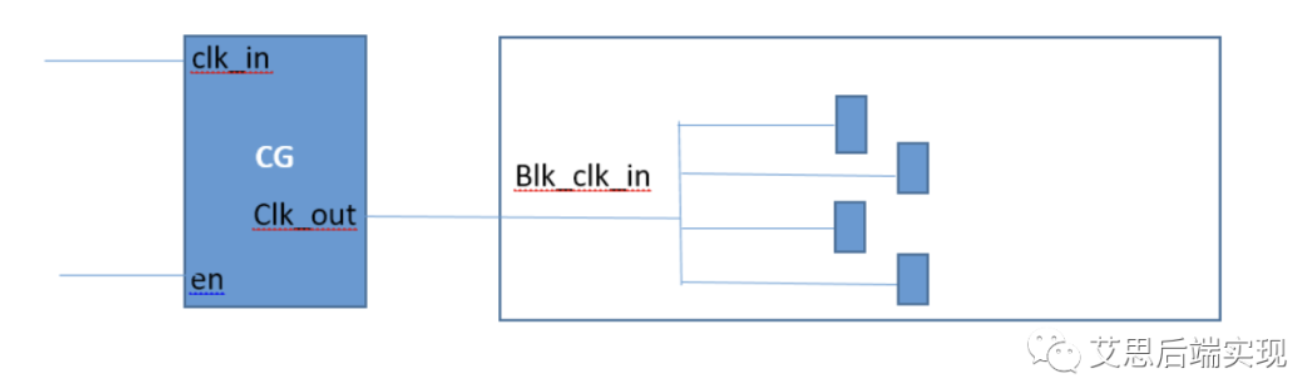

block_clock = sys_clock * block_enable -

时钟选择:使用半静态信号(近乎于模式控制):

clock_out =(sel==1'b0)?func_clock : scan_clock或者使用latch/reg结构,设计一个防抖的时钟切换,但是无论门控信号的产生有多么复杂,只要符合门控适中的结构,最后的clock gating check的点位是不会发生变化的,只是一个好的时钟生成(clock-gen)的设计,可以对STA更友好的,推进项目质量和加速项目收敛,这也是一个有经验的设计工程师的基本修为。

时钟是周期的变化,如果和一个门控逻辑进行组合逻辑运算,通常会出现时钟波形传播的问题(clock crop 或者clock swallow):

在不同阶段出现的enable信号,会导致clock的波形发生畸变

注意:在STA的timing report中,用户是不会看到上述问题的影响的的,但是在实际芯片中,这种影响是真实发生的。 所以,clock-gating的逻辑,必须被clock-gating-check所覆盖,并且需要谨慎地进行彻底修复,对于工具不能自动推断出来的clock-gating点,需要用户重点关注和给出解决方案,否则在最后的芯片中会出现和STA完全不一致(无法通过STA定位)的时序问题。

未完待续… (To Be continued …)

这样处理以后,LVS的std-cell的port mismatch也就完美解决了,

学好v2lvs,再也不用perl去patch source netlist了~~~~

【敲黑板划重点】

理解门控时钟检查(clock-gating-check)和理解门控时钟(clock-gating)同等重要,任何在clock tree上做的动作都需要额外的小心。

-

分频器

+关注

关注

43文章

448浏览量

50144 -

STA

+关注

关注

0文章

51浏览量

19072 -

门控时钟

+关注

关注

0文章

27浏览量

8986 -

XOR

+关注

关注

0文章

12浏览量

162070

发布评论请先 登录

相关推荐

FPGA的时钟门控是好还是坏?

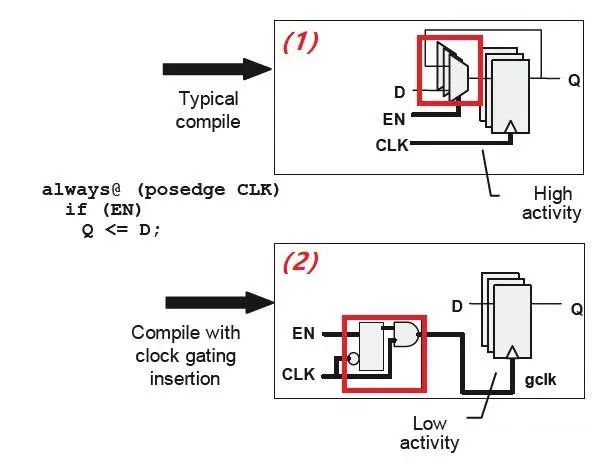

通常有两种不同的时钟门控实现技术

什么是门控时钟?如何生成门控时钟?

ASIC的clock gating在FPGA里面实现是什么结果呢?

门控时钟检查(clock gating check)的理解和设计应用

门控时钟检查(clock gating check)的理解和设计应用

评论