晶振电路设计考虑事项:

- 位置要选对:晶振内部是石英晶体,如果不慎掉落或受不明撞击,石英晶体易断裂破损,所以晶振的放置远离板边,靠近MCU的位置布局。

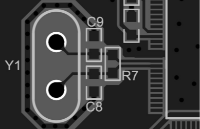

2.两靠近:耦合电容应尽量靠近晶振的电源管脚,如果多个耦合电容,按照电源流入方向,依次容值从大到小摆放;晶振则要尽量的靠近MCU。

3.走线短:所有连接晶振输入/输出端的导线尽量短,以减少噪声干扰及分布电容对晶振的影响。

使晶振、外部电容器(如果有)与 IC之间的信号线尽可能保持最短。当非常低的电流通过IC晶振振荡器时,如果线路太长,会使它对 EMC、ESD 与串扰产生非常敏感的影响。而且长线路还会给振荡器增加寄生电容。

4.高独立:尽可能保证晶振周围的没有其他元件。防止器件之间的互相干扰,影响时钟和其他信号的质量。晶振周围 1mm 禁布器件,0.5mm 禁布过孔走线,所有晶振下不打过孔(包括地过孔)。当心晶振和地的走线。

5.尽可能将其它时钟线路与频繁切换的信号线路布置在远离晶振连接的位置。

6.外壳要接地:晶振的外壳必须要接地,除了防止晶振向外辐射,也可以屏蔽外来的干扰。

如果实际的负载电容配置不当,第一会引起线路参考频率的误差.另外如在发射接收电路上会使晶振的振荡幅度下降(不在峰点),影响混频信号的信号强度与信噪.

当波形出现削峰,畸变时,可增加负载电阻调整(几十K到几百K).要稳定波形是并联一个1M左右的反馈电阻.

-

晶振

+关注

关注

34文章

2860浏览量

68010 -

晶振电路

+关注

关注

7文章

92浏览量

25294

发布评论请先 登录

相关推荐

晶振电路的PCB设计

晶振电路的PCB设计

评论