GRE是Global Route Environment的缩写,中文意思为全局布线环境,运用具备阶层化意识的全面绕线引擎与图形式互连流程规划程序。通GRE技术在短时间就可以开发出包含众多互连总线与芯片引脚数的复杂且高速的设计组件。此外,运用GRE技术后便于工程师实现更佳的功能密度与系统效能最大化。Cadence这项系统互连设计解决方案,为PCB设计人员提供智能型规划和绕线的环境,节省大量的时间、增进功能密度并提升效能,同时也大幅降低成本。

01

GRE布线规划模式

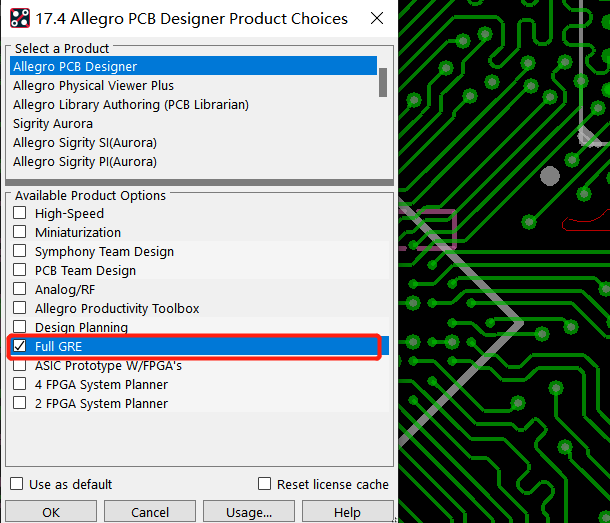

GRE提供不同的Options选项,来应对不同的设计要求,全功能的GRE功能要在Allegro启动的时候勾选Full GRE才能实现,或者通过File菜单--Change Editor选项进行切换后勾选Full GRE复选项后才能实现。如下图1所示。

图1 全功能的GRE功能启动

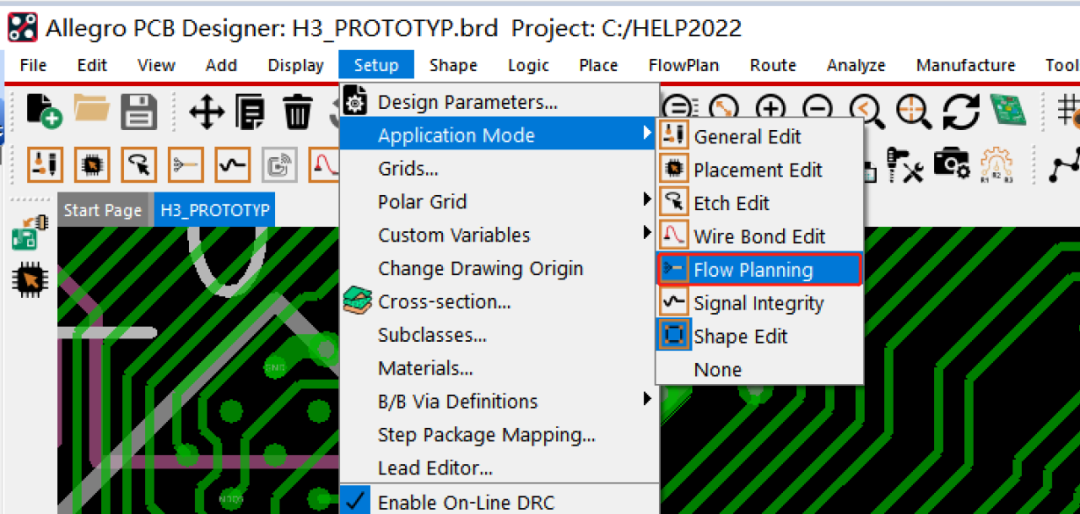

进入Allegro界面之后,想要启动GRE首先要选择GRE的功能模式,然后在Allegro的界面中选择setup菜单--Application mode--Flow Planning命令切换到该模式才能实现布线GRE规划。

图2 模式切换到Flow Planning

02

GER的参数设置

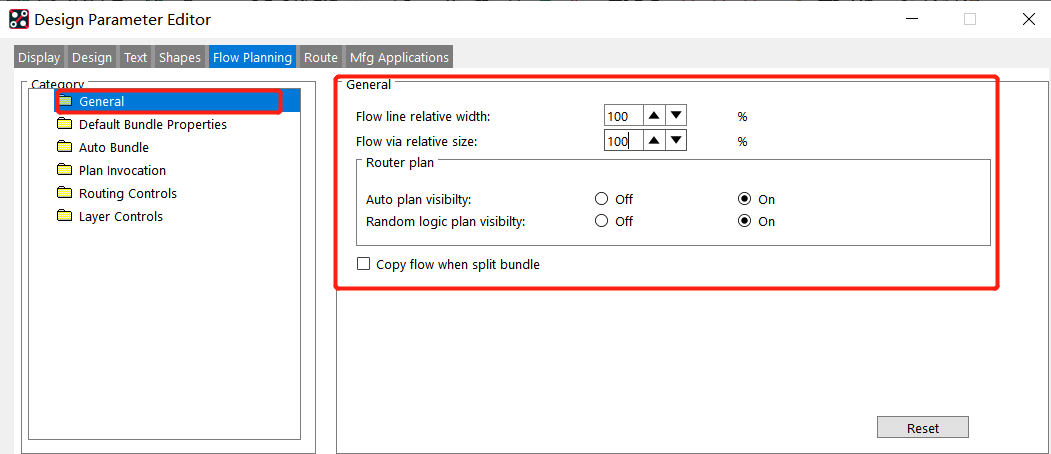

GER参数设置在Setup菜单--Design Parameter命令下的Flow Planning选项卡中。在General选项组里面,可以在设置Flow-line relative width文本框和Flow via relative size文本框中设置比例比例,用来定义一组飞线抽象成Bundle或者Flow后的宽度和过孔大小。如下图4和5所示。一般设置成100-150%为宜,或者根据自己的经验和板子上线的密度来定义。该参数对Bundle和Flow的设置全局有效,在该处的修改,对所有的Bundle和Flow都有效。

图3Flow Planning General选项卡

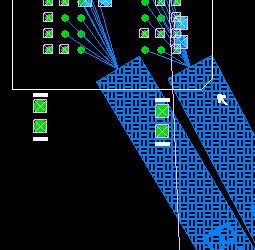

图4 100%的显示效果

图5 200%的显示效果

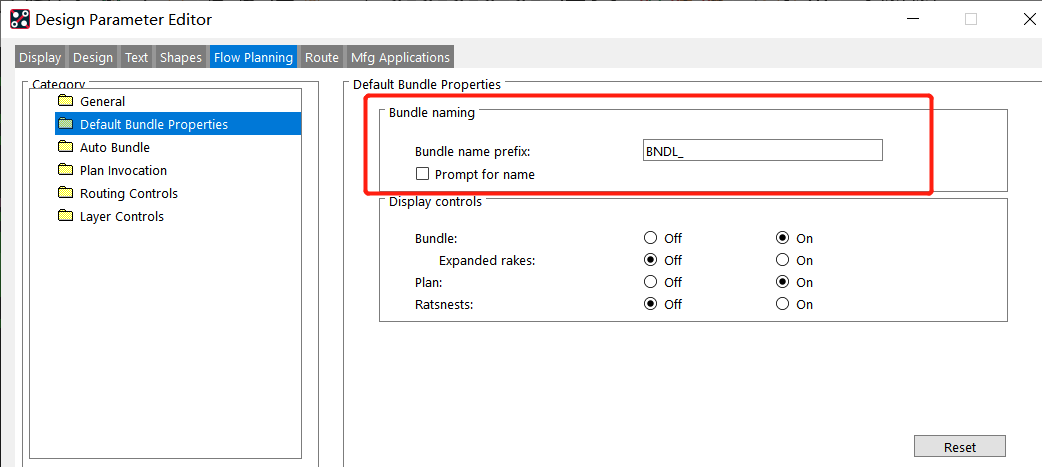

Bundle的命名规则也是可以修改的,可以针对单独的Bundle来设置特殊的名字,点击就能进行编辑操作。Bundle的命名设置功能有限,修改了规则只对以后新建立的有效,之前的无效。如下图7所示。点击Show Element命令可以查看Bundle的名称如下图6所示。

图6Bundle的命名规则修改

关于Expanded Rakes选项,若该选项设置成Off,飞线的显示是经过软件优化过的,该模式下连接线很顺畅且不存在交叉的情况,但这并不是真实的情况,它只是表明了元件和元件之间有多少飞线。若设置成On,元件和元件之间的飞线显示的将是真实的连接关系,能看到飞线是否存在交叉不顺畅的问题,建议将该项设置成On以便于对元件的布局进行调整。

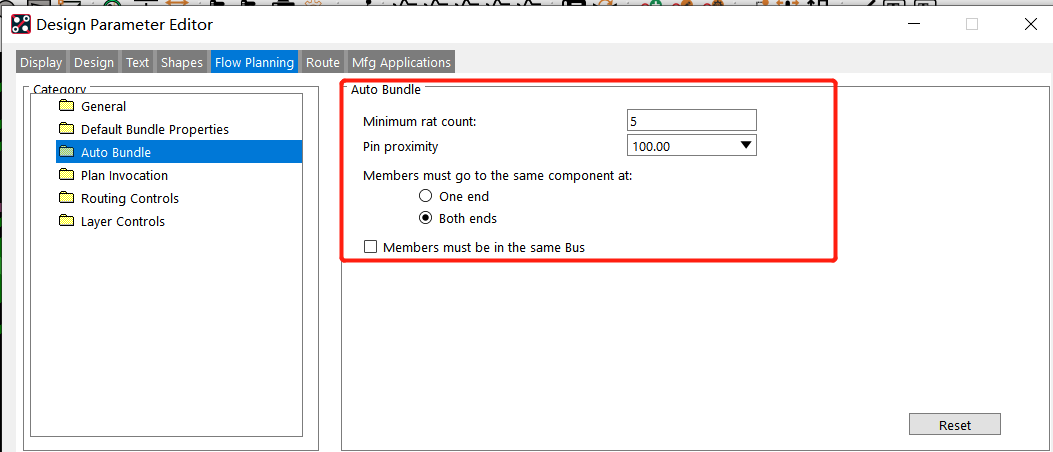

Auto Bundle的设置选项页,用来定义自动创建Bundle时一些参数的配置,具体如下。

(1)Minimum Rat Count文本框用来定义一个Bundle最小飞线数量,默认是5,表示具备5根以上的飞线时系统才会自动创建一个Bundle。

(2)Pin Proximity文本框用来定义同一个Bundle的Pin引脚之间的最远距离,只有在该距离之内的飞线,系统才会自动创建一个Bundle。

(3)Members must go to the same component单选框用来定义组成Bundle的飞线是否要同属一个元件。One end单选项定义属于同一元件网络,Both ends单选项定义属于不同元件网络。

(4)Members must be in the same bus复选框用来定义组成Bundle的飞线是否属于同一组总线。勾选后自动创建的Bundle会属于同一个总线。如下图7所示。

图7Auto Bundle的设置选项

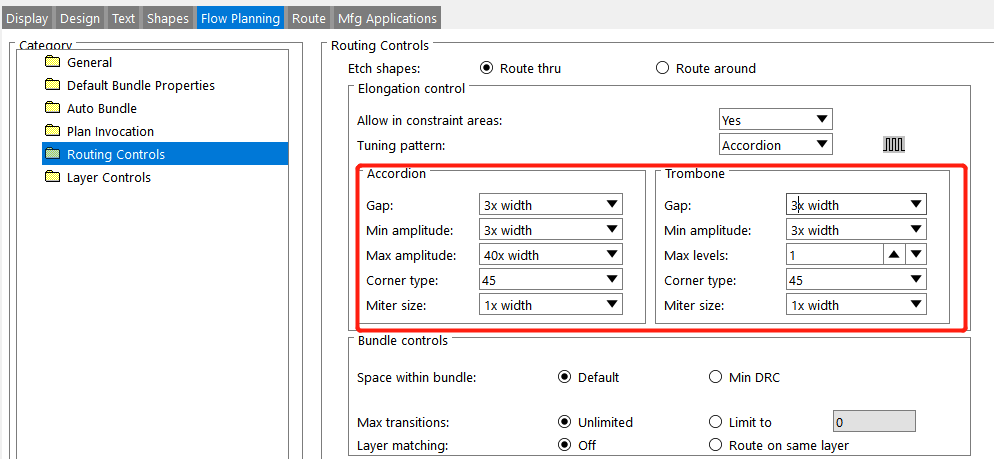

Routing Controls是布线参数的设置,设定绕线蛇形线布线的间距、和线之间的距离,线的转角,最小的间距等参数。

图8 Routing Controls布线参数设置

下期预告:实例讲解 | GRE的处理办法

通过4片DDR3中的1片为实例进行讲解,在Allegro中GRE处理的基本元素就是Bundle,详细讲解如何手动创建、自动创建、通过规则管理器来创建Bundle,并且编辑管理Bundle的详细操作。

教大家如何运用全局布线GRE规划应用技术提升智能绕线规划增强高密度PCB的设计效率。

-

布局

+关注

关注

5文章

269浏览量

25023 -

allegro

+关注

关注

42文章

657浏览量

145253

发布评论请先 登录

相关推荐

通信开关电源参数设置方法

变频器参数设置技巧介绍

德力西变频器恒压供水参数设置步骤

恒压供水变频器参数设置方法

金田变频器怎么调参数设置

s120编码器参数设置在哪里

松下伺服参数设置步骤

变频器的基本参数设置

频谱分析仪的参数设置方法

东元驱动器参数设置步骤及注意事项

变频器常用参数设置技巧与指南

技术资讯 | 全局布线GRE规划应用及参数设置

技术资讯 | 全局布线GRE规划应用及参数设置

评论