IP核(Intellectual Property core)是一段具有特定电路功能的硬件描述语言程序,常常被用于数字电路中。该程序与集成电路工艺无关,可以移植到不同的半导体工艺中去生产集成电路芯片,从而帮助开发人员减少工作量,并缩短产品上市时间。

IP核(Intellectual Property core)是一段具有特定电路功能的硬件描述语言程序,常常被用于数字电路中。该程序与集成电路工艺无关,可以移植到不同的半导体工艺中去生产集成电路芯片,从而帮助开发人员减少工作量,并缩短产品上市时间。

虹科针对不同的应用和领域开发了一系列以太网交换IP,因而用户可以将不同IP的特征进行组合以获得每种情况的最佳解决方案。下面将为您介绍虹科1G HSR/PRP交换机IP核。

01什么是HSR&PRP?

HSR和PRP是两项兼容性好、易于使用的冗余协议,其所属的国际标准为IEC 62439,并已在电力行业得到广泛使用和验证。随着网络拓扑越来越复杂,列车、工控甚至互联网等行业对网络可靠性传输的需求不断提升,这两种能够提供零切换延迟时间、在故障情况下不丢失帧的协议渐渐有了更广阔的应用。也正是因为如此,虹科推出了HSR/PRP IP核,来帮助用户开发相关产品。

点此获取更多HSR/PRP技术文章

02虹科1G HSR/PRP IP核

虹科HSR/PRP交换机IP核是一个完整的硬件解决方案,可实现高可靠性无缝冗余协议和并行冗余标准,并能够在低成本的FPGA上实现。它通过硬件来交换帧,这样可以提供很高的交换速度,同时也是实现变电站自动化的过程总线和机架间总线的最大允许使用年限和数据完整性所必需的。它是针对能源市场设备的一种灵活解决方案,该设备将连接到HSR环、PRP局域网或在IEC 61850的环境下起到网桥的作用。

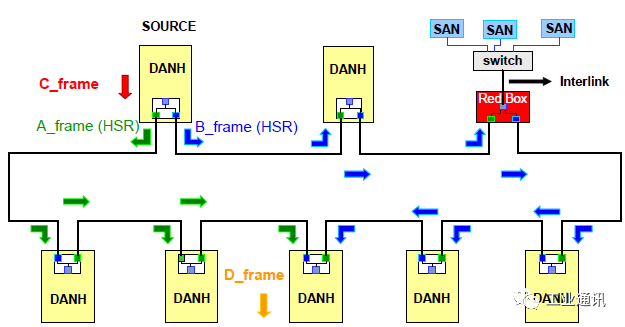

HSR单播流量环配置示例

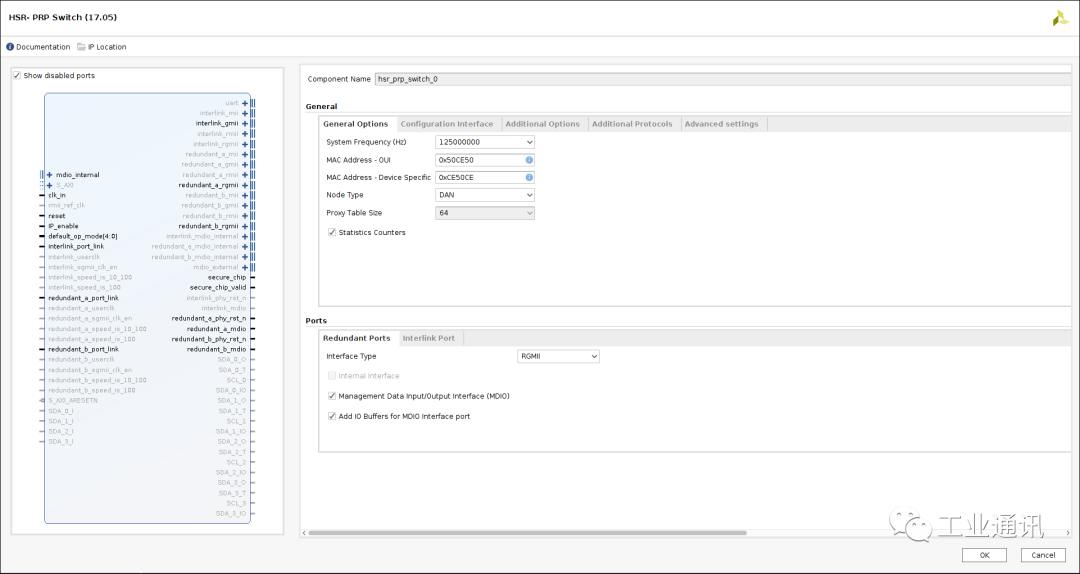

用于Xilinx Vivado工具的

虹科HSR-PRP交换机IP Core /

以下Xilinx FPGA系列支持虹科HSR-PRP IP核:

6系列(Spartan,Virtex)

7系列(Zynq,Spartan,Artix,Kintex,Virtex)

Ultrascale(Kintex,Virtex)

Ultrascale +(Zynq MPSoC,Kintex,Virtex)

通过利用新的Xilinx Vivado工具,虹科HSR-PRP交换机 IP核可以轻松集成到您的FPGA设计中,该工具允许在图形用户界面中使用该IP核,并以简便的方式配置IP参数。

/

关键特性

虹科HSR-PRP交换机IP核 /

1

# 接口

全双工10/100/1000 Mbps以太网接口

MII/RMII/GMII/RGMII/SGMII/QSGMII物理层设备(PHY)接口

每个端口支持不同的数据速率

铜缆和光纤介质接口:10/100/1000Base-T,100Base-FX,1000Base-X

2

# 交换

处理体系结构专用于HSR/PRP,千兆以太网的转发延迟为500ns

全硬件解决方案,无需片上微处理器或软件堆栈

已经过优化,几乎不需要逻辑资源,从而可以在低成本FPGA器件上实现

巨型帧管理

3

# 冗余与时间同步

可用于实现终端节点DAN、RedBox或QuadBox功能

带有单个标志,可以通过软件在PRP和HSR模式之间切换

支持与SoC-e 1588 IP内核结合的IEEE 1588-2008 v2

4

# 组态

MDIO、UART、AXI4-Lite或CoE(以太网配置)管理接口

以太网配置(COE):通过连接到CPU的同一以太网链路全面访问内部寄存器

购买IP核时提供驱动程序

5

# 可定制功能

节点表大小

每个端口的转发队列大小独立

冗余和互连端口中的IEEE1588v2 P2P透明时钟

可扩展的复制/循环丢弃表

VLAN优先级支持

通过AXI4-Lite、MDIO、UART或CoE(以太网配置)访问内部寄存器

具有集成SAN代理的RedBox模式

IEEE 1588v2普通时钟、混合时钟和边界时钟

-

FPGA

+关注

关注

1625文章

21665浏览量

601753 -

IP

+关注

关注

5文章

1646浏览量

149324

发布评论请先 登录

相关推荐

虹科培训 | 重磅升级!全新模式月底开班,你想学的都在这里!

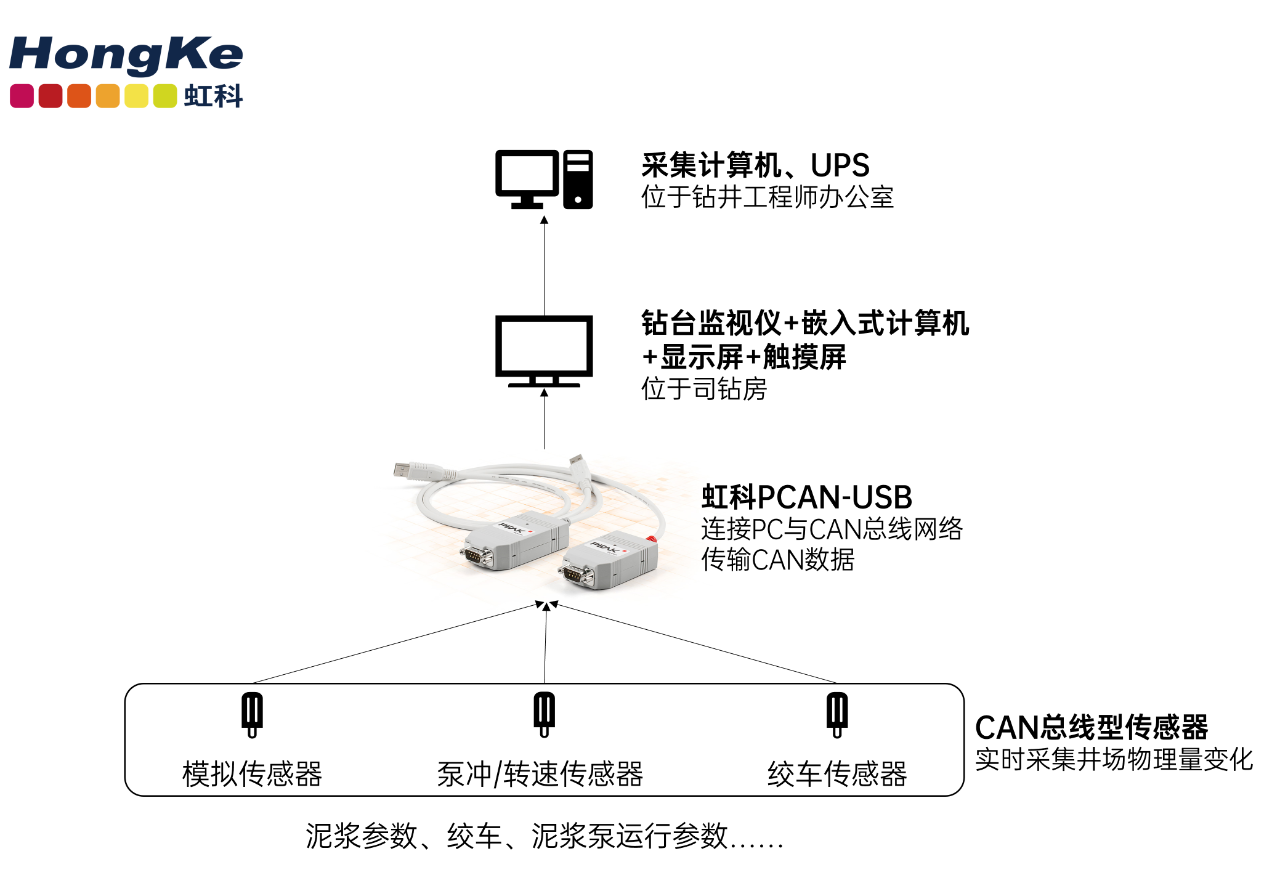

虹科应用 为什么虹科PCAN方案能成为石油工程通讯的首选?

虹科方案 | 精准零部件测试!多路汽车开关按键功能检测系统

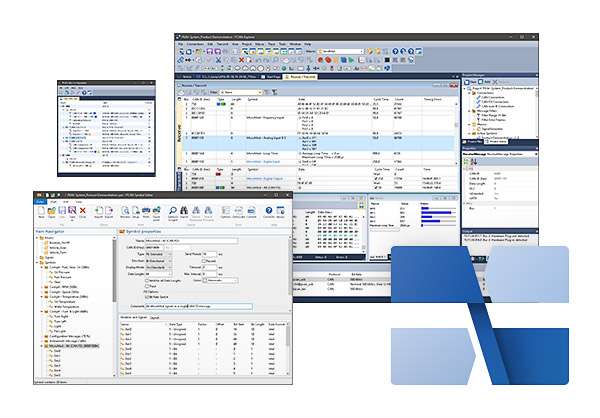

虹科应用 当CANoe不是唯一选择:发现虹科PCAN-Explorer 6

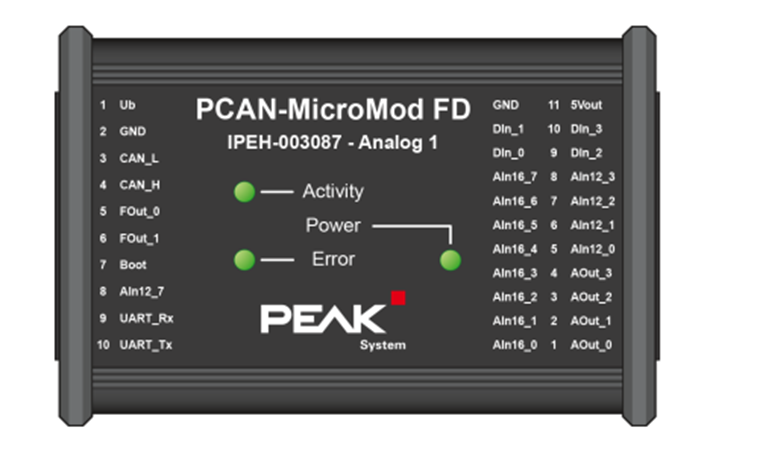

虹科案例|为什么PCAN MicroMod FD是数模信号转换的首选方案?

虹科方案 | 符合医药行业规范的液氮罐运输和存储温度监测解决方案

提高生产效率!虹科MSR165快速检测机器故障,实现精准优化

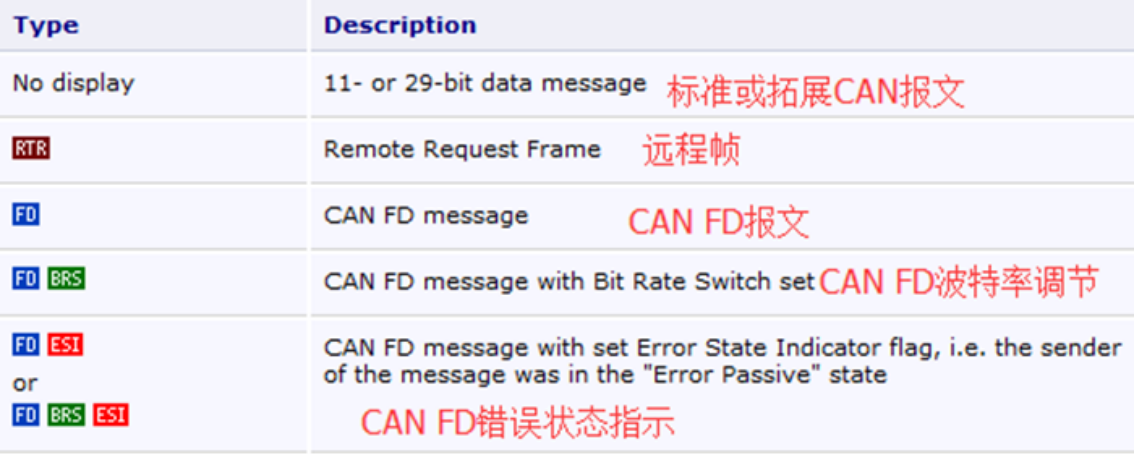

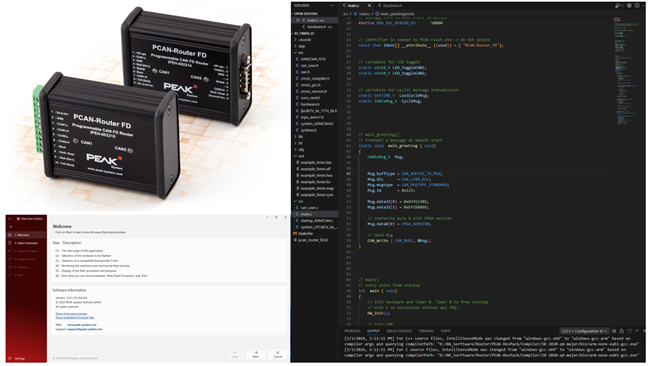

虹科分享 | PCAN工具:强大的CAN通讯解决方案,你了解多少?

虹科方案|释放总线潜力:汽车总线离线模拟解决方案

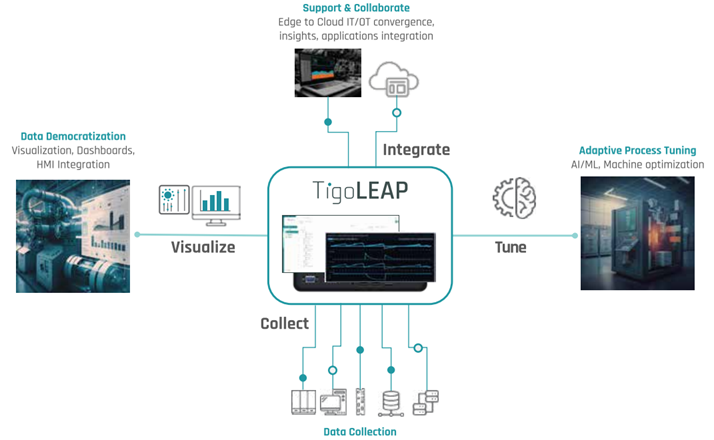

虹科方案|从困境到突破:TigoLeap方案引领数据采集与优化

虹科智能互联:您的智能通讯解决方案合作伙伴

虹科方案 | 虹科HSR/PRP IP核:全硬件解决方案,可在低成本的FPGA上实现

虹科方案 | 虹科HSR/PRP IP核:全硬件解决方案,可在低成本的FPGA上实现

评论