去年10月,第 54 届国际微电子研讨会在圣地亚哥举行。这是由国际微电子组装和封装协会(International Microelectronics Assembly and Packaging Society)主办的会议,简称为 iMAPS。

大会上,Cadence副总经理KT Moore先生亲自到场发表了一场题为《判断电子设计的下一步:后摩尔时代亦或超越摩尔时代(More Moore or More than Moore: an EDA Perspective)》的主题演讲。由于 KT 先生的姓氏是 Moore,和摩尔定律(Moore's Law)中是同一个单词,这场演讲可以说足够“摩尔”。

图为Cadence副总经理KT Moore先生在iMAPS大会发表主题演讲。

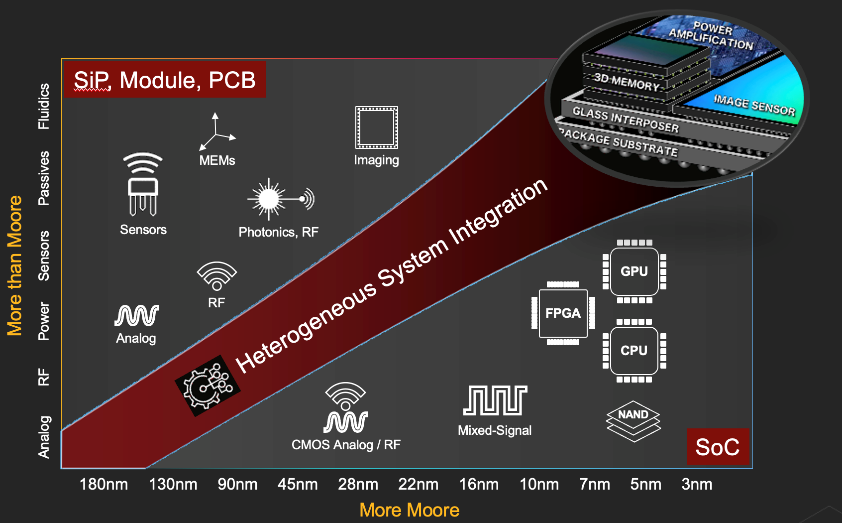

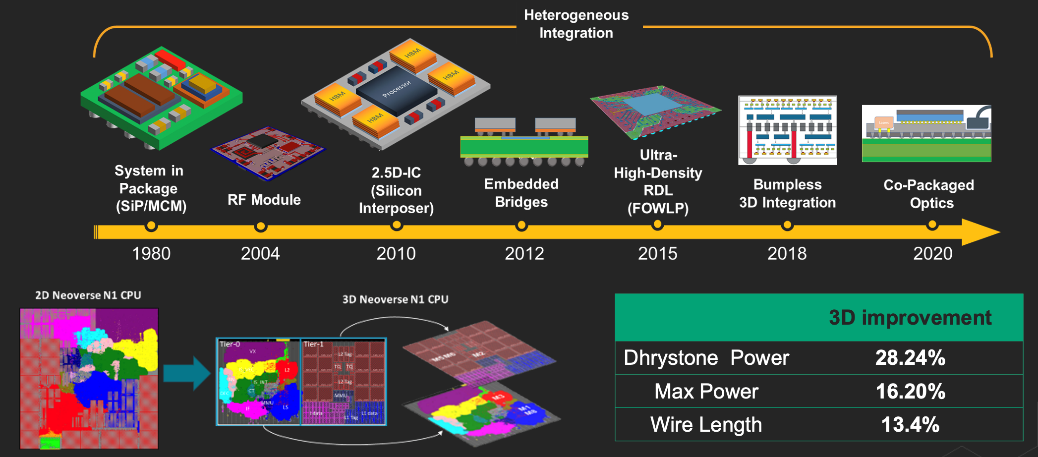

当然,“超越摩尔定律”(more than Moore) 令人朗朗上口,用来描述系统在芯片上扩展的方式,而不是单纯地指扩大硅的尺寸,摩尔定律之前重要的内容就是缩小元器件并扩大硅尺寸;而“超越摩尔定律”指的就是高级封装。

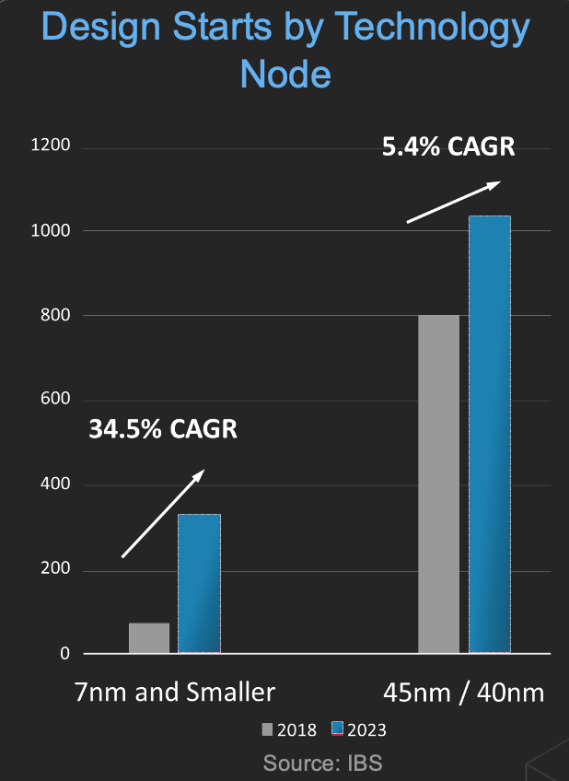

当数年前 KT 先生听说 7nm 工艺时,他预测可能只有十家公司能够负担在这种节点进行设计的能力(我也怀疑数量不会很多,当时几乎所有作出预测的人也都是这样认为的)。但是我们都错了;目前有几百家公司正在进行 7nm 及更先进的设计,其中包括成熟的半导体公司、遍布全球各地的初创公司,以及开始自主设计芯片的系统公司。

正如上图所示,先进节点的成长比例比成熟节点强劲得多(当然,先进节点的起步基础较小)。但两者都在增长,半导体行业呈现一片欣欣向荣的景象。

复杂的系统设计方法出现了分叉,有点像“双城记”。图中的右下角是传统的 SoC,即把所有东西都塞进一个裸片中;左上方是带有光学元件、射频...等其他功能的系统。目前,它们开始融合到中间的线上,形成异质系统的集成:

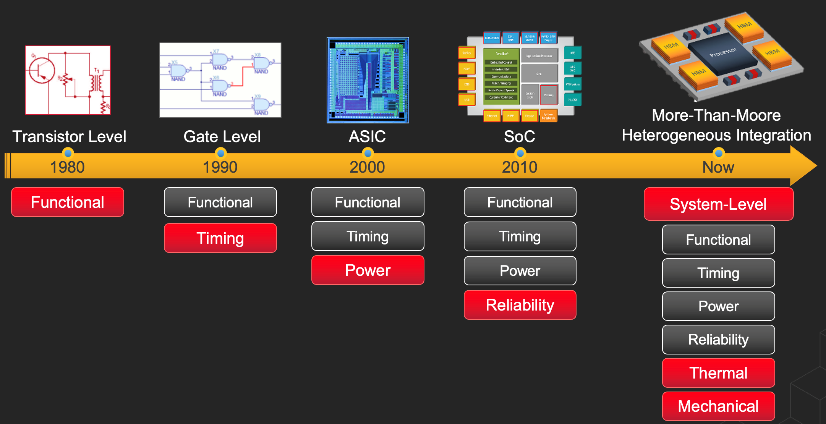

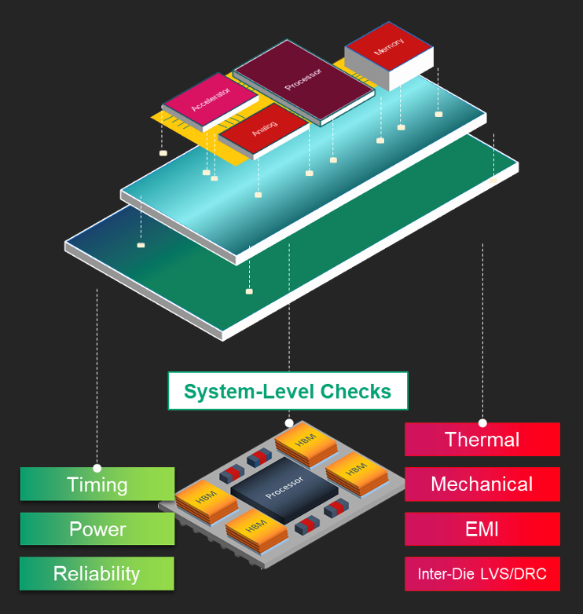

1985 年,KT 先生毕业后到Texas Instruments国防部门工作,参与了当时Texas Instruments规模最大的设计,有 9000 个晶体管。现在,有这么多器件的芯片上只要放置一个 I/O 就可以。但在当时,人们唯一关心的只是“功能是否正确”。渐渐地,我们需要检查设计的其他方面。现在,在“超越摩尔定律”的时代,我们担心的是如何一起完成所有复杂的系统级功能检查。

在电子设计 (EDA, Electronic Design Automation) 中,我们不再仅止于关注 IO-ring内的情况,而是需要同时关注 IO-ring外的各种性能问题。

在系统方面,设计的许多方面一直是彼此独立设计的。但由于缺乏集成的信息,往往导致单个裸片和封装出现过度设计而使得成本昂贵。

3D-IC 设计整合和管理

裸片放置和管脚bump 规划

没有单一的数据库来收集多种技术规范

跨越小芯片(chiplets)和封装的热分析

3D STA 和用于签核的时序工艺角数量猛增

系统级裸片间连接性验证

上下游跨域设计沟通

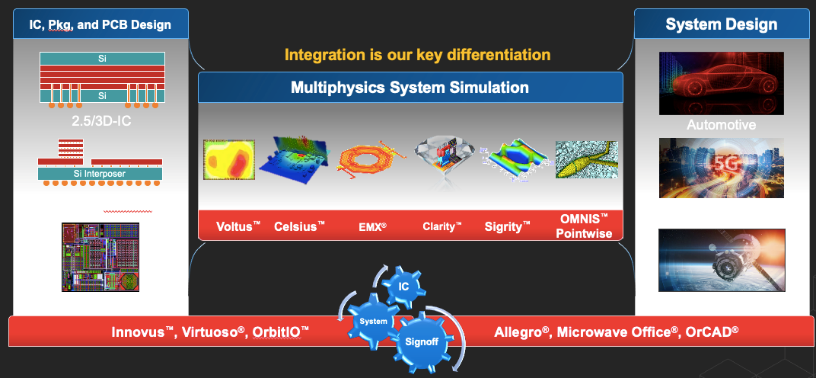

要解决现今工具缺乏集成的问题,显然就是开发更多的集成能力。下图显示了 Cadence针对“航空、火车和汽车”的主要工具集成,这些领域都含有电子元件及许多其他部件。这不仅仅是关于“IO 环内”的芯片,还包括外部的从电气和热分析到计算流体力学的一切。

“

以前可能只分析单独一块电路板,现在我们可以分析整个系统,并进行合理的计算。因为Cadence工具可以高效进行架构设计,因此用户不必拥有巨大的内存,而是可以使用在云上可用的无限计算能力——无论是在公有云还是在私有云上。

——KT Moore

”

设计工具的研发与并购

今天,我们用“超越摩尔定律”来讨论异构集成;但事实上,自 90 年代初业界开始探讨“多芯片模块 (multi-chip modules ,MCM)”以来,Cadence 就一直在深耕这个领域。当然,这远在摩尔定律开始失去动力之前。

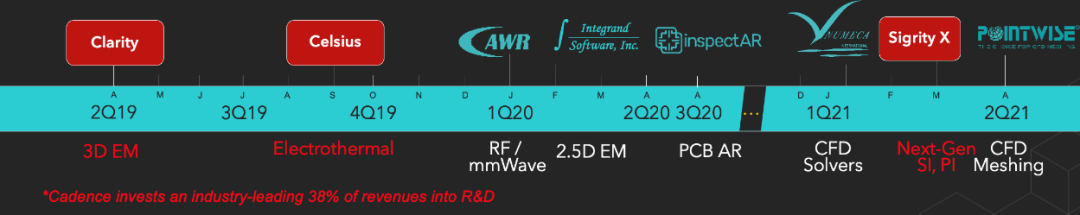

每家公司都面临一个共同的挑战:是在企业内部自行开发一款产品(有时称为“有机成长“),还是收购一家专攻某个领域的公司。在过去的两年里,Cadence 在系统领域构建了一个完整的产品组合,混合采用了这两种方法:

Clarity 家族,用于系统级电气分析的工具(内部开发)

Celsius家族,用于热分析的产品 (内部开发)

AWR家族,用于射频设计的产品 (收购)

Integrand 工具,用于 2.5D 芯片上的电磁分析(收购)

inspectAR工具,PCB 增强现实(AR)技术(收购)

Numeca技术,用于计算流体力学的求解器 (收购)

Sigrity X工具,用于下一代信号和电源完整性的产品(内部开发)

Pointwise家族,用于 CFD 网格划分的产品(收购)

其中,有一件事令业内人士都感到惊讶,那就是 Cadence 将 38% 的收入投资到研发之中,这一比例在行业内处于领先水平。在半导体设计和集成方面,总是会不断涌现新的要求。

设计完整性

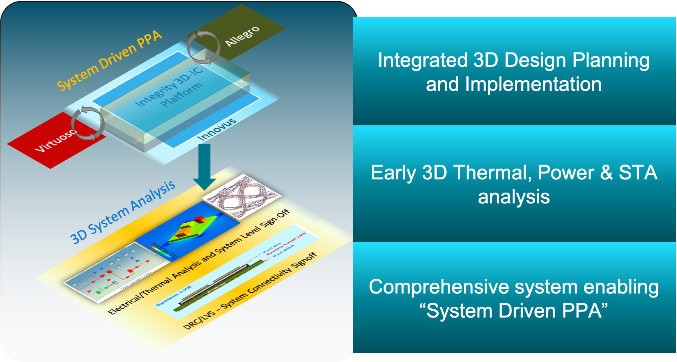

KT 最后谈到了 Integrity 3D-IC平台,这是一款专门针对堆叠裸片 3D 芯片设计的新产品。该工具可以进行 3D 规划(如传统在同一个层面上,称为布局规划)和设计实现。并且,它可以进行早期的 3D 热、功耗和时序分析。这些能力结合在一起,不仅在单个裸片的层面上,也在系统的层面上优化了 PPA。

“

PPA 是指功耗(Power)、性能(Performance)和面积(Area),这也是半导体领域的术语。我们谈论的是在实现最佳性能的同时,使芯片尺寸尽可能小、功耗尽可能低。设计师面对的问题是“这对于高级封装来说有什么不同?”其实没有什么不同,但是必须采取不同的方法。

……

归根结底,关键在于全面的集成。设计师需要知道,自己能够信心十足地完成设计。当开始组合这些异构设计时,有很多地方会出现问题。因此,Integrity 3D-IC平台融合了Cadence的布局和布线技术,以及仿真分析技术。我相信Cadence是目前唯一一家可以宣称将这些技术相互集成的公司,所以Cadence提供了真正的集成解决方案。这就是 EDA 的发展方向,我们正在与一些客户和合作伙伴携手合作,共同引领这一潮流。

——KT Moore

”

最后的问题

在主题演讲的最后,KT提出了最后一个问题:

我们应该让摩尔定律继续发展?还是追求超越摩尔定律?

答案您可能早已知晓,KT 的答案是我们需要两者兼顾。

-

半导体

+关注

关注

334文章

27253浏览量

217931 -

摩尔定律

+关注

关注

4文章

634浏览量

78983

发布评论请先 登录

相关推荐

2025电子设计与制造技术研讨会

飞腾成功举办散热技术应用发展研讨会

高算力AI芯片主张“超越摩尔”,Chiplet与先进封装技术迎百家争鸣时代

“自我实现的预言”摩尔定律,如何继续引领创新

启扬智能受邀参加2024恩智浦技术巡回研讨会

2024 ETAP 电气系统数字孪生平台技术研讨会(深圳站)

摩尔定律的终结:芯片产业的下一个胜者法则是什么?

行业资讯 I iMAPS 研讨会:摩尔定律,延续或超越?

行业资讯 I iMAPS 研讨会:摩尔定律,延续或超越?

评论