本期我们理论联系实际,把芯片CP测试真正的动手操作起来。基本概念介绍

1

什么是CP测试

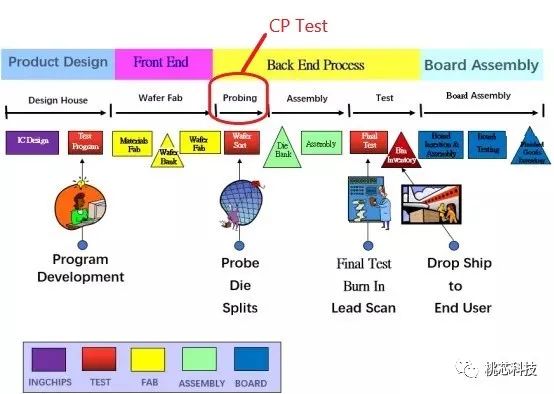

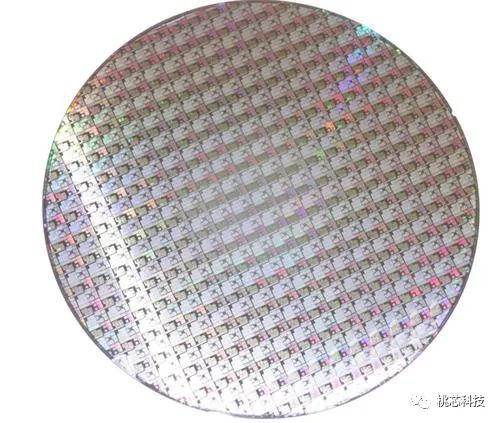

CP(Chip Probing)指的是晶圆测试。CP测试在整个芯片制作流程中处于晶圆制造和封装之间。晶圆(Wafer)制作完成之后,成千上万的裸DIE(未封装的芯片)规则的分布满整个Wafer。由于尚未进行划片封装,芯片的管脚全部裸露在外,这些极微小的管脚需要通过更细的探针(Probe)来与测试机台(Tester)连接。

在未进行划片封装的整片Wafer上,通过探针将裸露的芯片与测试机连接,从而进行的芯片测试就是CP测试。

图 1 CP Test在芯片产业价值链上的位置

图 2 Wafer上规则的排列着DIE(来源于网络)

2

为什么要做CP测试

Wafer制作完成之后,由于工艺原因引入的各种制造缺陷,分布在Wafer上的裸DIE中会有一定量的残次品。CP测试的目的就是在封装前将这些残次品找出来(Wafer Sort),从而提高出厂的良品率,缩减后续封测的成本。

而且通常在芯片封装时,有些管脚会被封装在内部,导致有些功能无法在封装后进行测试,只能在CP中测试。

另外,有些公司还会根据CP测试的结果,根据性能将芯片分为多个级别,将这些产品投放入不同的市场。

CP测试内容和测试方法

1

SCAN

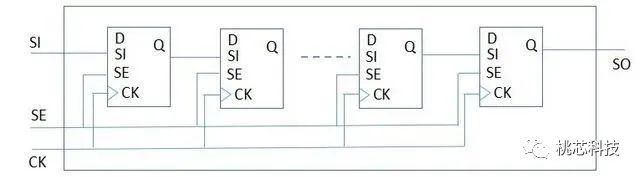

SCAN用于检测芯片逻辑功能是否正确。DFT设计时,先使用DesignCompiler插入ScanChain,再利用ATPG(Automatic Test Pattern Generation)自动生成SCAN测试向量。SCAN测试时,先进入Scan Shift模式,ATE将pattern加载到寄存器上,再通过Scan Capture模式,将结果捕捉。再进入下次Shift模式时,将结果输出到ATE进行比较。

图 3 Scan Chain示意图(来源于网络)

2

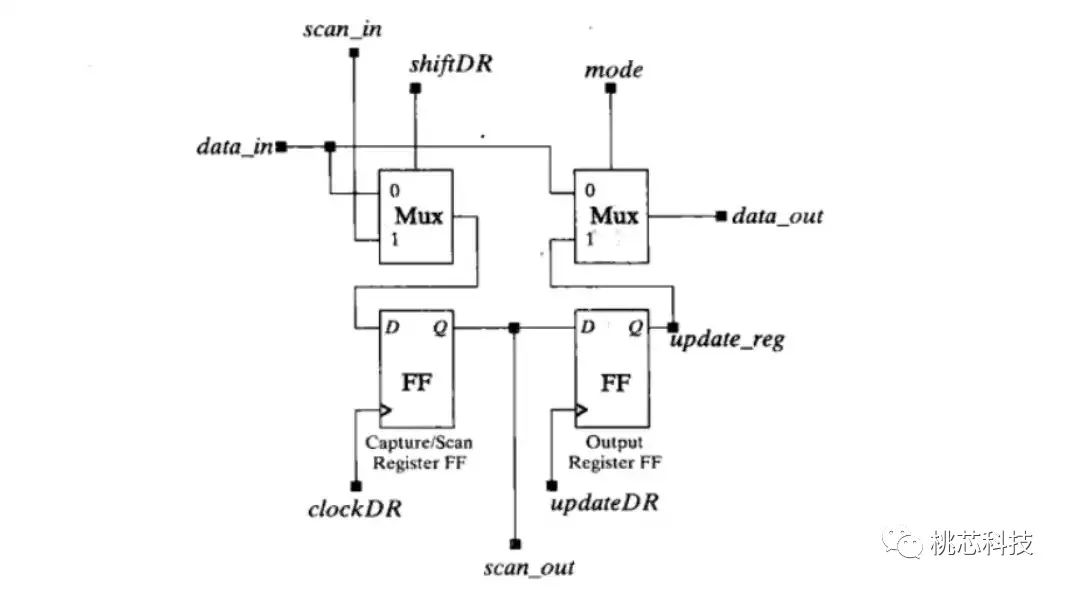

Boundary SCAN

Boundary SCAN用于检测芯片管脚功能是否正确。与SCAN类似,Boundary SCAN通过在IO管脚间插入边界寄存器(Boundary Register),使用JTAG接口来控制,监测管脚的输入输入出状态。

图 4 Boundary Scan原理图(来源于网络)

3

存储器

芯片往往集成着各种类型的存储器(例如ROM/RAM/Flash),为了测试存储器读写和存储功能,通常在设计时提前加入BIST(Built-In SelfTest)逻辑,用于存储器自测。芯片通过特殊的管脚配置进入各类BIST功能,完成自测试后BIST模块将测试结果反馈给Tester。

ROM(Read-Only Memory)通过读取数据进行CRC校验来检测存储内容是否正确。

RAM(Random-Access Memory)通过除检测读写和存储功能外,有些测试还覆盖DeepSleep的Retention功能和Margin Write/Read等等。

Embedded Flash除了正常读写和存储功能外,还要测试擦除功能。Wafer还需要经过Baking烘烤和Stress加压来检测Flash的Retention是否正常。还有Margin Write/Read、Punch Through测试等等。

4

DC/AC Test

DC测试包括芯片Signal PIN的Open/Short测试,电源PIN的PowerShort测试,以及检测芯片直流电流和电压参数是否符合设计规格。

5

RF Test

对于无线通信芯片,RF的功能和性能至关重要。CP中对RF测试来检测RF模块逻辑功能是否正确。FT时还要对RF进行更进一步的性能测试。

7

其他Function Test

芯片其他功能测试,用于检测芯片其他重要的功能和性能是否符合设计规格。

以上各项展开均有更复杂更细化的内容,此处不展开讨论,仅作粗略介绍。

CP测试流程

1

可测试性设计

DFT(Design For Test),可测试性设计。如第二节CP测试内容和测试方法所述,芯片测试中用到的很多逻辑功能都需要在前期设计时就准备好,这一部分硬件逻辑就是DFT。

DFT逻辑通常包含SCAN、Boundary SCAN、各类BIST、各类Function Test Mode以及一些Debug Mode。

测试人员需要在芯片设计之初就准备好TestPlan,根据各自芯片的规格参数规划好测试内容和测试方法。

芯片通常会准备若干种TestMode功能,通过配置管脚使芯片进入指定的测试状态,从而完成各个类型的测试。

对于SCAN和Boundary SCAN,需要插入ScanChain,根据芯片规模、Timing、SCAN覆盖率等参数,DFT工程师需要决定插入ScanChain的长短和数目。然后使用ATPG自动生成SCAN测试向量,覆盖率决定了测试向量的长短。为了节约成本还要对ScanChain进行压缩。然后再进行功能仿真和SDF仿真,保证功能和Timing满足要求。ATPG可输出WGL或STIL格式文件供Tester使用。细节还有很多,这里不再展开叙述了。

BIST(Built-In SelfTest)逻辑。这些自测逻辑完成对ROM/RAM/Flash等功能的测试。

Function Test Mode。一些专门的功能测试需要增加硬件逻辑,例如ADC/DAC/时钟等

2

选测试厂,测试机

测试厂和测试机的选择要考虑芯片类型、测试内容、测试规格和成本等因素。

一套芯片测试设备称为ATE(Automatic Test Equipment),由机台(Tester)、Loadboard、Probe Card、Handler和测试软件等部分组成。CP测试ATE不需要Loadboard和Handler。

图5,ATE机器

按照侧重的芯片类型和测试内容分,测试机台有很多品牌和产品系列:

例如存储器芯片Advantest T55xx 系列等、数字混合信号或SoC芯片Teradyne J750 系列等,RF射频芯片Credence ASL-3000 系列等。

3

制作ProbeCard以及Test Program

选择好测试机后,硬件方面需要制作ProbeCard,软件方面需要制作Test Program。

ProbeCard是探针卡。

ProbeCard包括探针和芯片外围电路。裸DIE规则的布满整个Wafer,无论哪片Wafer,每颗DIE都有固定的位置,芯片管脚的位置也就固定。这些位置坐标和间距都信息在芯片投产前已经确定,制作针卡需要这些参数。探针有钨铜、铍铜或钯等材料,这些探针在强度、导电性、寿命、成本等方面各有特点。

针卡还需要确定同测数(Site)。增加同测数可以节约测试机时成本,但是受限于测试机台资源,同测数有上限,例如32/16/8/4。

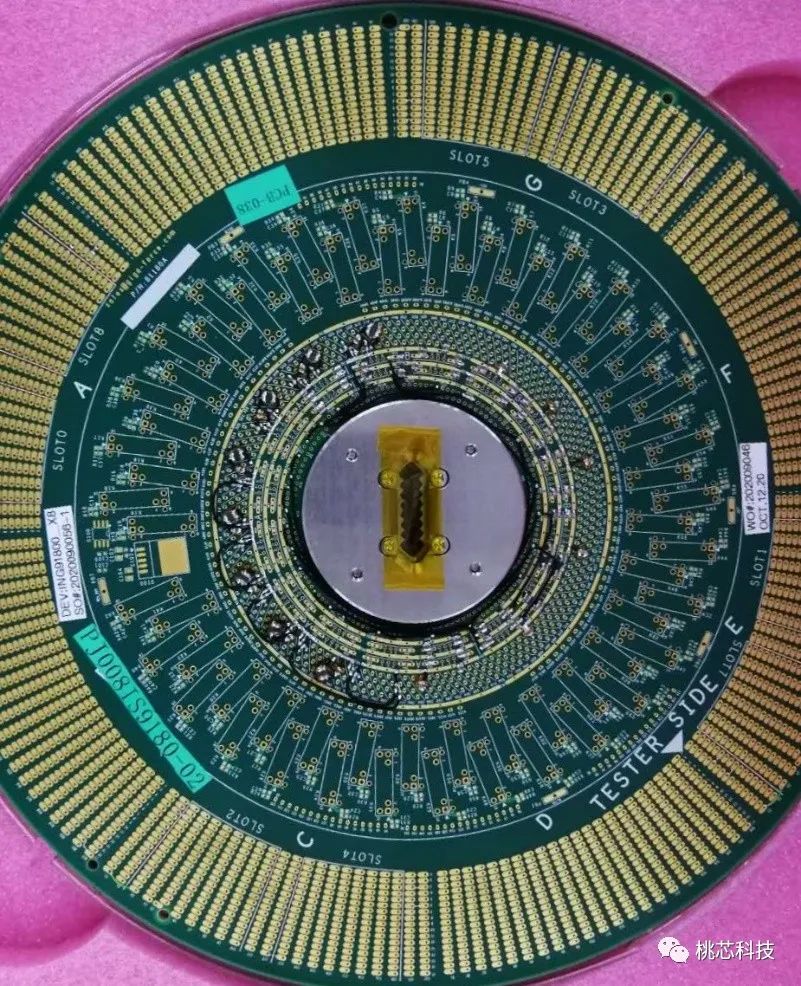

图6,ProbeCard照片

Test Program是测试程序。

测试程序控制整个机台的测试过程。

不同的测试机有不同的测试软件系统,对应的测试程序也有不同的格式。通常工程师提供WGL/STIL/VCD等格式的文件,再转换成测试机需要的文件格式,并增加其他测试程序。

4

调试以及结果分析

Wafer由Foundry出厂转运至测试厂,ATE软硬件就绪后就可以开始进行调试了。

根据TestPlan,Pattern(测试向量)被分作不同的BIN,从而定位测试错误的位置。调试时还可以在系统上直接看到一个Pattern中错误的Cycle位置,工程师根据这些错误信息进行debug,修改Pattern和测试程序,逐个清理,直到所有BIN都PASS。

同测的多Site全部PASS,Loop多轮后,便可以在整片Wafer上Try Run。此时工程师还要调试探针力度、清理探针周期等参数,确保整片Wafer上每一次Touchdown都可以测试稳定。

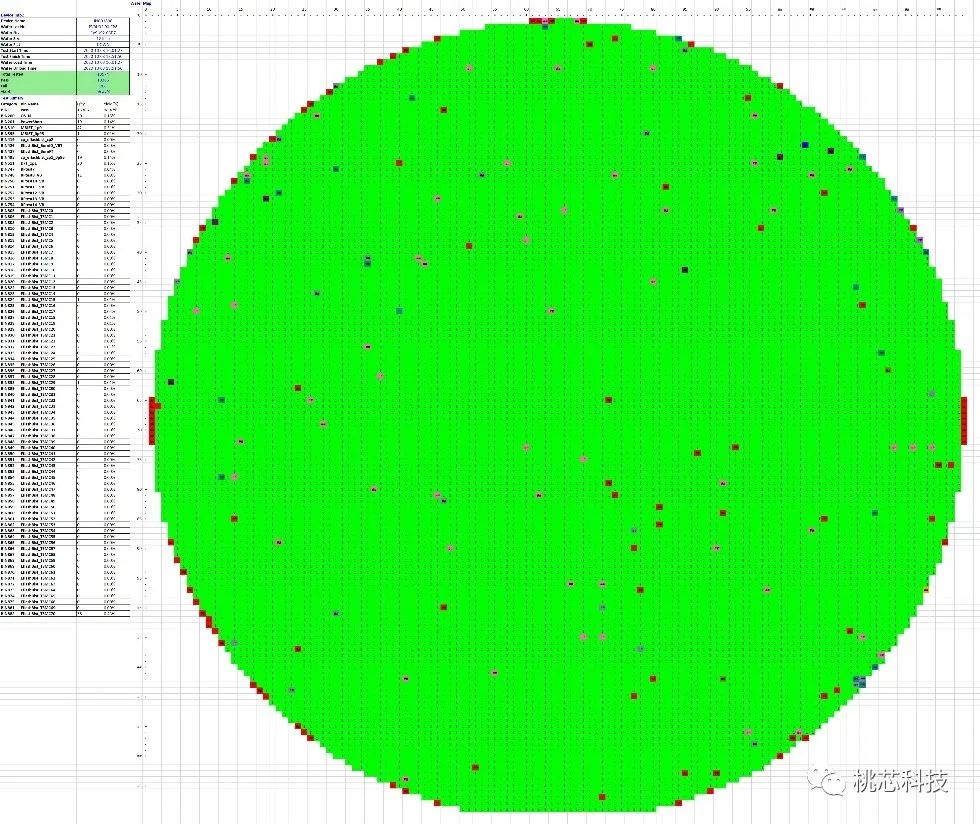

整片Wafer的测试结果通常生成一个WaferMap文件,数据生成一个datalog,例如STD文件。WaferMap主要包含良率、测试时间、各BIN的错误数和DIE位置,datalog则是具体的测试结果。工程师通过分析这些数据,决定是否进入量产。

图7,WaferMap截图

5

量产

进入量产阶段后,根据大量测试的统计数据,可以进行一些调整以进一步优化测试流程。

根据结果将错误率较高的BIN尽量排在靠前的位置,测试进行到第一个出错的BIN后就不在继续向下进行,以节省测试时间,并且防止已发现的错误导致后续测量损坏针卡。

将错误率较低的BIN排在靠后的位置,当错误率极低时,甚至删除该测试,以节省测试时间。

决定是否对出错的DIE进行复测。由于各种原因,对于出错的DIE,再重新测试一次可能会PASS。通常复测可以纠正一定比例的错误,但是要多用一部分测试时间,所以要综合考虑决定是否复测。

通常处于Wafer边缘位置的DIE出错的概率较高,综合考虑,有时可以直接将边缘DIE剔除,不进行测试就标为坏品,以节省测试时间。

还需要关注良率是否稳定,当连续出现良率较低的情况时,需要停止测试,进行数据分析,检查设备或与Foundry沟通。

量产CP测试的结果需要交给后续封装厂使用。通常是一个含有分BIN信息的Map文件,封装厂根据Map文件挑选好品封装,剔除坏品,还可以保留客户选择的特殊BIN别。

成本控制

CP测试成本由前期一次性投入的固定成本和后期量产的可变成本组成。

1

固定成本

固定成本包含DFT开发以及面积和功耗、ProbeCard制作和养护,Test Program制作和调试。

DFT开发以及面积和功耗

DFT有开发成本。并且DFT硬件逻辑将占用一部分芯片面积(虽然很小),DFT要提高效率,减小面积和功耗。

ProbeCard制作

ProbeCard有公板和专板两种。顾名思义,公板是公用板,专板是专用板。公板是在已有的板子上通过飞线等方式组成芯片外围电路,制作成本低,制作周期短,适用于对测试规格要求不高的CP测试。专板是为自家芯片专门制作的板子,适用于对外围电路要求高,测试规格精密的芯片,设计和制作成本高,周期长。

ProbeCard上的探针材料和探针数也影响成本。各种材料的探针各有特点,价钱也不同,这里不再展开。减少探针数量也能降低成本。

在资源允许的条件下要尽可能的增加同测数,多Site同测可以减少测试时间成本。

Test Program制作和调试

Test Program有开发成本。调试时需要机台,有调试机时成本。还需要一片调试Wafer,调试过程中反复Touchdown会导致该片Wafer上的若干DIE无法再进行封装。

2

可变成本

可变成本主要就是量产测试时间。量产测试时间是整个CP测试成本中的最重要组成。而且测试前期投入固定成本后,今后量产的全部成本几乎都在测试时间成本上。直接影响测试时间的内容主要有:DFT效率、同测数、Test Program效率和一些量产策略。

DFT效率

DFT测试执行的高效直接影响单个DIE的测试时间。因此在芯片设计之初,DFT就要考虑到测试效率。减少测试时间,提高覆盖率,这对节约成本至关重要。

提高测试时钟;Scan使用压缩模式;缩减TestMode上电时间;检查测试计划,缩减不必要的测试项;检查测试策略是否合理,优化测试方案等等。一切DFT设计以提高效率为根本原则,既要高覆盖率,又要缩减时间。有时这两者之间的矛盾则需要相互权衡。

同测数

在资源允许的条件下要尽可能的增加同测数,多Site同测可以减少测试时间成本。

Test Program效率

和DFT效率相比,测试程序效率作用不大,但是合理安排测试程序还是可以缩减测试时间。例如在程序中减少不必要的等待时间;多个测试项并行进行等。

一些量产策略

如关于量产一节所述,一些量产的策略可以节约测试时间。

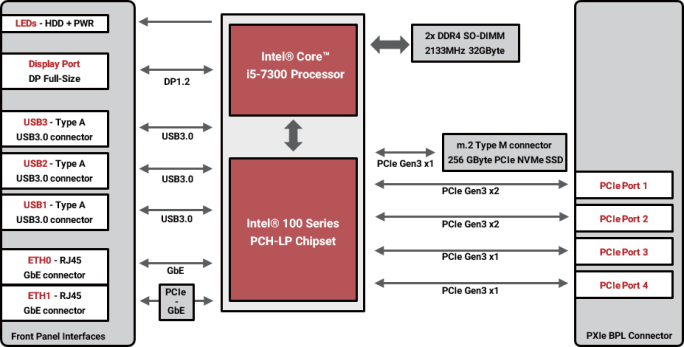

联合仪器自主研发设计的3U控制器UI-X8101是一款极其紧凑且功能强大的3U单插槽嵌入式控制器,适用于PXI Express和CPCIexp 平台。凭借面向未来的丰富接口功能,可以在大多数测试与测量应用中完美运行。内置第七代Intel Core处理器,配备高达32GB DDR4的内存,支持PCIe Gen3总线协议,轻松适应高带宽应用。

产品特点

•符合PXI-5PXIExpress硬件规范Rev.2.0

•最大系统吞吐量6GB/s1

•集成m.2NVMePCIeGen3存储器

•第7代带超线程的IntelCore

•市面上极为紧凑的PXIe嵌入式控制器

•可定制BIOS

•四链路模式PCIeGen3x2- x2- x1- x1

如果您想了解更多联合仪器相关产品,可点本文左上方蓝字关注公众号,获得联合仪器中国区总代理——北京汉通达科技发布的芯片测试最新技术,经典应用案例及最新产品信息。

-

芯片

+关注

关注

459文章

51566浏览量

429752 -

测试

+关注

关注

8文章

5469浏览量

127431

发布评论请先 登录

相关推荐

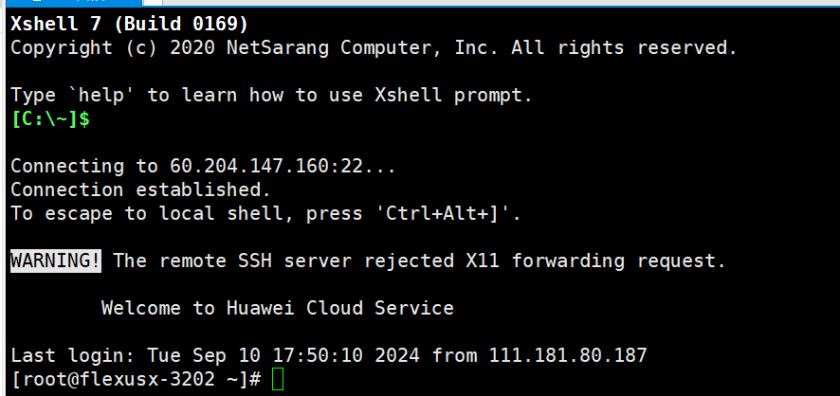

云服务器 Flexus X 实例,镜像切换与服务器压力测试

季丰电子完成自研Acco8200_CP_Generic_Board公板测试验证

CP测试与FT测试有什么区别

tga2963-cp

TGA2623-CP

TGA2622-CP

TGA2590-CP

TGA2578-CP

TGA2239-CP

TGA2238-CP

芯片测试有哪些 芯片测试介绍

CP测试实例

CP测试实例

评论