IP核(Intellectual Property core)是一段具有特定电路功能的硬件描述语言程序,常常被用于数字电路中。该程序与集成电路工艺无关,可以移植到不同的半导体工艺中去生产集成电路芯片,从而帮助开发人员减少工作量,并加快产品上市。

IP核(Intellectual Property core)是一段具有特定电路功能的硬件描述语言程序,常常被用于数字电路中。该程序与集成电路工艺无关,可以移植到不同的半导体工艺中去生产集成电路芯片,从而帮助开发人员减少工作量,并加快产品上市。

在以往文章中,我们介绍了高可靠性无缝冗余协议HSR(IEC 62439-3-Clause 5)的相关概念。这是一项兼容性好、易于使用的冗余协议,能够通过环形网络双向发送数据包来提供冗余。在环中断的情况下,支持HSR的目标节点则通过另一个端口接收帧。

点此查看更多虹科HSR/PRP技术文章和相关产品

但是,如果时序和带宽使用限制很严格,则需要在HSR节点中添加时序平面,以便按计划的方式传送数据流量。IEEE 1588协议推动了构建确定性 HSR 解决方案的进行,该解决方案专注于电力或国防等关键行业,比起通用的TSN解决方案,这些行业更倾向于使用HSR等更简单的基于硬件的强大解决方案。

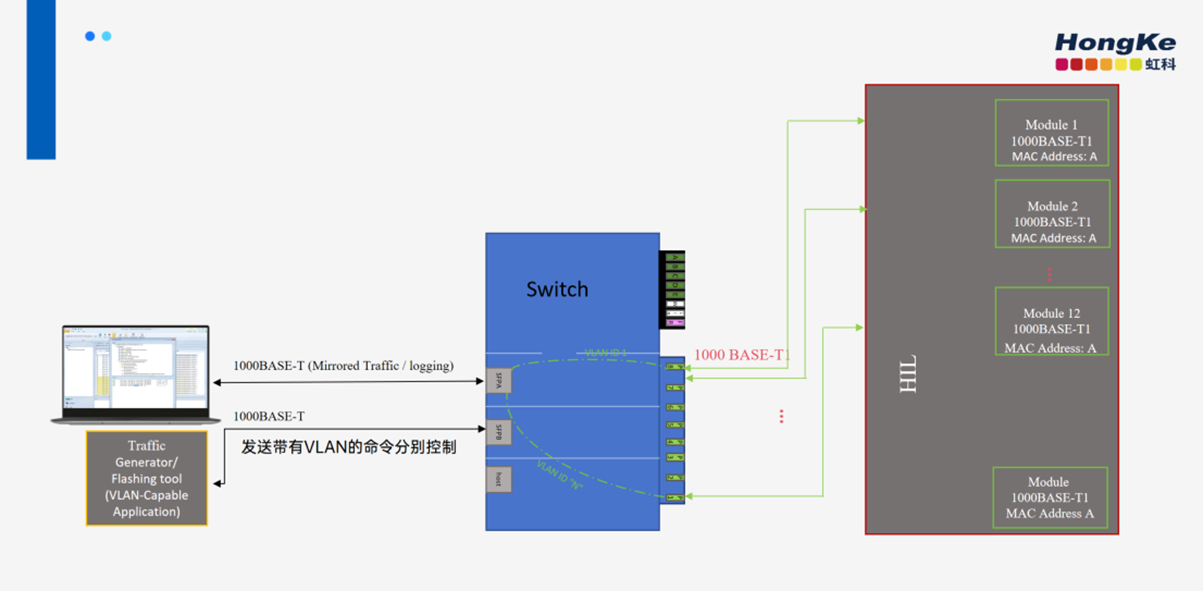

基于此,虹科推出了确定性HSR IP核(DHSR IP core)。这是一个基于硬件的专有解决方案,针对可重构设备进行了优化,如果 IEC 发布确定性高可靠性无缝冗余的最终互操作标准,则可以进行升级。

Key Features

虹科DHSR IP core的关键特性

• HSR中的确定性精确帧发送

•基于精确时钟同步的循环时分复用

• HSR/PRP 交换机 IP core中列出的常规功能:点击查看虹科方案 | 虹科HSR/PRP IP核:全硬件解决方案,可在低成本的FPGA上实现

“

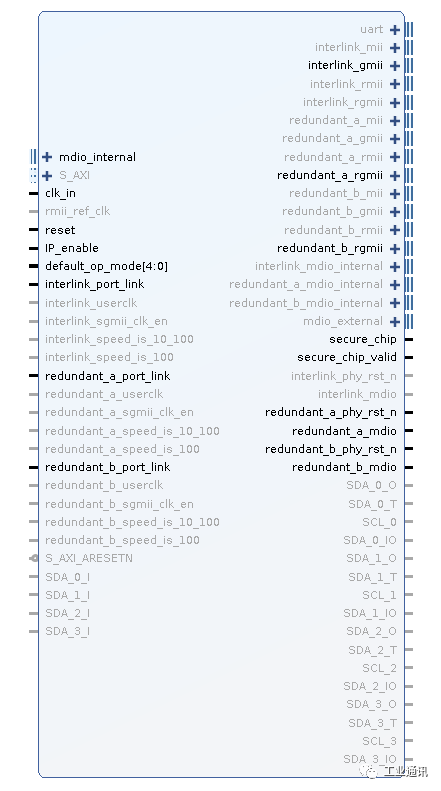

虹科HSR-PRP交换机IP核

虹科HSR-PRP交换机IP核是一个完整的硬件解决方案,可实现高可靠性无缝冗余协议和并行冗余标准,并能够在低成本的FPGA上实现。它通过硬件来交换帧,这样可以提供很高的交换速度,同时这也是实现变电站自动化的过程总线和机架间总线的最大允许使用年限和数据完整性所必需的。它是针对能源市场设备的一种灵活解决方案,该设备将连接到HSR环、PRP局域网或在IEC 61850的环境下起到网桥的作用。

-

交换机

+关注

关注

21文章

2624浏览量

99307

发布评论请先 登录

相关推荐

以太网交换机高稳定性时钟系统应用方案

虹科应用 增强型以太网交换机:如何实现同IP控制的高效网络管理?

华为交换机常用命令大全

交换机怎么配置IP地址

虹科案例丨VLAN不再难懂:一台转换器+交换机轻松解锁VLAN配置

ETAS推出Time-Triggered Scheduling (TTS)的确定性调度解决方案

光路科技TSN工业交换机FR-TSN4206成功通过“时间敏感网络产业链名录计划”检测认证,为确定性网络应用提供强

POE交换机是什么?POE交换机的特点

交换机的作用与功能 交换机的基本配置

汇聚交换机和核心交换机区别

国产交换机产品,裕太微解决方案(YT9215x、YT9218x)

交换机连接应用解决方案

虹科方案 | 确定性HSR交换机IP核,基于硬件的专用解决方案

虹科方案 | 确定性HSR交换机IP核,基于硬件的专用解决方案

评论