美浦森超结MOS在照明电源中的应用

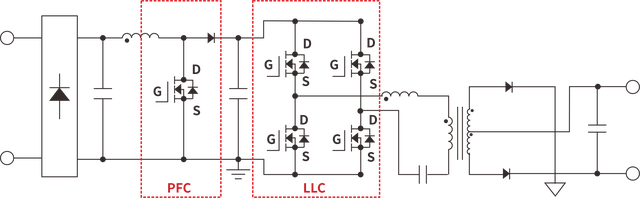

随着电源技术和功率器件以及通信技术的发展,目前的照明产品越来越趋向于智能化,小型化。对电源的体积和功率密度的要求也越来越高。因此,越来越多的新型半导体器件也逐渐应用到LED照明产品上,比如超结MOS的应用就越来越普遍,许多LED电源厂商以开始用超结MOS去替代VDMOS,在达到高效率的同时,更节省了电源空间和生产成本。今天我们来讨论一下在照明行业中改如何选择合适的超结MOS。

首先,我们需要了解超结MOS和VDMOS的优缺点,以及在照明产品中我们应该注意MOS的哪些重要参数。

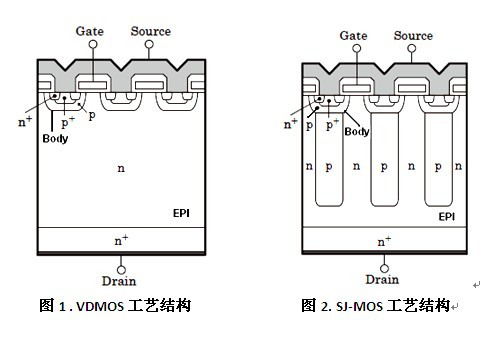

一、超结MOS与VDMOS的结构差异

为了克服传统MOS导通电阻与击穿电压之间的矛盾,一些人在VDMOS基础上提出了一种新型的理想器件结构,称为超结器件或SJ-MOS,他们的结构如图1和图2所示,其由一些列的P型和N型半导体薄层交替排列组成。在截止态时,由于P型和N型层中的耗尽区电场产生相互补偿效应,使P型和N型层的掺杂浓度可以做的很高而不会引起器件击穿电压的下降。导通时,这种高浓度的掺杂可以使其导通电阻显著下降,大约有两个数量级。因为这种特殊的结构,使得SJ-MOS的性能优于传统的VDMOS.

二、超结MOS的优点

1、通态阻抗小,通态损耗小。

由于超结MOS的Rdson远远低于VDMOS,在系统电源类产品中超结MOS的导通损耗必然较之VDMOS要减少的多。其大大提高了系统产品上面的单体MOSFET的导通损耗,提高了系统产品的效率。

2、同等功率规格下封装小,有利于功率密度的提高。

首先,同等电流以及电压规格条件下,超结MOS的晶圆面积要小于VDMOS工艺的晶圆面积,这样作为MOS的厂家,对于同一规格的产品,可以封装出来体积相对较小的产品,有利于电源系统功率密度的提高。

其次,由于超结MOS的导通损耗的降低从而降低了电源类产品的损耗,因为这些损耗都是以热量的形式散发出去,我们在实际中往往会增加散热器体积来降低MOS单体的温升,使其保证在合适的温度范围内。由于超结MOS可以有效的减少发热量,减小了散热器的体积,对于一些功率稍低的电源,甚至使用超结MOS后可以将散热器彻底拿掉。有效的提高了系统电源类产品的功率密度。

3、栅电荷小,对电路的驱动能力要求降低。

传统VDMOS的栅电荷相对较大,我们在实际应用中经常会遇到由于IC的驱动能力不足造成的温升问题,部分产品在电路设计中为了增加IC的驱动能力,确保MOSFET的快速导通,我们不得不增加推挽或其它类型的驱动电路,从而增加了电路的复杂性。超结MOS的栅电容相对比较小,这样就可以降低其对驱动能力的要求,提高了系统产品的可靠性。

4、结电容小,开关速度加快,开关损耗小。

由于超结MOS结构的改变,其输出的结电容也有较大的降低,从而降低了其导通及关断过程中的损耗。

同时由于超结MOS栅电容也有了响应的减小,电容充电时间变短,大大的提高了超结MOS的开关速度。对于频率固定的电源来说,可以有效的降低其开通及关断损耗。提高整个电源系统的效率。

三、超结MOS系统应用可能会出现的问题

1、EMI可能超标。

由于超结MOS拥有较小的寄生电容,造就了超结MOS具有极快的开关特性。因为这种快速开关特性伴有极高的dv/dt和di/dt,会通过器件和印刷电路板中的寄生元件而影响开关性能。对于在现代高频开关电源来说,使用了超结MOS,EMI干扰肯定会变大。

2、栅极震荡。

功率MOSFET的引线电感和寄生电容引起的栅极震荡,由于超结MOSFET具有较高的开关dv/dt。其震荡现象会更加突出。这种震荡在启动状态、过载状况和MOSFET并联工作时,会发生严重问题,导致MOSFET失效的可能。

3、抗浪涌及耐压能力差。

由于超结MOS的结构原因,很多厂商的超结MOS在实际应用推广替代VDMOS的过程中,基本都出现过浪涌及耐压测试不合格的情况。这种情况在通信电源及雷击要求较高的电源产品上,表现的更为突出。这点必须引起我们的注意。

4、漏源极电压尖峰比较大。

在反激的电路拓扑中,由于本身电路的原因,变压器的漏感、散热器接地、以及电源地线的处理等问题,不可避免的要在MOSFET上产生相应的电压尖峰。针对这样的问题,反激电源大多选用RCD SUNBER电路进行吸收。由于超结MOS拥有较快的开关速度,势必会造成更高的VDS尖峰。如果反压设计余量太小及漏感过大,更换超结MOS后,极有可能出现VD尖峰失效问题。

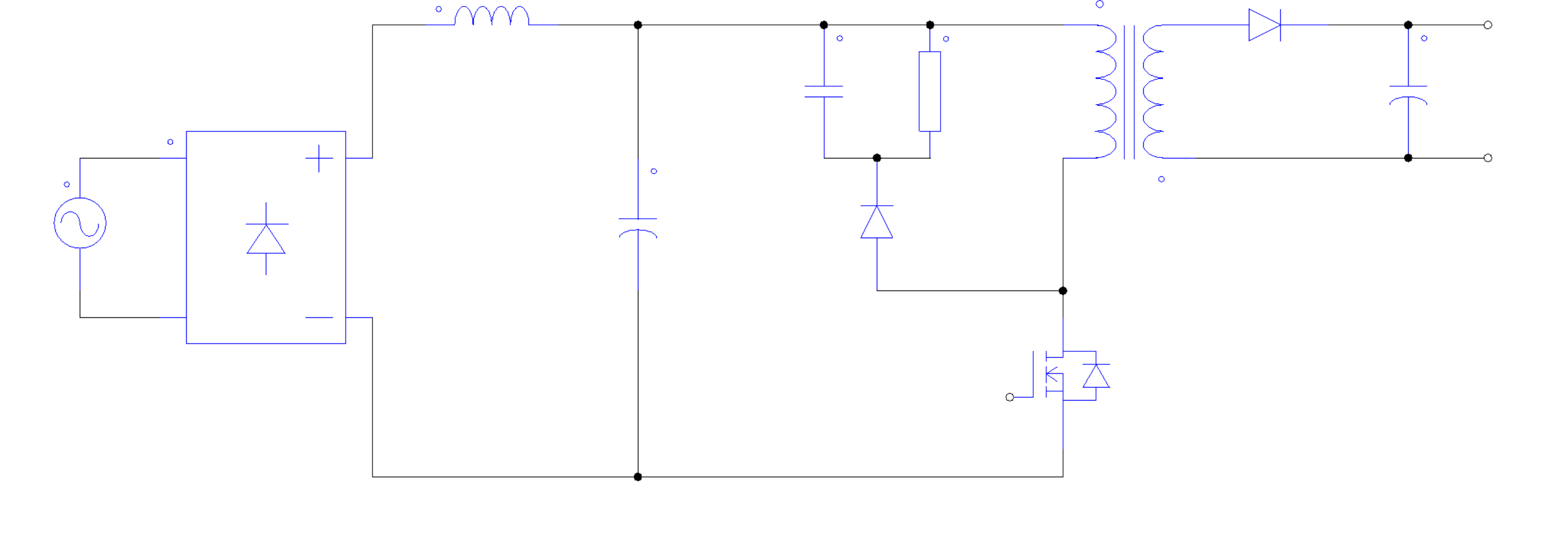

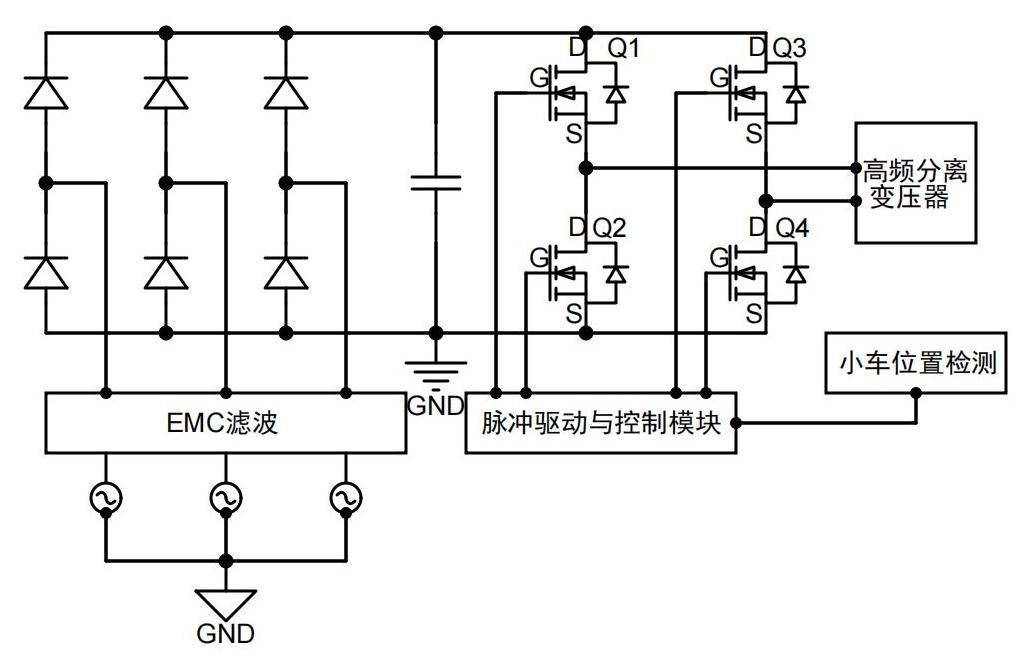

目前我们在100W内的照明市场主要采用的是PSR拓扑结构,如图3:

在这种结构下,超结MOS相比VDMOS,其远低于VDMOS的Rdson和小封装体积的优势非常明显。例如,我们可以用252的封装外型去替代220F,在节省了散热器的同时,还能保证较高的效率和较低的温升,也更加利于生产。

同时,在这种构架下,超结MOS的EMI和浪涌较差的缺点也非常突出。由于前端没有滤波电解电容,在浪涌冲击时,Vbus电压会升的很高,随着Ton的减小,ID电流变大,Vds会升的很高,对MOS的雪崩能力要求比较高。

如图,在同样的浪涌情况下,超结MOS失效的可能性更高。这就要求我们在选择超结MOS的时候,必须重点考虑MOS的雪崩能力。

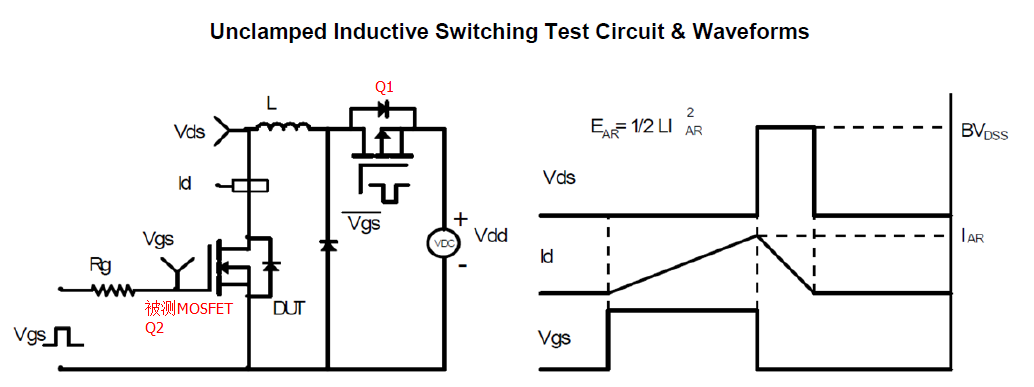

我们知道MOSFET的规格书中,EAS的指标值直接反应了MOS的抗浪涌能力。而实际中,我们看到各个厂家在此参数上的值相去甚远,这主要是因为各个厂家的测试条件不一样。通用的EAS测试电路如下:

由图可知,L和I的取值不同,实测的EAS值也不同。一般情况下会采用较小的L以及较大的I进行测试。我们在选择超结MOS时,应以相同测试条件下EAS值较大的为优。

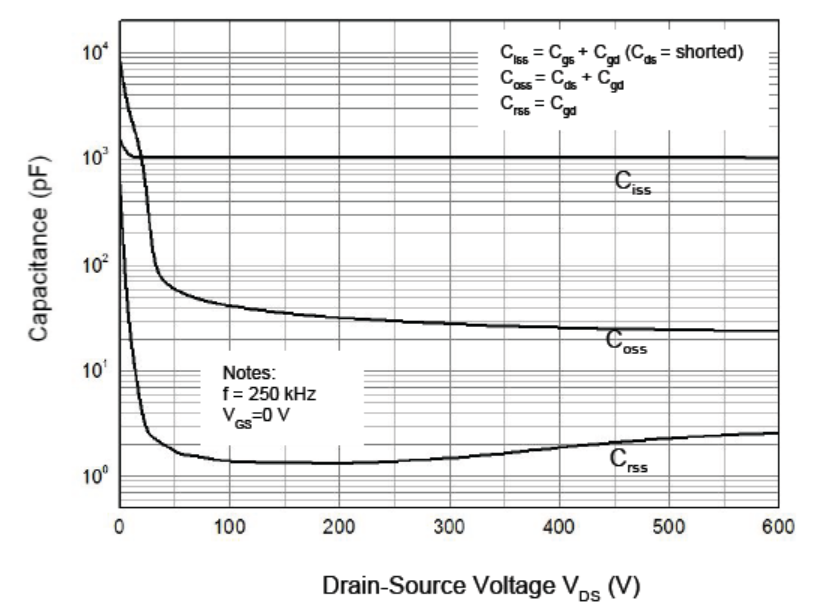

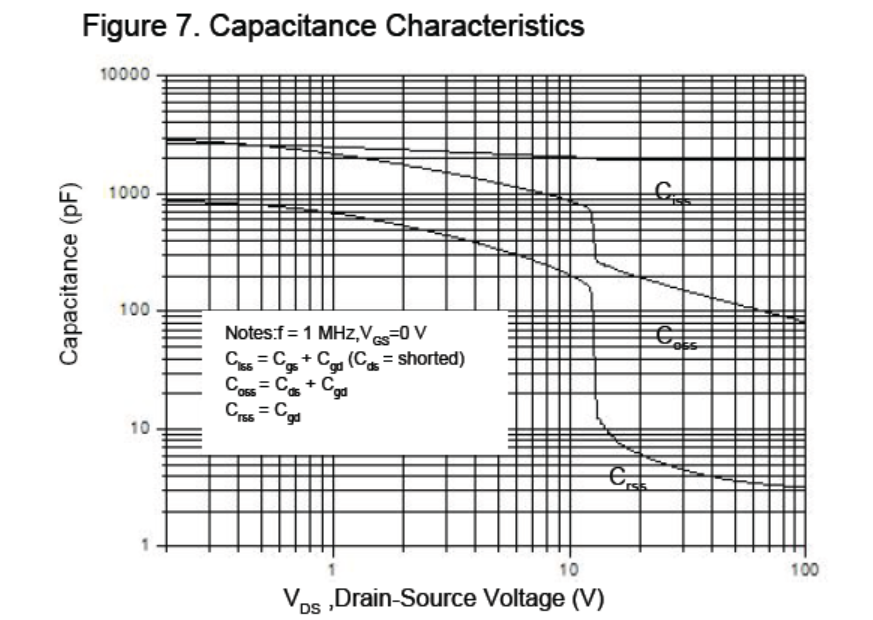

另外,由于超结的Qg很小,在快速开关中会产生较大的dv/dt和di/dt,从而造成EMI困扰。实际选用时,我们应关注MOS的电容的特性。如下图:

芯晶图电子潘17633824194

芯晶图电子潘17633824194为12A的VDMOS和12A的超结MOS的电容曲线特性对比。超结MOS的电容特性突变更大。由此带来更差的EMI效果。

-

芯片

+关注

关注

455文章

50851浏览量

423863 -

电子元器件

+关注

关注

133文章

3345浏览量

105514 -

MOSFET

+关注

关注

147文章

7178浏览量

213384 -

IC

+关注

关注

36文章

5953浏览量

175649

发布评论请先 登录

相关推荐

如何选择合适的mos管 mos管在电源管理中的作用

MOS管在LED驱动电源中的应用

美浦森半导体亮相2024慕尼黑上海电子展

SLD60N02T 规格书 60A 20V美浦森 贴片TO-252MOS管

SLD60N02T美浦森 TO-252封装 60A 20V MOS管

碳化硅MOS、超结MOS与IGBT性能比较

美浦森超结MOS在照明电源中的应用

美浦森超结MOS在照明电源中的应用

评论