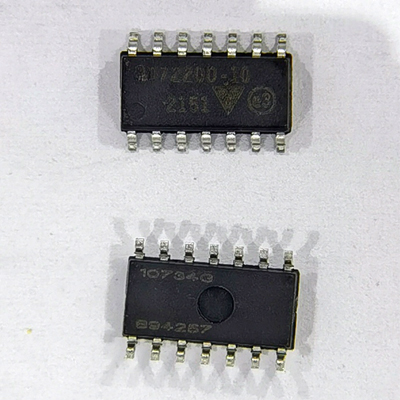

3D7220 10 抽头延迟线产品系列包括固定延迟CMOS集成电路。 每个包都包含一条延迟线,在时间均匀分布的 10 个点上轻敲和缓冲。 点对点(增量)延迟值的范围可以从 0.75ns 到 700ns。 这输入在没有反转的情况下在输出端再现,时间偏移为根据用户指定的破折号。 3D7220 兼容 TTL 和 CMOS,能够驱动十个 74LS 型负载,并具有上升沿和下降沿精度。全CMOS 3D7220集成电路被设计为混合 TTL 固定延迟线的可靠、经济的替代方案。 它是提供标准 14 针可自动插入 DIP 和节省空间表面贴装 14 引脚 SOIC 和 16 引脚 SOL 封装。

特征

• 全硅、低功耗 CMOS 技术

• TTL/CMOS 兼容输入和输出

• 气相、IR 和波峰焊

• 可自动插入 (DIP pkg.)

• 低地反弹噪声

• 前沿和后沿精度

• 延迟范围:0.75ns 至 7000ns

• 延迟容差:2% 或 0.5ns

• 温度稳定性:±2% 典型值(-40C 至 85C)

• Vdd 稳定性:±1% 典型值 (4.75V-5.25V)

• 最小输入脉冲宽度:总延迟的 15%

• 14 针 Gull-Wing 可插入式

替代混合延迟线

3D7220D 33

3D7220D -1

3D7220D -1.5

3D7220D -2

3D7220D -2.5

3D7220D -4

3D7220D -5

3D7220D -10

3D7220D -20

3D7220D -50

3D7220D -100

3D7220D -700

3D7220 33

3D7220 -1

3D7220 -1.5

3D7220 -2

3D7220 -2.5

3D7220 -4

3D7220 -5

3D7220 -10

3D7220 -20

3D7220 -50

3D7220 -100

3D7220 -700

发布评论请先 登录

相关推荐

【Moldex3D丨产品技巧】使用金线精灵与样板快速建立金线组件

ADC10D1000/ADC10D1500低功耗ADC数据表

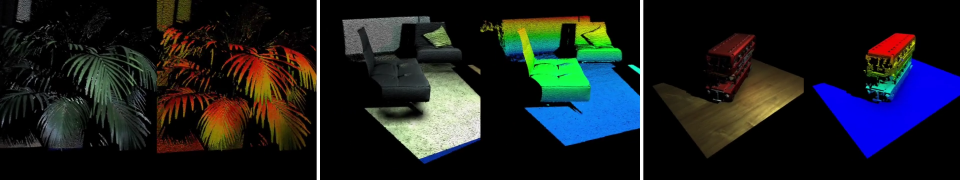

高分工作!Uni3D:3D基础大模型,刷新多个SOTA!

SOLIDWORKS 3D CAD 2024的10大新增功能

2D与3D视觉技术的比较

3D视觉的三大优势

3D7220D-10延时线

3D7220D-10延时线

评论