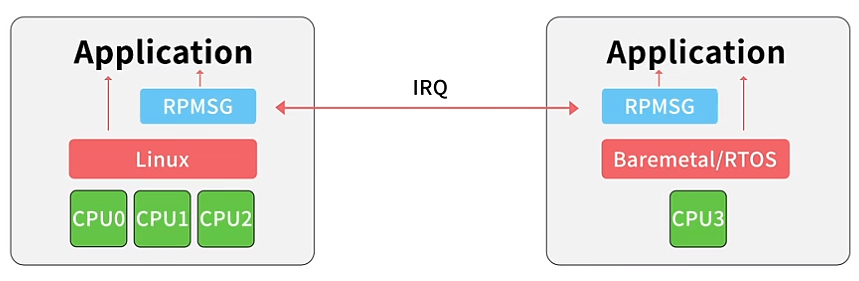

现代工业设备系统要求越来越复杂,既要强大的多任务的事务处理能力,又需要低延时实时任务处理能力的需求,特别是工业自动化控制领域(如数控机床、机械臂)、电力监测领域(如DTU、继保设备、一二次融合设备)等应用场景尤为迫切。为了满足日益复杂的系统要求,创龙科技推出了基于Xilinx Zynq-7020/7010实现的双系统解决方案。

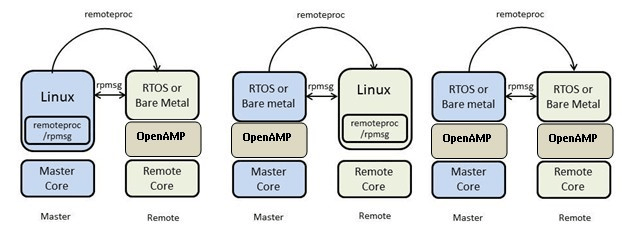

Xilinx Zynq-7020/7010是一款集成双核ARM Cortex-A9 + Artix-7 FPGA架构的单芯片SoC,它的OpenAMP框架可实现双核ARM Cortex-A9非对称使用方案,从而使双核ARM实现分别跑两个系统:一个ARM Cortex-A9跑Linux,一个ARM Cortex-A9作为实时核跑RTOS(FreeRTOS)或者裸机。实时核与FPGA端进行低延时的高速数据交换与实时通讯控制,从而满足低延时的实时任务要求。而跑Linux的 ARM核作为更上层应用,处理更复杂的业务事务。

Xilinx Zynq-7020/7010单芯片SoC方案配合双系统的应用为工业控制、电力一二次融合设备、医疗电子、测试测量、汽车电子、通信等应用提供了更灵活、更具成本优势的解决方案。

1、echo_test案例

1.1 案例功能

案例功能:CPU0使用RPMsg向CPU1发送数据,CPU1接收到数据后再使用RPMsg向CPU0回传数据。CPU0对回传的数据进行验证,并输出验证结果。

1.2 操作说明

将CPU1裸机或FreeRTOS可执行文件复制到评估板文件系统“/lib/firmware/”目录下,并执行如下命令加载CPU1程序。

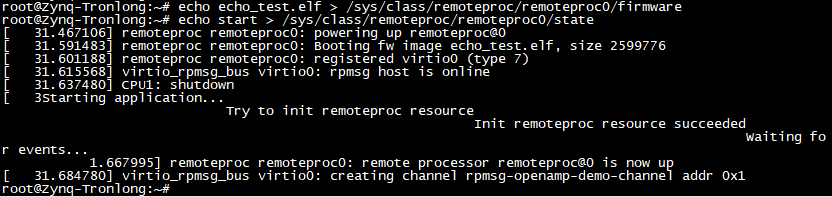

Target# echo echo_test.elf > /sys/class/remoteproc/remoteproc0/firmware

Target# echo start > /sys/class/remoteproc/remoteproc0/state

图 3

执行如下命令加载RPMsg驱动,并在“/dev/”目录下生成RPMsg设备节点。

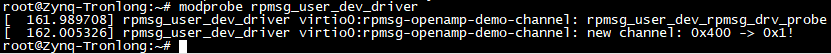

Target# modprobe rpmsg_user_dev_driver

图 4

将CPU0应用程序可执行文件复制到评估板文件系统,并执行如下命令通过RPMsg与CPU1进行通信。

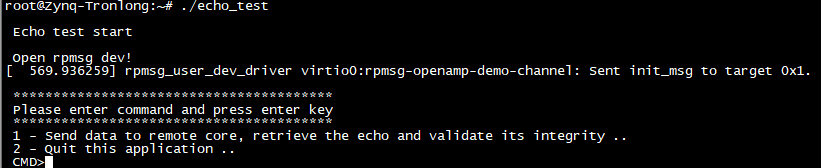

Target# ./echo_test

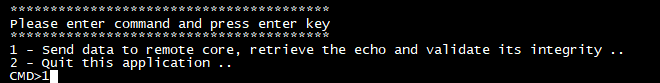

图 5

输入1,并按回车键进行测试。

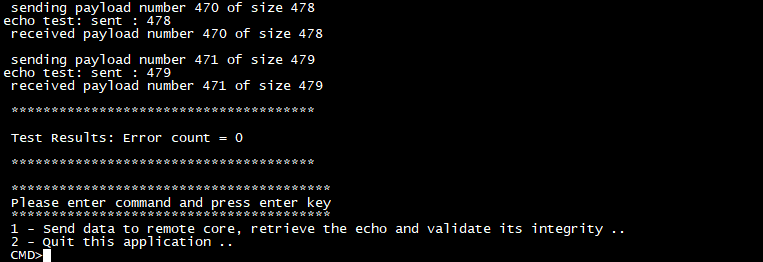

图6

图7

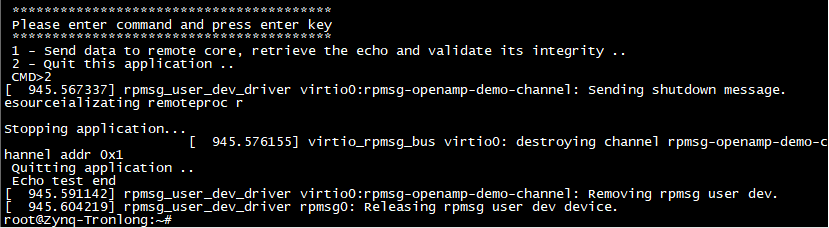

输入2,并按回车键退出测试。

图 8

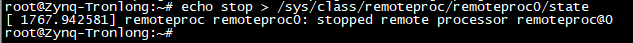

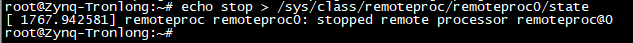

执行如下命令,停止CPU1程序。

Target# echo stop > /sys/class/remoteproc/remoteproc0/state

图 9

2、matrix_multiply案例

2.1 案例功能

案例功能:CPU0随机生成两个矩阵并使用RPMsg向CPU1发送数据,CPU1接收到数据后进行矩阵乘法运算,再使用RPMsg向CPU0回传运算结果,然后CPU0通过串口终端输出运算结果。

2.2 操作说明

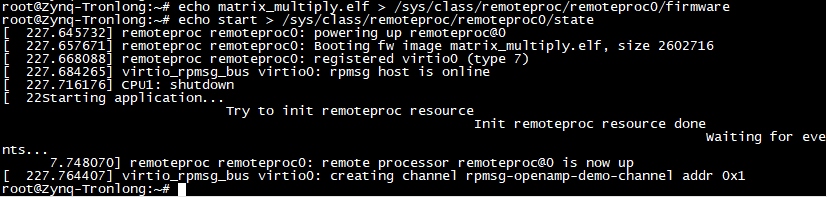

将CPU1裸机或FreeRTOS可执行文件复制到评估板文件系统“/lib/firmware/”目录下,并执行如下命令加载CPU1程序。

Target# echo matrix_multiply.elf > /sys/class/remoteproc/remoteproc0/firmware

Target# echo start > /sys/class/remoteproc/remoteproc0/state

图 10

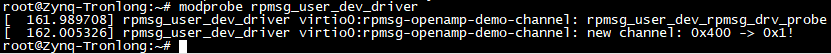

执行如下命令加载RPMsg驱动,并在“/dev/”目录下生成RPMsg设备节点。

Target# modprobe rpmsg_user_dev_driver

图 11

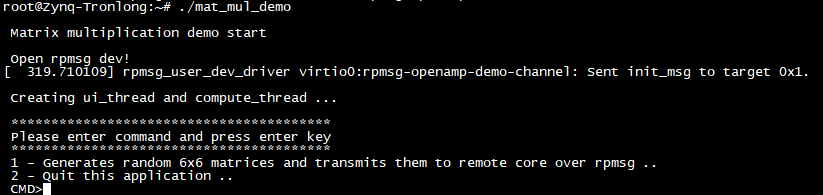

将CPU0应用程序可执行文件复制到评估板文件系统,并执行如下命令通过RPMsg与CPU1进行通信。

Target# ./mat_mul_demo

图 12

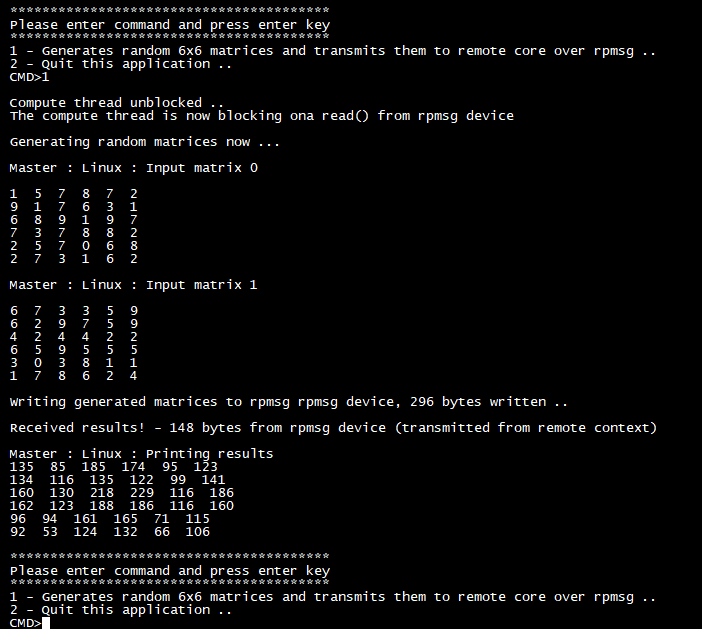

输入1,并按回车键进行测试。

图 13

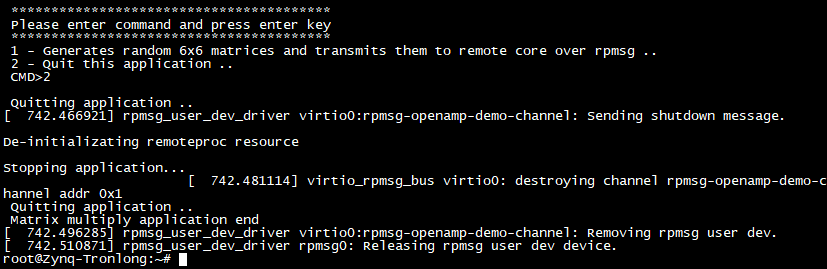

输入2,并按回车键退出测试。

图 14

执行如下命令,停止CPU1程序。

Target# echo stop > /sys/class/remoteproc/remoteproc0/state

图 15

3、内存分配说明

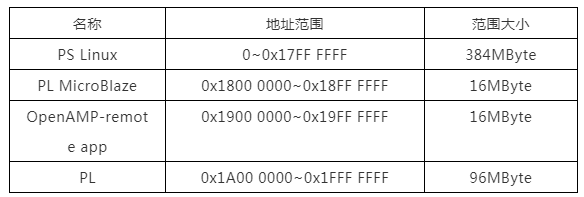

512MByte DDR容量版本核心板的内存地址分配如下:

表 1

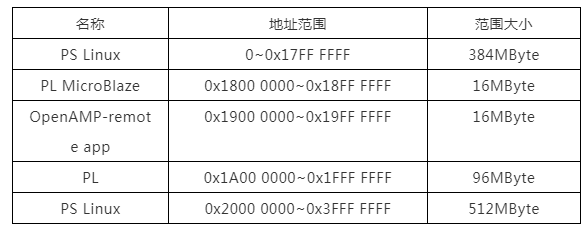

1GByte DDR容量版本核心板的内存地址分配如下:

表 2

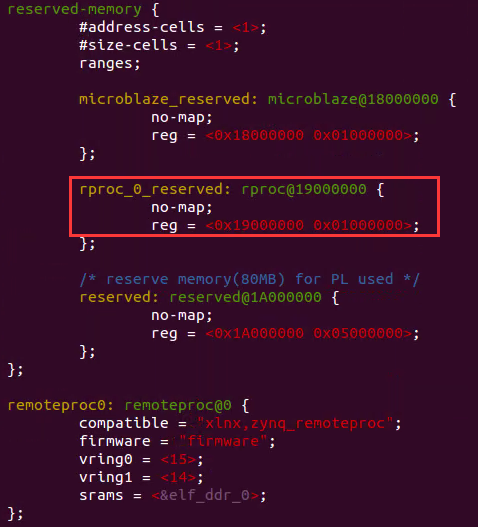

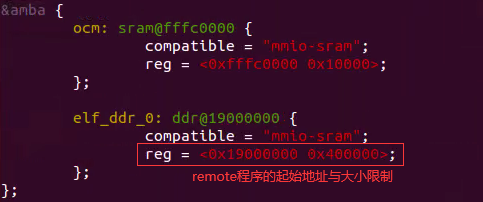

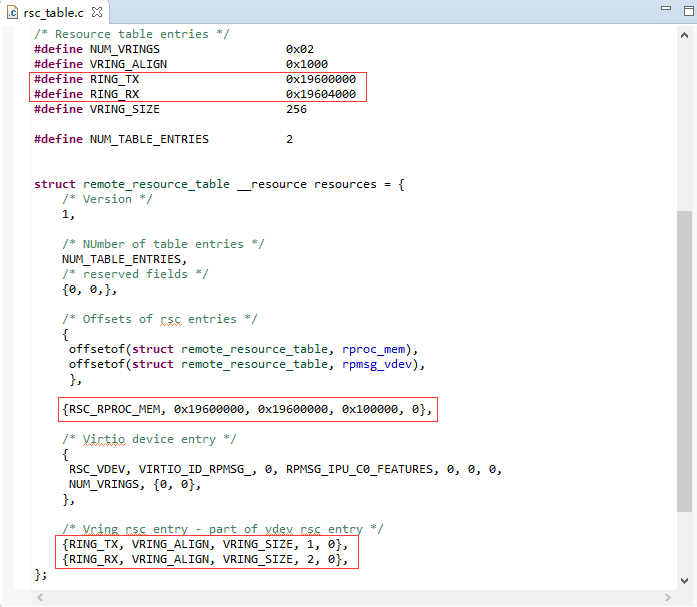

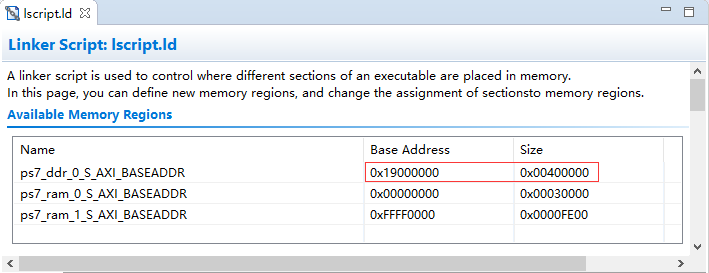

如需修改CPU1程序(OpenAMP-remote app)内存地址空间范围,可通过更改设备树文件tlz7x-easyevm-s.dts、资源表rsc_table.c及链接文件lscript.ld对内存地址空间进行重新分配。三者需同步修改并保持一致,以确保固件程序链接地址与设备树配置的elf_ddr_0对应。所使用的资源(内存和virtio设备资源)不能超出设备树文件配置的内存范围。

图 16设备树文件tlz7x-easyevm-s.dts配置

图 17设备树文件tlz7x-easyevm-s.dts配置

图 18 CPU1程序资源表rsc_table.c配置

图 19 CPU1程序链接文件lscript.ld配置

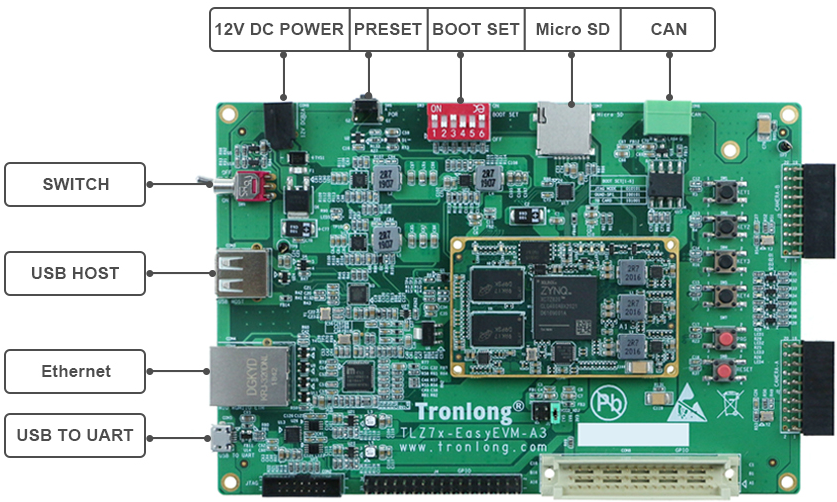

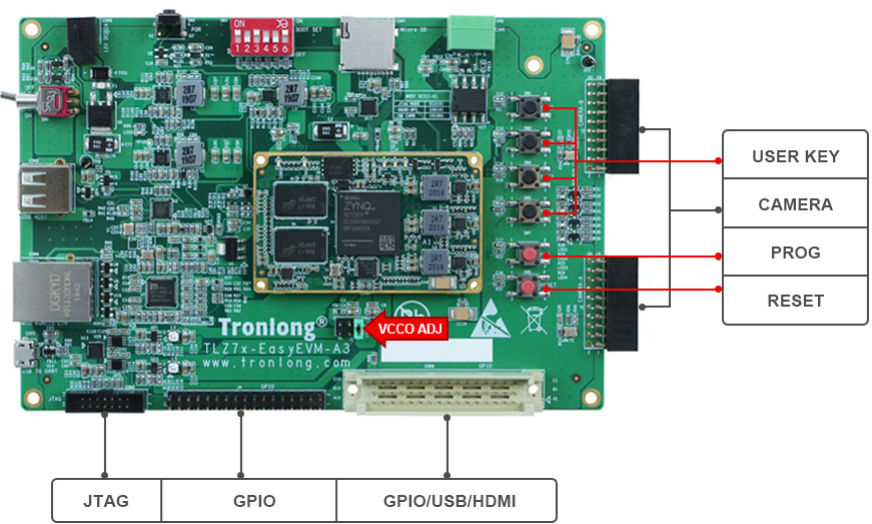

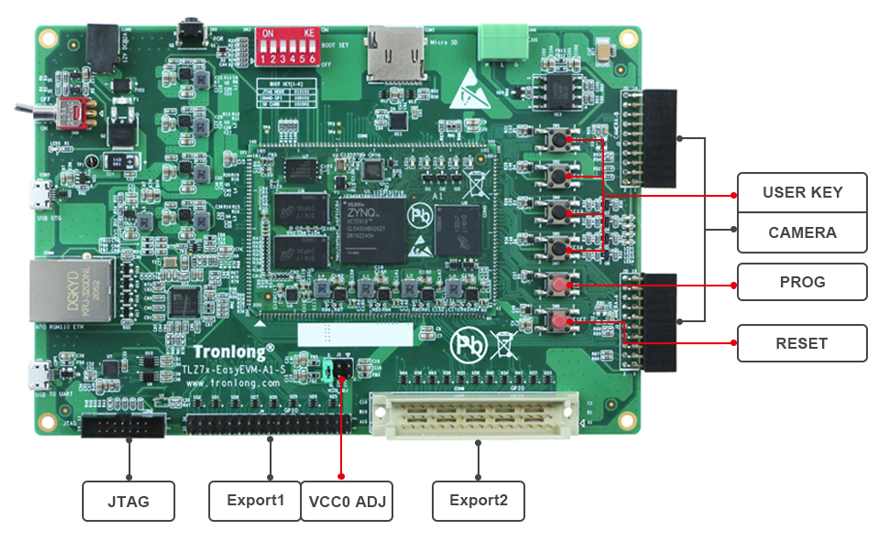

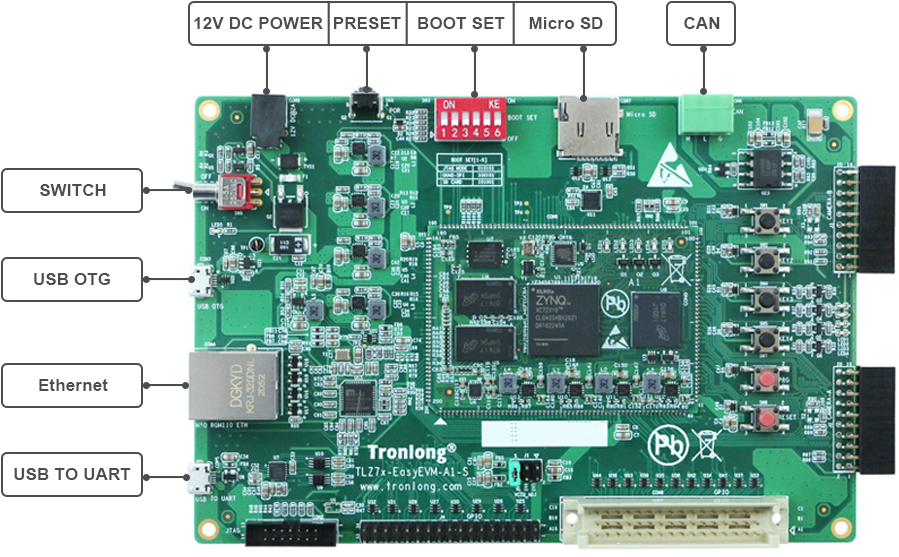

上述推文中的案例是在创龙科技(Tronlong)基于Zynq-7010/7020处理器设计的两款工业评估板——TLZ7x-EasyEVM、TLZ7x-EasyEVM-S上实现的,它由核心板+底板构成,用户使用核心板进行二次开发时,仅需专注上层运用,降低了开发难度和时间成本,可快速进行产品方案评估与技术预研。

图 1 TLZ7x-EasyEVM硬件资源框图

图 2 TLZ7x-EasyEVM硬件资源框图

图 3 TLZ7x-EasyEVM-S硬件资源框图

图 4 TLZ7x-EasyEVM-S硬件资源框图

-

FPGA

+关注

关注

1631文章

21806浏览量

606709 -

ARM

+关注

关注

134文章

9184浏览量

369743 -

嵌入式

+关注

关注

5096文章

19199浏览量

308302 -

Linux

+关注

关注

87文章

11354浏览量

210667

发布评论请先 登录

相关推荐

“国产双系统”出炉!复旦微FMQL20SM非对称AMP:Linux + 裸机

ARM + RISC-V核间通信方案,基于全志T113-i的OpenAMP非对称架构

手机和锂电池纳入第一批工业产品碳足迹核算规则团体标准推荐清单

Littelfuse推出新型TPSMB非对称TVS二极管

Littelfuse推出TPSMB非对称TVS二极管系列

“双系统”出炉!瑞芯微RK3562J非对称AMP:Linux+RTOS/裸机

业界首款用于SiC MOSFET栅极保护的非对称瞬态抑制二极管系列

非对称的ARM双系统,如何实现工业产品的低延时——基于ZYNQ

非对称的ARM双系统,如何实现工业产品的低延时——基于ZYNQ

评论