稳定性对于灵敏度高的测量系统至关重要, 它是决定系统准确度和精密性的关键参数。就像电压表中的参考电压一样,激光的频率和相位必须参考一个稳定的源。在这篇技术文章中,我们介绍了光学系统中的偏移锁相法的应用,此方法可以将一个光学系统的稳定性转移到另一个光学系统,使得此系统达到同样稳定的效果。这是我们上海昊量光电设备有限公司推出的Moku:Lab的产品实现了此功能。

一、简介

光学锁相是一种常见的技术,他能够将一束激光的频率和相位特性传递给另一束激光。它通常用于外差计量、自由空间光通信和光谱应用。在这篇技术文章中,我们讨论了使用数字相位表实现偏移相位锁定,并描述了锁相后双激光器的稳定性。

光学偏移锁相(简而言之)简单地说,偏移锁相稳定了两个激光器之间的相位差,实现过程如下:首先测量两台激光器的相位差;第二,通过反馈并调节其中一台激光器的频率来稳定相位差。

测量两个激光器之间的相位差是一个相对简单的过程,结合两个激光器的输出(通过一个分束器或类似的装置),并将组合的光束照射到一个光电探测器上。其结果类似于混频过程,并在两个激光器的差频处产生一个振荡信号。我们可以把这个称为混频后的信号。

光电二极管的功率用下面公式描述:

PPD和EPD分别表示探测器上的能量和电场。E1和E2是每个激光器的输出场强,计算公式如下:

其中 ω1和ω2是各自的频率,Φ1和Φ2是各自的相位,将公式2 和3带入到公式1中,可以得到下面公式:

注意,高阶项通常在光电探测器的带宽之外,重要的是要认识到,即使混频后的信号包含了激光器的相位信息,这个信息包含在信号的参数中,并且在这种形式的反馈系统中使用相对困难。为了从混频后的信号中提取相位,我们使用了相位检测器。一个简单的鉴相器由一个混频器和一个低通滤波器组成,该滤波器将信息转换为基带,以便用于反馈系统。

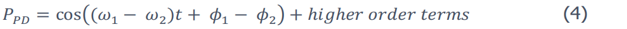

一旦把基带中的相位信号反馈到其中一个激光器, 可以消除两个激光器之间的任何差异。图1总结了完整的设置。

图1:典型偏移激光锁频系统示意图

二、锁相环(PLL) -----一种不同类型的鉴相器

虽然混频器和低通滤波器对于大多数偏置锁相系统是足够的,但也有其局限性。首先,混频器-滤波器组合的范围限制在±π/2,并且系统的相位输出只有在非常接近于零时才会是线性的。这些范围和线性问题往往使系统难以处理大的波动。在这些情况下,使用额外的锁相环(PLL)代替标准的混频器-滤波器进行相位检测可能会有所帮助。

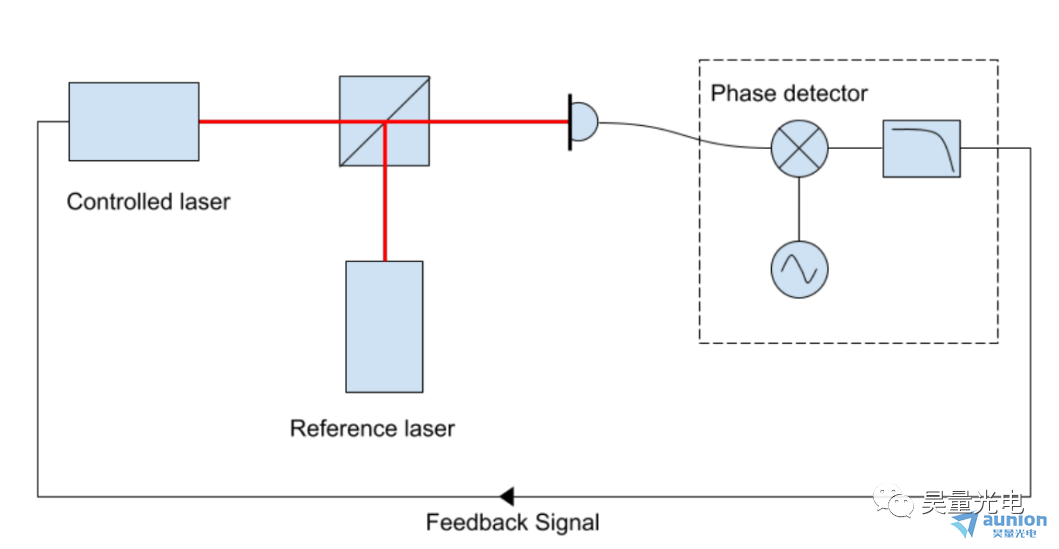

锁相环是一种用来在两个振荡器之间建立稳定的频率和相位关系的技术。它被广泛应用于现代电子、集成芯片等许多领域。锁相环有三个主要组成部分:鉴相器,环路滤波器和可控/可调振荡器。该鉴相器产生包含与两个信号之间的相位差(近似)成比例的直流分量的信号。然后将该信号发送到环路滤波器(低通和/或PID),从鉴相器中去除高次谐波。滤波后的误差信号被送到振荡器,振荡器的输出频率由输入的直流电压控制。通过形成这个闭环并调谐环路滤波器,可以实现两个振荡器的稳定相位关系。

图2:典型的锁相环框图

锁相环在初始锁的获取,去除非线性影响(如周期滑动),和确保更稳定的锁方面是有帮助的。

三、用Moku:Pro进行偏移锁相

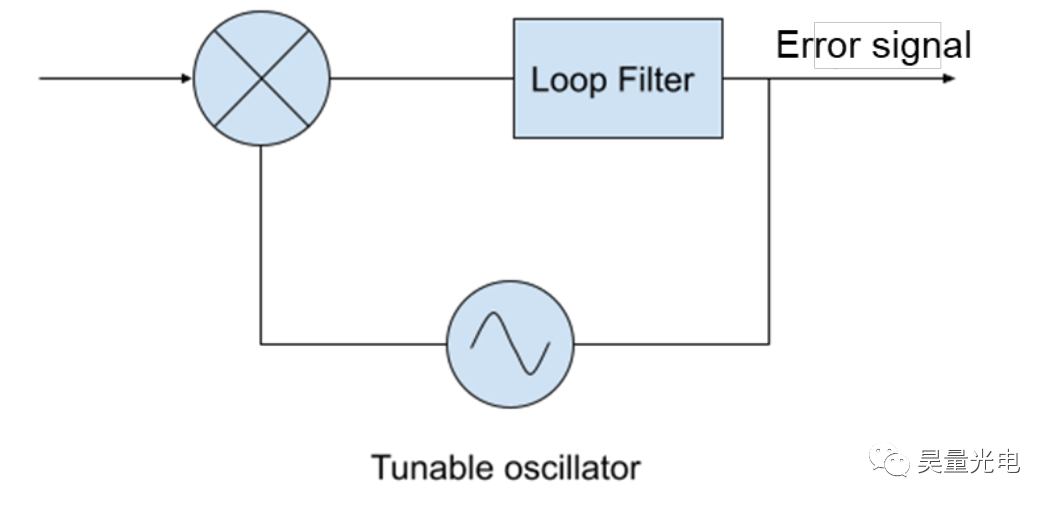

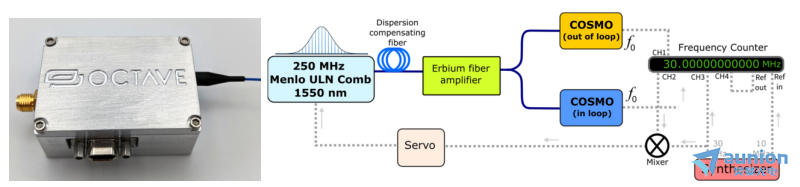

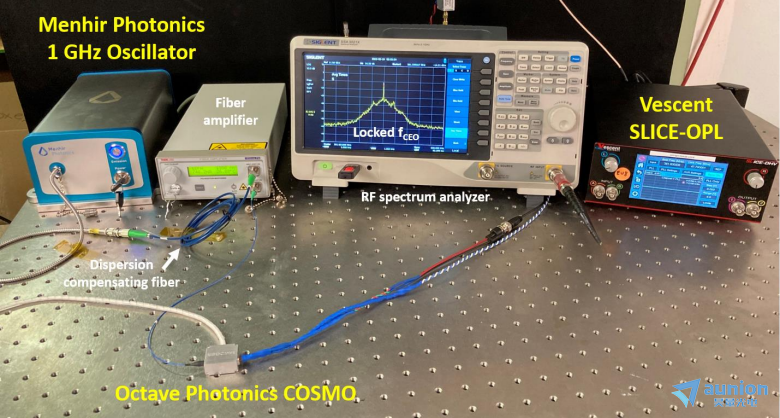

为了演示了Moku:Pro的相位表偏移锁相结构,我们使用了两个非平面环形振荡(NPRO)激光器,主激光器和从激光器的光束在分束器处合并,并在光电二极管上进行干涉,如图3所示。混频后的信号与Moku:Pro的输入1相连。然后将反馈信号连接到下一激光器的频率控制器上。

图3:激光偏移锁频的仪器设置

3.1 设置锁相功能参数

在实现锁相之前,需要将系统参数调整到工作范围。为了能够锁定信号,热驱动器被用来粗略地调整激光,以在Moku:Pro输入的600 MHz带宽内产生混频信号。一旦进入量程,相位表可以通过使用自动获取功能或手动设置频率来跟踪混频信号。有关相位表的详细信息,请参阅参考资料[5]和相位表用户手册。

设置输出使用相位和选择电压缩放(这可以被视为增益在一个典型的控制回路)。你可以从一个小的增益开始,逐渐增加增益来优化系统。

图4:控制回路的初始增益可以通过“缩放”在“输出”窗口中设置

手动操作时,可以使用初始频率来调整偏移锁相器的频率,以达到到所需的频率。

图5:偏移频率可以通过“Channel”窗口下的“Frequenc”进行调整

3.2 自锁性能

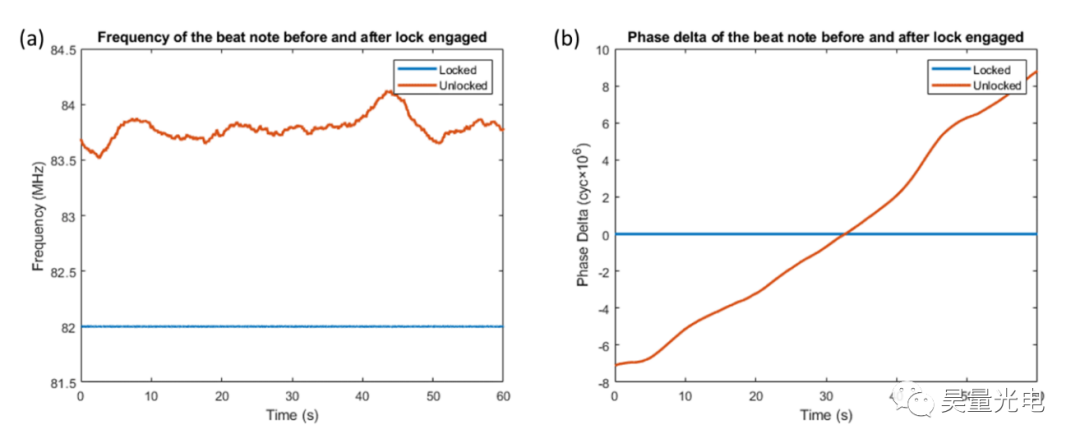

使用Moku:Lab上运行的独立相位表测量锁相的性能。图6显示了在测量60秒时的锁定和自由运行频率(a)和相位(b)。可以清楚地看到,两个激光器之间的相位和频率波动都明显减小。

图6:混频信号在被锁与不被锁的情况下的频率a和相位b图示

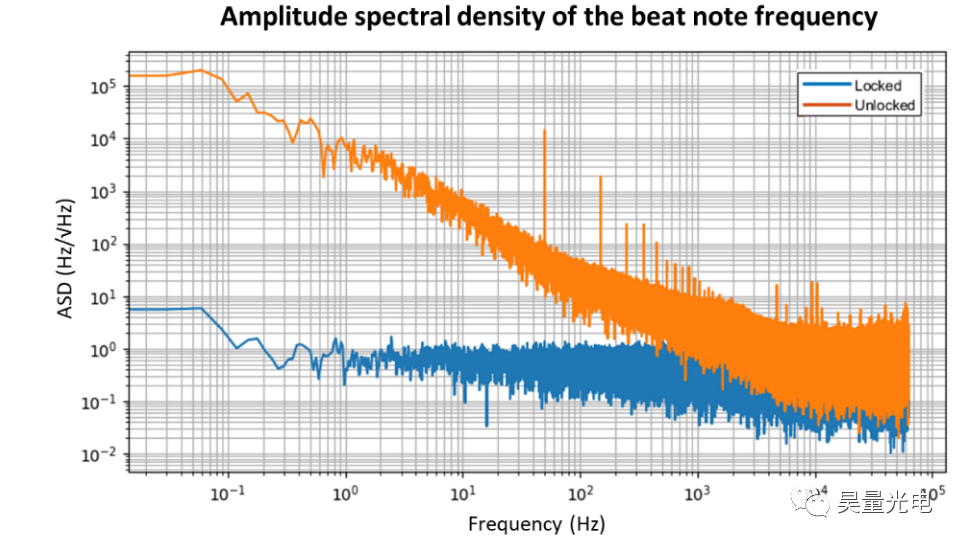

以频率的幅值谱密度为例,测得稳定性提高了4个数量级以上,从1 Hz/√Hz的相对频率稳定性降低到0.1 Hz。

图7:锁相前后偏移混频信号的振幅谱密度图

四、总结

激光偏移锁定保持了主激光器和从激光器之间的频率差。在这样的系统中,相位误差信号的动态范围通常超过2π,此时混频器型的相位检测器可能无法连续跟踪信号。Moku:Pro的相位表实现了四个独立的锁相环相位检测器,并且有自动相位展开功能。在两个激光器之间,以82 MHz的偏移量实现了稳定锁频,在10 Hz时的频率稳定性优于1 Hz/ √Hz。

-

FPGA

+关注

关注

1635文章

21837浏览量

608326 -

激光器

+关注

关注

17文章

2582浏览量

60998

发布评论请先 登录

相关推荐

锁相环是什么意思

锁相环PLL的噪声分析与优化 锁相环PLL与相位噪声的关系

锁相环PLL的常见故障及解决方案

锁相环PLL的工作原理 锁相环PLL应用领域

数字锁相环固有的相位抖动是怎样产生的,如何解决

锁相环频率合成器的特点和应用

锁相环相位噪声的影响因素

锁相环的工作原理和应用场景

激光器偏频锁定,一种基于FPGA应用于光学锁相环的四通道相位表

激光器偏频锁定,一种基于FPGA应用于光学锁相环的四通道相位表

评论