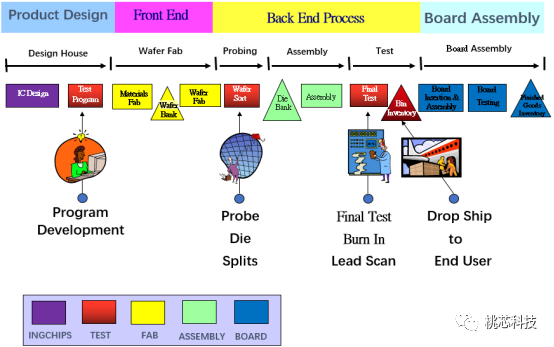

给大家说说芯片测试相关。1测试在芯片产业价值链上的位置如下面这个图表,一颗芯片最终做到终端产品上,一般需要经过芯片设计、晶圆制造、晶圆测试、封装、成品测试、板级封装等这些环节。在整个价值链中,芯片公司需要主导的环节主要是芯片设计和测试,其余的环节都可以由相应的partner来主导或者完成。  图(1)2测试如何体现在设计的过程中 下图表示的是设计公司在进行一个新的项目的时候的一般流程,从市场需求出发,到产品tape out进行制造,包含了系统设计、逻辑设计、电路设计、物理设计,到最后开始投入制造。最下面一栏标注了各个设计环节中对于测试的相关考虑,从测试架构、测试逻辑设计、测试模式产生、到各种噪声/延迟/失效模式综合、进而产生测试pattern,最后在制造完成后进行测试,对测试数据进行分析,从而分析失效模式,验证研发。所以,测试本身就是设计,这个是需要在最初就设计好了的,对于设计公司来说,测试至关重要,不亚于电路设计本身。

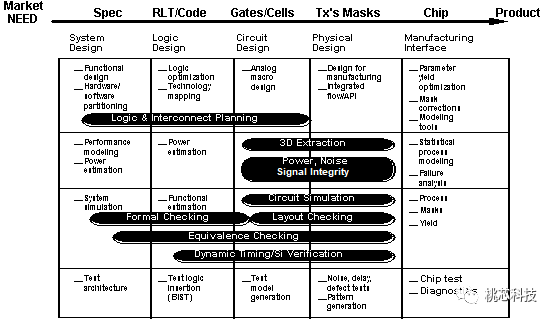

图(1)2测试如何体现在设计的过程中 下图表示的是设计公司在进行一个新的项目的时候的一般流程,从市场需求出发,到产品tape out进行制造,包含了系统设计、逻辑设计、电路设计、物理设计,到最后开始投入制造。最下面一栏标注了各个设计环节中对于测试的相关考虑,从测试架构、测试逻辑设计、测试模式产生、到各种噪声/延迟/失效模式综合、进而产生测试pattern,最后在制造完成后进行测试,对测试数据进行分析,从而分析失效模式,验证研发。所以,测试本身就是设计,这个是需要在最初就设计好了的,对于设计公司来说,测试至关重要,不亚于电路设计本身。  图(2)设计公司主要目标是根据市场需求来进行芯片研发,在整个设计过程中,需要一直考虑测试相关的问题,主要有下面几个原因:1)随着芯片的复杂度越来越高,芯片内部的模块越来越多,制造工艺也是越来越先进,对应的失效模式越来越多,而如何能完整有效地测试整个芯片,在设计过程中需要被考虑的比重越来越多。2)设计、制造、甚至测试本身,都会带来一定的失效,如何保证设计处理的芯片达到设计目标,如何保证制造出来的芯片达到要求的良率,如何确保测试本身的质量和有效,从而提供给客户符合产品规范的、质量合格的产品,这些都要求必须在设计开始的第一时间就要考虑测试方案。3)成本的考量。越早发现失效,越能减少无谓的浪费;设计和制造的冗余度越高,越能提供最终产品的良率;同时,如果能得到更多的有意义的测试数据,也能反过来提供给设计和制造端有用的信息,从而使得后者有效地分析失效模式,改善设计和制造良率。 3测试的各种

图(2)设计公司主要目标是根据市场需求来进行芯片研发,在整个设计过程中,需要一直考虑测试相关的问题,主要有下面几个原因:1)随着芯片的复杂度越来越高,芯片内部的模块越来越多,制造工艺也是越来越先进,对应的失效模式越来越多,而如何能完整有效地测试整个芯片,在设计过程中需要被考虑的比重越来越多。2)设计、制造、甚至测试本身,都会带来一定的失效,如何保证设计处理的芯片达到设计目标,如何保证制造出来的芯片达到要求的良率,如何确保测试本身的质量和有效,从而提供给客户符合产品规范的、质量合格的产品,这些都要求必须在设计开始的第一时间就要考虑测试方案。3)成本的考量。越早发现失效,越能减少无谓的浪费;设计和制造的冗余度越高,越能提供最终产品的良率;同时,如果能得到更多的有意义的测试数据,也能反过来提供给设计和制造端有用的信息,从而使得后者有效地分析失效模式,改善设计和制造良率。 3测试的各种

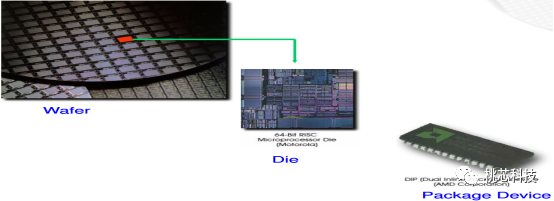

对于芯片来说,有两种类型的测试,抽样测试和生产全测。抽样测试,比如设计过程中的验证测试,芯片可靠性测试,芯片特性测试等等,这些都是抽测,主要目的是为了验证芯片是否符合设计目标,比如验证测试就是从功能方面来验证是否符合设计目标,可靠性测试是确认最终芯片的寿命以及是否对环境有一定的鲁棒性,而特性测试测试验证设计的冗余度。这里我们主要想跟大家分享一下生产全测的测试,这种是需要100%全测的,这种测试就是把缺陷挑出来,分离坏品和好品的过程。这种测试在芯片的价值链中按照不同阶段又分成晶圆测试和最终测试(FT,也叫封装测试或者成品测试),就是上面图(1)中的红色部分。 测试相关的各种名词:ATE-----------Automatic Test Equipment,自动化测试设备,是一个高性能计算机控制的设备的集合,可以实现自动化的测试。Tester---------测试机,是由电子系统组成,这些系统产生信号,建立适当的测试模式,正确地按顺序设置,然后使用它们来驱动芯片本身,并抓取芯片的输出反馈,或者进行记录,或者和测试机中预期的反馈进行比较,从而判断好品和坏品。Test Program---测试程序,测试机通过执行一组称为测试程序的指令来控制测试硬件DUT-----------Device Under Test,等待测试的器件,我们统称已经放在测试系统中,等待测试的器件为DUT。 晶圆、单颗die和封装的芯片----如下面图(3)所示  图(3)Wafer就是晶圆,这个由Fab进行生产,上面规则地放着芯片(die),根据die的具体面积,一张晶圆上可以放数百数千甚至数万颗芯片(die)。Package Device就是封装好的芯片,根据最终应用的需求,有很多种形式,这个部分由芯片产业价值链中的封装工厂进行完成。 测试系统的基本工作机制:

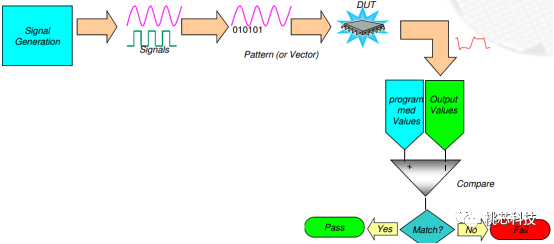

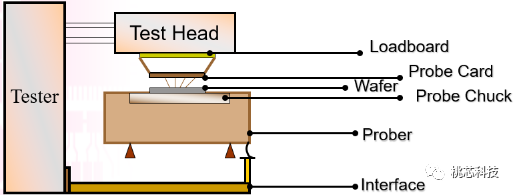

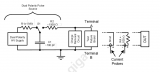

图(3)Wafer就是晶圆,这个由Fab进行生产,上面规则地放着芯片(die),根据die的具体面积,一张晶圆上可以放数百数千甚至数万颗芯片(die)。Package Device就是封装好的芯片,根据最终应用的需求,有很多种形式,这个部分由芯片产业价值链中的封装工厂进行完成。 测试系统的基本工作机制: 图(4) 对测试机进行编写程序,从而使得测试机产生任何类型的信号,多个信号一起组成测试模式或测试向量,在时间轴的某一点上向DUT施加一个测试向量,将DUT产生的输出反馈输入测试机的仪器中测量其参数,把测量结果与存储在测试机中的“编程值”进行比较,如果测量结果在可接受公差范围内匹配测试机中的“编程值”,那么这颗DUT就会被认为是好品,反之则是坏品,按照其失效的种类进行记录。 晶圆测试(wafer test,或者CP-chip probering):就是在图(3)中的晶圆上直接进行测试,下面图中就是一个完整的晶圆测试自动化系统。Prober--- 与Tester分离的一种机械设备,主要的作用是承载wafer,并且让wafer内的一颗die的每个bond pads都能连接到probe card的探针上,并且在测试后,移开之前的接触,同时移动wafer,换另外的die再一次连接到probe card的探针上,并记录每颗die的测试结果。

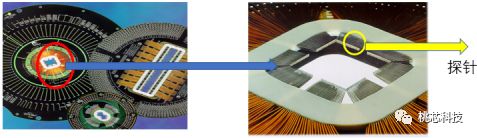

图(4) 对测试机进行编写程序,从而使得测试机产生任何类型的信号,多个信号一起组成测试模式或测试向量,在时间轴的某一点上向DUT施加一个测试向量,将DUT产生的输出反馈输入测试机的仪器中测量其参数,把测量结果与存储在测试机中的“编程值”进行比较,如果测量结果在可接受公差范围内匹配测试机中的“编程值”,那么这颗DUT就会被认为是好品,反之则是坏品,按照其失效的种类进行记录。 晶圆测试(wafer test,或者CP-chip probering):就是在图(3)中的晶圆上直接进行测试,下面图中就是一个完整的晶圆测试自动化系统。Prober--- 与Tester分离的一种机械设备,主要的作用是承载wafer,并且让wafer内的一颗die的每个bond pads都能连接到probe card的探针上,并且在测试后,移开之前的接触,同时移动wafer,换另外的die再一次连接到probe card的探针上,并记录每颗die的测试结果。  图(4)Probe Card---乃是Tester与wafer上的DUT之间其中一个连接介面,目的在连接Tester Channel 与待测DUT。大部分为钨铜或铍铜,也有钯等其他材质;材质的选择需要高强度、导电性及不易氧化等特性,样子如下面图(5)所示。

图(4)Probe Card---乃是Tester与wafer上的DUT之间其中一个连接介面,目的在连接Tester Channel 与待测DUT。大部分为钨铜或铍铜,也有钯等其他材质;材质的选择需要高强度、导电性及不易氧化等特性,样子如下面图(5)所示。  图(5) 当 probe card 的探针正确接触wafer内一顆 die的每个bond pads后, 送出start信号通过Interface给tester开始测试, tester完成测试送回分类讯号 ( End of test) 给Prober, 量产時必須 tester 与 prober 做连接(docking) 才能测试。 最终测试(FT,或者封装测试):就是在图(3)中的Package Device上进行测试.下图就是一个完整的FT的测试系统。对比wafer test,其中硬件部分,prober换成了handler,其作用是一样的,handler的主要作用是机械手臂,抓取DUT,放在测试区域,由tester对其进行测试,然后handler再根据tester的测试结果,抓取DUT放到相应的区域,比如好品区,比如坏品1类区,坏品2类区等。

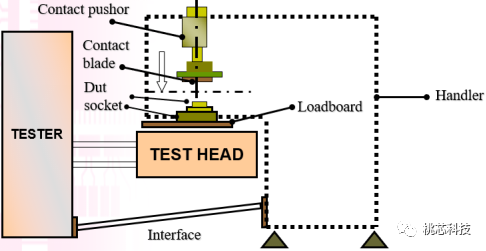

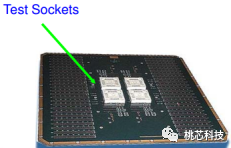

图(5) 当 probe card 的探针正确接触wafer内一顆 die的每个bond pads后, 送出start信号通过Interface给tester开始测试, tester完成测试送回分类讯号 ( End of test) 给Prober, 量产時必須 tester 与 prober 做连接(docking) 才能测试。 最终测试(FT,或者封装测试):就是在图(3)中的Package Device上进行测试.下图就是一个完整的FT的测试系统。对比wafer test,其中硬件部分,prober换成了handler,其作用是一样的,handler的主要作用是机械手臂,抓取DUT,放在测试区域,由tester对其进行测试,然后handler再根据tester的测试结果,抓取DUT放到相应的区域,比如好品区,比如坏品1类区,坏品2类区等。  图(6) 而probe card则换成了load board,其作用是类似的,但是需要注意的是load board上需要加上一个器件—Socket,这个是放置package device用的,每个不同的package种类都需要不同的socket,如下面图(7)所示,load board上的四个白色的器件就是socket。

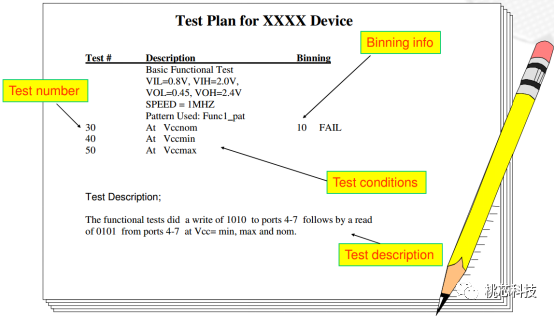

图(6) 而probe card则换成了load board,其作用是类似的,但是需要注意的是load board上需要加上一个器件—Socket,这个是放置package device用的,每个不同的package种类都需要不同的socket,如下面图(7)所示,load board上的四个白色的器件就是socket。 图(7)Handler 必须与 tester 相结合(此动作叫 mount 机)及接上interface才能测试, 动作为handler的手臂将DUT放入socket,然后 contact pusher下压, 使 DUT的脚正确与 socket 接触后, 送出start 讯号, 透过 interface 给 tester, 测试完后, tester 送回 binning 及EOT 讯号; handler做分类动作。4如何进行一个产品的测试开发各种规格书:通常有三种规格书,设计规格书、测试规格书、产品规格书。设计规格书,是一种包含新电路设计的预期功能和性能特性的定义的文档,这个需要在设计项目启动阶段就要完成,通常由市场和设计人员共同完成,最终设计出来的产品的实际功能和性能需要和设计规格书的规定进行比较,以确认本次设计项目的完成度。测试规格书,其中包含详细的逐步测试程序、条件、方法,以充分测试电路,通常由设计人员和产品验证工程师在设计过程中完成。产品规格书,通常就是叫做datasheet,由设计公司对外发布的,包含了各种详细的规格、电压、电流、时序等信息。 测试计划书:就是test plan,需要仔细研究产品规格书,根据产品规格书来书写测试计划书,具体的需要包含下面这些信息:a)DUT的信息,具体的每个pad或者pin的信息,CP测试需要明确每个bond pads的坐标及类型信息,FT测试需要明确封装类型及每个pin的类型信息。b)测试机要求,测试机的资源需求,比如电源数量需求、程序的编写环境、各种信号资源数量、精度如何这些,还需要了解对应的测试工厂中这种测试机的数量及产能,测试机费用这些。c)各种硬件信息,比如CP中的probe card, FT中的load board的设计要求,跟测试机的各种信号资源的接口。d)芯片参数测试规范,具体的测试参数,每个测试项的测试条件及参数规格,这个主要根据datasheet中的规范来确认。类型与下面图(8)这样

图(7)Handler 必须与 tester 相结合(此动作叫 mount 机)及接上interface才能测试, 动作为handler的手臂将DUT放入socket,然后 contact pusher下压, 使 DUT的脚正确与 socket 接触后, 送出start 讯号, 透过 interface 给 tester, 测试完后, tester 送回 binning 及EOT 讯号; handler做分类动作。4如何进行一个产品的测试开发各种规格书:通常有三种规格书,设计规格书、测试规格书、产品规格书。设计规格书,是一种包含新电路设计的预期功能和性能特性的定义的文档,这个需要在设计项目启动阶段就要完成,通常由市场和设计人员共同完成,最终设计出来的产品的实际功能和性能需要和设计规格书的规定进行比较,以确认本次设计项目的完成度。测试规格书,其中包含详细的逐步测试程序、条件、方法,以充分测试电路,通常由设计人员和产品验证工程师在设计过程中完成。产品规格书,通常就是叫做datasheet,由设计公司对外发布的,包含了各种详细的规格、电压、电流、时序等信息。 测试计划书:就是test plan,需要仔细研究产品规格书,根据产品规格书来书写测试计划书,具体的需要包含下面这些信息:a)DUT的信息,具体的每个pad或者pin的信息,CP测试需要明确每个bond pads的坐标及类型信息,FT测试需要明确封装类型及每个pin的类型信息。b)测试机要求,测试机的资源需求,比如电源数量需求、程序的编写环境、各种信号资源数量、精度如何这些,还需要了解对应的测试工厂中这种测试机的数量及产能,测试机费用这些。c)各种硬件信息,比如CP中的probe card, FT中的load board的设计要求,跟测试机的各种信号资源的接口。d)芯片参数测试规范,具体的测试参数,每个测试项的测试条件及参数规格,这个主要根据datasheet中的规范来确认。类型与下面图(8)这样  图(8) e)测试项目开发计划,规定了具体的细节以及预期完成日期,做到整个项目的可控制性和效率。 测试项目流程:桃芯科技目前量产的是BLE的SOC产品,里面包含了eflash、AD/DA、 LDO/BUCK、RF等很多模块,为了提供给客户高品质的产品,我们针对每个模块都有详细的测试,下面图(9)是我们的大概的项目测试流程:

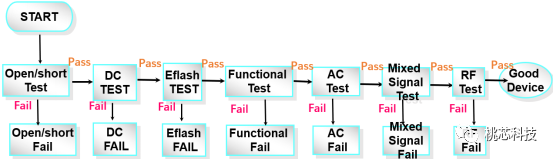

图(8) e)测试项目开发计划,规定了具体的细节以及预期完成日期,做到整个项目的可控制性和效率。 测试项目流程:桃芯科技目前量产的是BLE的SOC产品,里面包含了eflash、AD/DA、 LDO/BUCK、RF等很多模块,为了提供给客户高品质的产品,我们针对每个模块都有详细的测试,下面图(9)是我们的大概的项目测试流程:  图(9)

图(9)

Open/Short Test: 检查芯片引脚中是否有开路或短路。

DC TEST:验证器件直流电流和电压参数

Eflash TEST: 测试内嵌flash的功能及性能,包含读写擦除动作及功耗和速度等各种参数。

Function TEST: 测试芯片的逻辑功能。

AC Test: 验证交流规格,包括交流输出信号的质量和信号时序参数。

Mixed Signal Test:验证DUT数模混合电路的功能及性能参数。

RF Test: 测试芯片里面RF模块的功能及性能参数。

上面我们给大家介绍了芯片的测试目的,原理,以及方法和流程,接下来我们将比较详细的给大家介绍芯片的错误类型,对应的测试策略,以及跟芯片整体质量相关的一些具体测试方法。

1

半导体芯片的defects、Faults

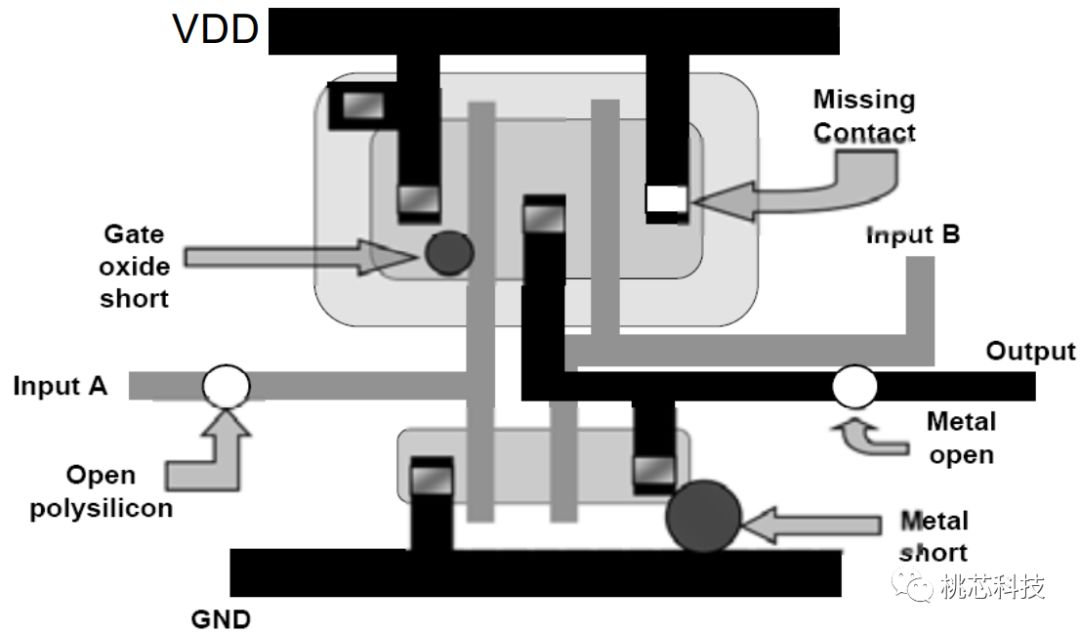

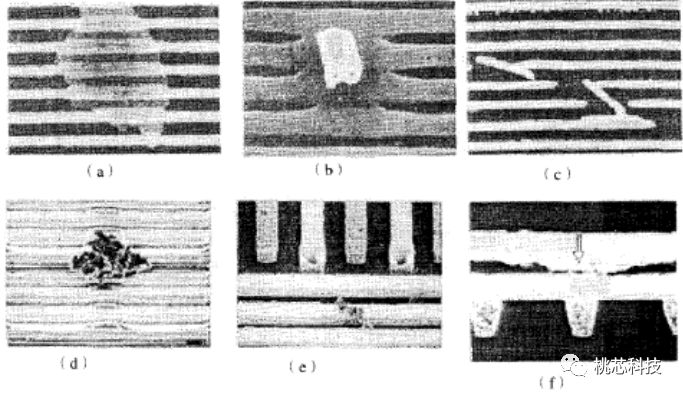

芯片在制造过程中,会出现很多种不同类型的defects,比如栅氧层针孔、扩散工艺造成的各种桥接、各种预期外的高阻态、寄生电容电阻造成的延迟等等,如下面图(1)所示,大概展示了各种基本的defects。 图(1)这些defects单独、或者组合一起,造成了电路的表现不符预期,这就是造成了Faults.而且各种Faults的表现也是不一样的:永久的Faults,就是彻底的坏品,各种不同的条件下都会表现出来,易于测试发现。间或的Faults,时有发生的不符合预期,不是总能发现,需要一定的外部条件刺激。偶然的Faults,只是偶然的,在特定的外部硬件或者工作模式条件下才表现出来。可靠性问题的Faults,这种一般不会表现出来,只会在一些极端条件才会表现出来,比如高低温或者偏压情况下。为了更有效地检测出各种faults、避免浪费更多芯片的资源、节省费用,业界定义了很多种Faults Model,并提供了各种测试方法论。

图(1)这些defects单独、或者组合一起,造成了电路的表现不符预期,这就是造成了Faults.而且各种Faults的表现也是不一样的:永久的Faults,就是彻底的坏品,各种不同的条件下都会表现出来,易于测试发现。间或的Faults,时有发生的不符合预期,不是总能发现,需要一定的外部条件刺激。偶然的Faults,只是偶然的,在特定的外部硬件或者工作模式条件下才表现出来。可靠性问题的Faults,这种一般不会表现出来,只会在一些极端条件才会表现出来,比如高低温或者偏压情况下。为了更有效地检测出各种faults、避免浪费更多芯片的资源、节省费用,业界定义了很多种Faults Model,并提供了各种测试方法论。

Stuck At Faults

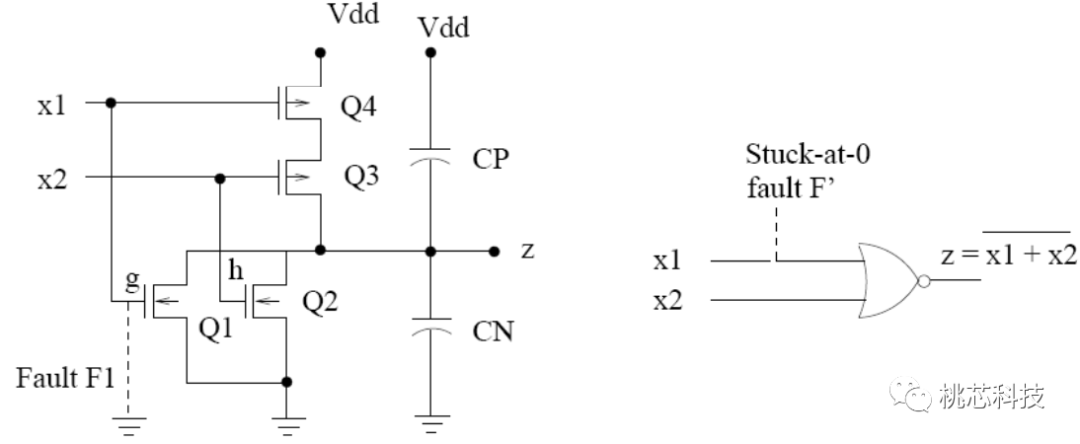

工艺制造过程中造成的硬件defects,使得某个节点Stuck At 0或者Stuck At 1, 如下面图(2)所示的一个或非门:输入节点x1发生了Stuck At 0的defect; x1和x2输入了00时候,Q1和Q2断开,Q3和Q4导通, z输出为H,正确;x1和x2输入了01时候,Q1和Q3断开,Q2和Q4导通, z输出为L,正确;x1和x2输入了10时候,此时x1被Stuck At 0了,等同于输入00,结果还是Q1和Q2断开,Q3和Q4导通,z输出为H,错误;至此,通过输入00,01,10就发现了这个defect。这种顺序输入00,01,10,而比较z输出的结果与预期的值进行判断的方法,就是所谓的Function测试。 图(2)那对于一个电路,需要生成多少pattern,能达到多少的测试覆盖率呢?下面图(3)就以一个与门为例,说一下生产测试向量及计算测试覆盖率的基本理念。

图(2)那对于一个电路,需要生成多少pattern,能达到多少的测试覆盖率呢?下面图(3)就以一个与门为例,说一下生产测试向量及计算测试覆盖率的基本理念。 图(3)如上面图示,一个与门,有三个节点a、b、c, 每个节点都有两种fault的情况(Stuck At 0或者1),那么一共就有6种stuck-at faults情况:a0,a1,b0,b1,c0,c1.那么如上面图中列出的,需要输入(1,0),(0,1),(1,1)可以完全测试出所有的6种可能的Stuck-at Faults的情况,测试覆盖率为:可以发现的faults/所有可能的Faults,上面的输入的测试覆盖率为100%。

图(3)如上面图示,一个与门,有三个节点a、b、c, 每个节点都有两种fault的情况(Stuck At 0或者1),那么一共就有6种stuck-at faults情况:a0,a1,b0,b1,c0,c1.那么如上面图中列出的,需要输入(1,0),(0,1),(1,1)可以完全测试出所有的6种可能的Stuck-at Faults的情况,测试覆盖率为:可以发现的faults/所有可能的Faults,上面的输入的测试覆盖率为100%。

Stuck Open(off)/Short(on) Faults

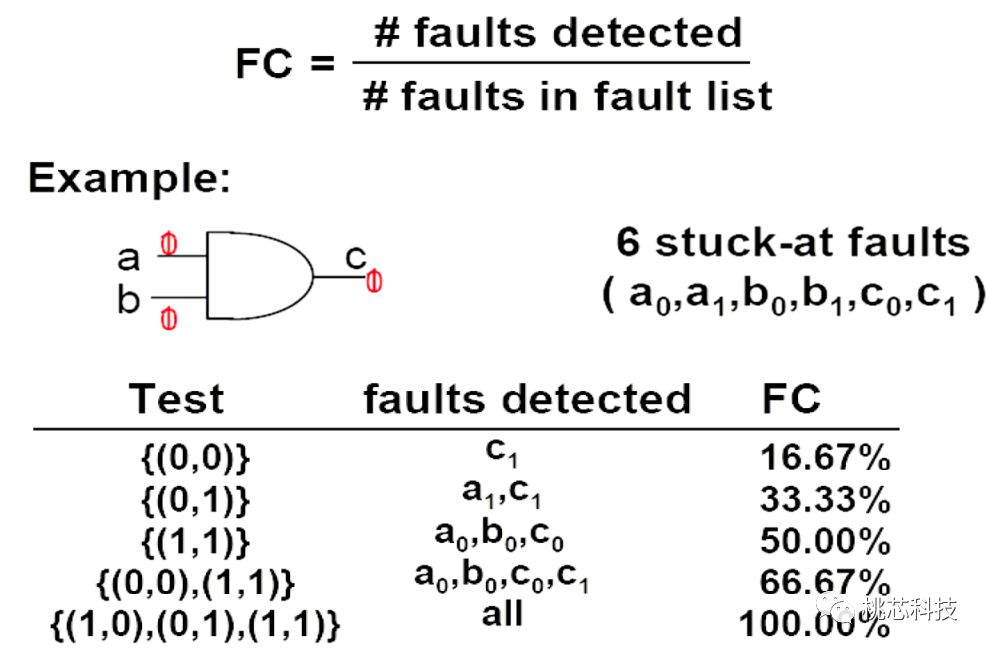

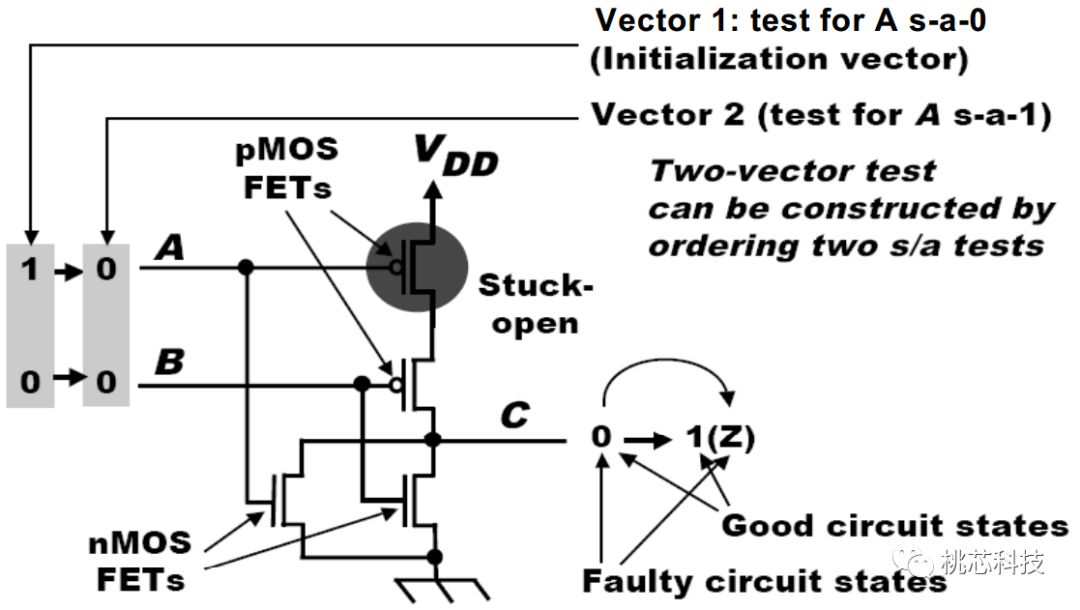

制造过程中造成的晶体管的defects,使得某个晶体管常开或者常闭了,如下面图(4)所示的时一个晶体管发生了Stuck Open(off)的错误了。 图(4)如上图,这种Stuck open可以用两组Stuck At的向量进行测试,AB输入从10变换到00,可以检测出这种Stuck Open的fault,也就是说大部分的Stuck Open/Short的faults都是可以通过Stuck At model的测试向量覆盖的。这种通过向量(function)的方式来测试Stuck Open/short,可能需要非常多的测试图形,需要的测试时间和成本都很多。还有一种测量电流的方式,也可以有效地测试一些这种Stuck open/short的faults,但是会节省很多测试时间和测试成本。如下面图(5)上半部分所示,右边的那个P沟道MOS管发生了Stuck short(on)的faults,图的下半部分展示了输入AB的四种不同的情况,当AB输入为00时,看起来这个晶体管表现地正常;但是当AB输入为11时,地和电源间存在一个直接导通的电路,输出端Z的状态是异常的。

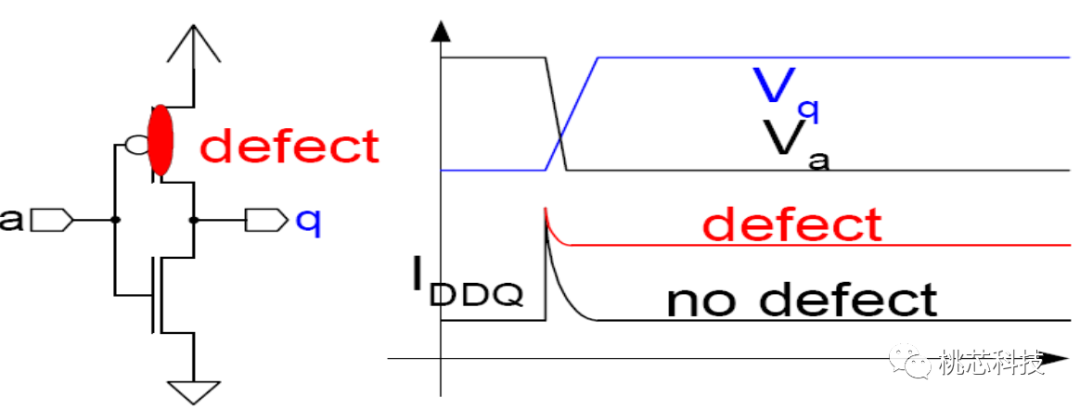

图(4)如上图,这种Stuck open可以用两组Stuck At的向量进行测试,AB输入从10变换到00,可以检测出这种Stuck Open的fault,也就是说大部分的Stuck Open/Short的faults都是可以通过Stuck At model的测试向量覆盖的。这种通过向量(function)的方式来测试Stuck Open/short,可能需要非常多的测试图形,需要的测试时间和成本都很多。还有一种测量电流的方式,也可以有效地测试一些这种Stuck open/short的faults,但是会节省很多测试时间和测试成本。如下面图(5)上半部分所示,右边的那个P沟道MOS管发生了Stuck short(on)的faults,图的下半部分展示了输入AB的四种不同的情况,当AB输入为00时,看起来这个晶体管表现地正常;但是当AB输入为11时,地和电源间存在一个直接导通的电路,输出端Z的状态是异常的。 图(5)此时VDD上的漏电比较大,也可以通过测量VDD上面的电流来判断正误,即IDDQ的测试方法,后面会详细地介绍这种方法。

图(5)此时VDD上的漏电比较大,也可以通过测量VDD上面的电流来判断正误,即IDDQ的测试方法,后面会详细地介绍这种方法。

桥接(Bridge Faults)

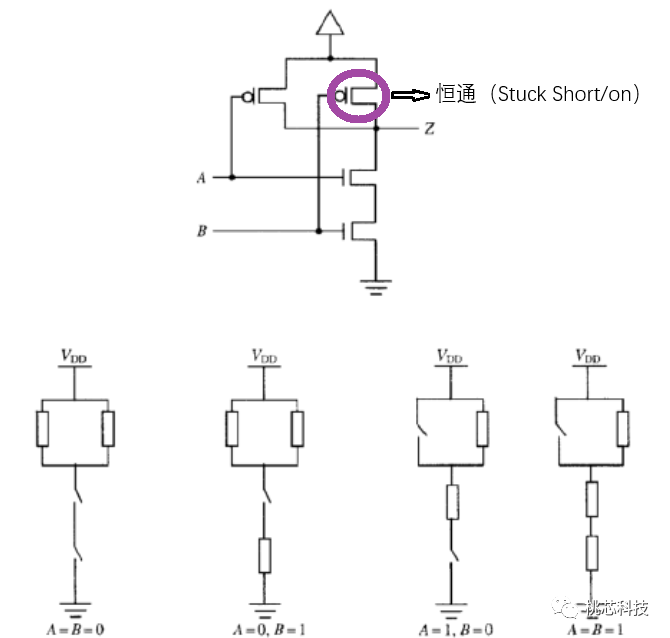

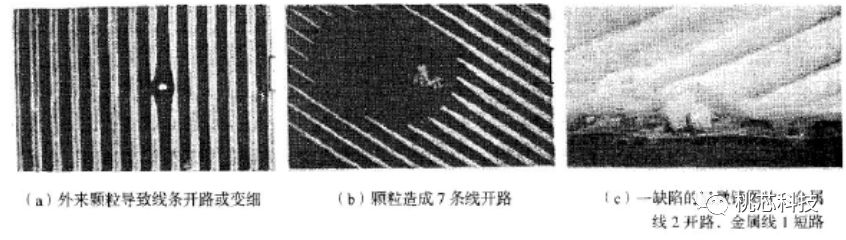

桥接缺陷是由于电路中两个或多个电节点之间短路造成的,而设计中并未设计这种短接。这些短接的节点可能是某一个晶体管的,也可能是几个晶体管之间的,可能处于芯片上同一层,也可能处于不同层。下面图(6)是桥接缺陷的几种图例。 图(6)上图中,(a)是因曝光不足导致7条金属线桥接子在一起的情形;(b)是外来颗粒的介入导致4条金属线桥接在一起的情形;(c)是因掩模划伤导致桥接的情形;(d)是1um大小的缺陷造成短路的情形;(e)是金属化缺陷导致2条金属线桥接的情形;(f)则是层间短路情形。上述情形中虽然导致缺陷的原因各有不同,但结果都是桥接。同样的,桥接测试也可以通过电压的方法完成,即run pattern方式,也就是stuck at的模式进行检测,但是电流测试是发现电压测试无法检查的故障的有效方法。下面图(7)表示的是mos管的source和drain桥接了。

图(6)上图中,(a)是因曝光不足导致7条金属线桥接子在一起的情形;(b)是外来颗粒的介入导致4条金属线桥接在一起的情形;(c)是因掩模划伤导致桥接的情形;(d)是1um大小的缺陷造成短路的情形;(e)是金属化缺陷导致2条金属线桥接的情形;(f)则是层间短路情形。上述情形中虽然导致缺陷的原因各有不同,但结果都是桥接。同样的,桥接测试也可以通过电压的方法完成,即run pattern方式,也就是stuck at的模式进行检测,但是电流测试是发现电压测试无法检查的故障的有效方法。下面图(7)表示的是mos管的source和drain桥接了。 图(7)上面图中,因为上面的P沟通的MOS管的source和drain桥接了,电源VDD上会有很大的漏电,用电流测试方法,可以很快发现问题。

图(7)上面图中,因为上面的P沟通的MOS管的source和drain桥接了,电源VDD上会有很大的漏电,用电流测试方法,可以很快发现问题。

开路故障(Open)

开路缺陷是制造工艺不当造成的,物理缺陷中大约40%属于开路缺陷。典型的开路缺陷包括线条断开、线条变细、阻性开路和渐变开路等。如下面图(8)所示: 图(8)图中(a)和(b)是电路存在开路的情形,(c)则是造成同时开路和短路缺陷的情形。开路缺陷的形式取决于缺陷的位置及大小。例如,对于栅极开路(一般称为浮栅,floating gate)这种缺陷,在缺陷面积小的情况下,隧道电流仍可流动,但信号的上升和下降时间增加;在缺陷面积大的情况下,输入信号就在栅极形成耦合,形成的浮栅就获得偏压,此电压可能导致晶体管导通,因此开路故障是否可检测,取决于缺陷的面积和位置。开路缺陷不一定都可以用Stuck At的模式检测到,如下面图(9)所示:

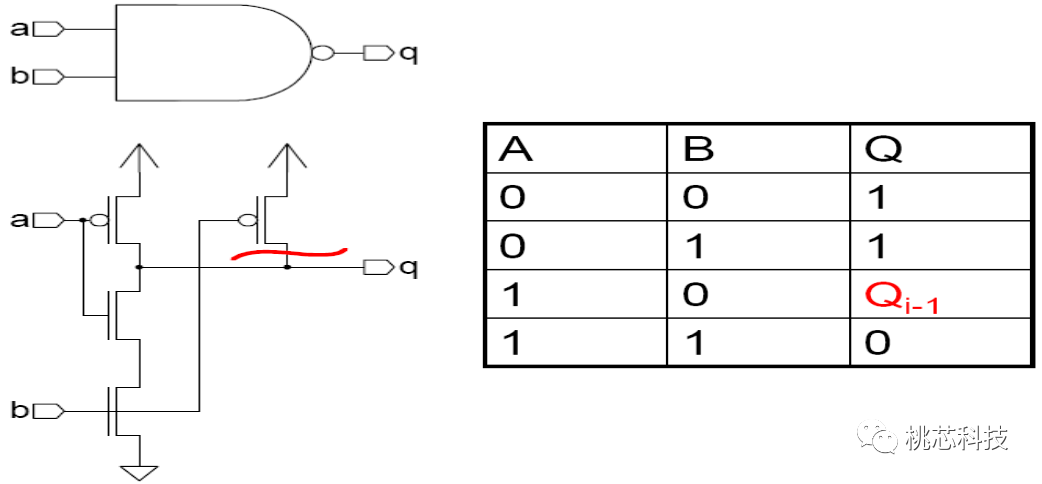

图(8)图中(a)和(b)是电路存在开路的情形,(c)则是造成同时开路和短路缺陷的情形。开路缺陷的形式取决于缺陷的位置及大小。例如,对于栅极开路(一般称为浮栅,floating gate)这种缺陷,在缺陷面积小的情况下,隧道电流仍可流动,但信号的上升和下降时间增加;在缺陷面积大的情况下,输入信号就在栅极形成耦合,形成的浮栅就获得偏压,此电压可能导致晶体管导通,因此开路故障是否可检测,取决于缺陷的面积和位置。开路缺陷不一定都可以用Stuck At的模式检测到,如下面图(9)所示: 图(9)上图中,红线部分表示那个mos管的drain与输出开路了,当顺序输入ab为00、01、10、11,从01变换为10的时候,输出Q保持了上面一个状态1,看起来还是正常的,这种情况下,就没有检测出来这个fault。但是如果调整一下输入的向量的顺序为00、01、11、10,就可以发现这个fault。通过IDD的测试方法,也可以测试出一些open缺陷,如下面的图(10)所示

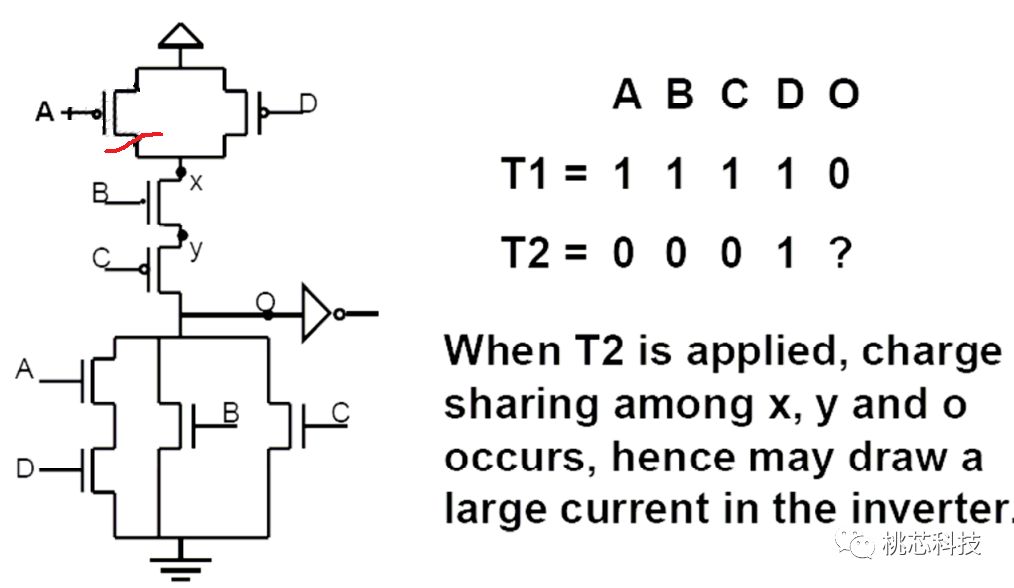

图(9)上图中,红线部分表示那个mos管的drain与输出开路了,当顺序输入ab为00、01、10、11,从01变换为10的时候,输出Q保持了上面一个状态1,看起来还是正常的,这种情况下,就没有检测出来这个fault。但是如果调整一下输入的向量的顺序为00、01、11、10,就可以发现这个fault。通过IDD的测试方法,也可以测试出一些open缺陷,如下面的图(10)所示 图(10)上面红色表示open的缺陷,当输入ABCD为1111时,输出O为0,当输出转为0001时候,在x、y和o之间出现了充放电,会有大电流出现。

图(10)上面红色表示open的缺陷,当输入ABCD为1111时,输出O为0,当输出转为0001时候,在x、y和o之间出现了充放电,会有大电流出现。

延迟缺陷(delay faults)

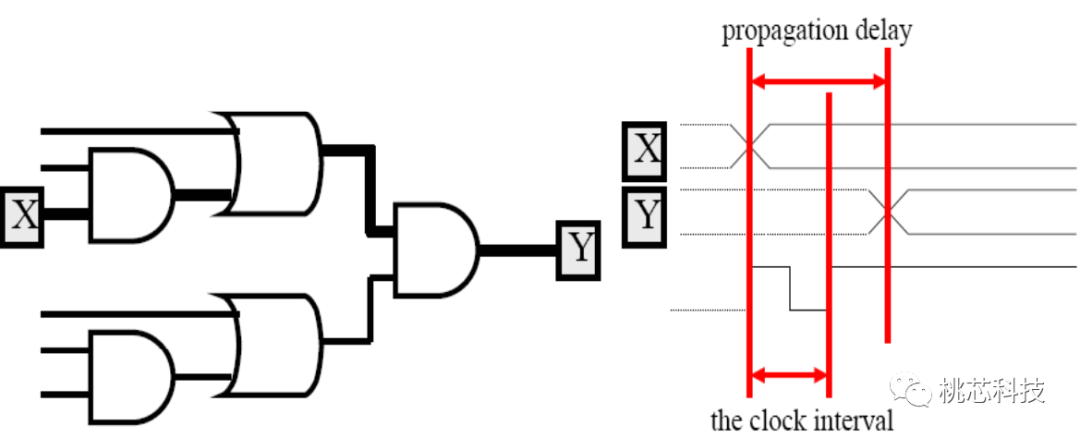

在一些高速芯片应用中,延迟缺陷特别重要,这种缺陷有很多原因,比如小面积的open导致某段线路的阻值偏大。如下面图(11)所示: 图(11)这个path的delay已经超过了一个clock的间隙,通过stuck At的测试方式,可以检测到这个缺陷。但是有的时候,延迟没有超过clock的间隙,就会造成潜在的失效,在某些情况下,比如硬件变化、外界温度变化等,延迟超过clock的间隙,导致缺陷。这种延迟缺陷,可以通过AC测试的方法进行补充,比如测试上升沿的时间、下降沿的时间等等。2

图(11)这个path的delay已经超过了一个clock的间隙,通过stuck At的测试方式,可以检测到这个缺陷。但是有的时候,延迟没有超过clock的间隙,就会造成潜在的失效,在某些情况下,比如硬件变化、外界温度变化等,延迟超过clock的间隙,导致缺陷。这种延迟缺陷,可以通过AC测试的方法进行补充,比如测试上升沿的时间、下降沿的时间等等。2

Pattern向量测试及IDDQ测试方法

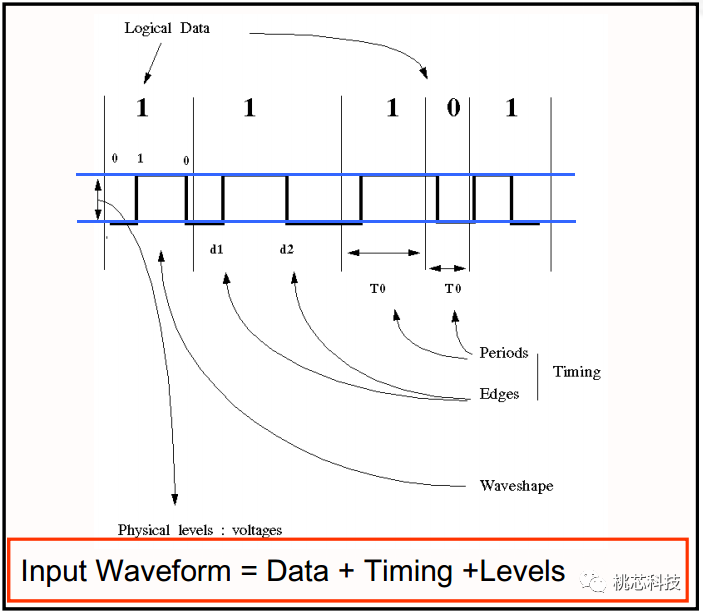

上面给大家介绍了一下各种失效模式及测试原理。通过Pattern向量测试,加以电流测试为补充,可以有效地测试各种faults。Pattern向量测试的方法设计人员对某种fault模型进行仿真,给出波形向量,通常是VCD格式或者WGL格式,测试人员需要结合时序、电平和逻辑,进行编程,来对芯片输入向量,以检测输出。如下面图(12)表示的就是测试机force给芯片的一段波形。 图(12)而芯片在接受到这段输入的波形后,运行特定的逻辑,输出波形如下面图(13),测试机需要在指定的strobe window进行比较输出的与预期的逻辑值的情况,以此来判断DUT是否逻辑功能正常。

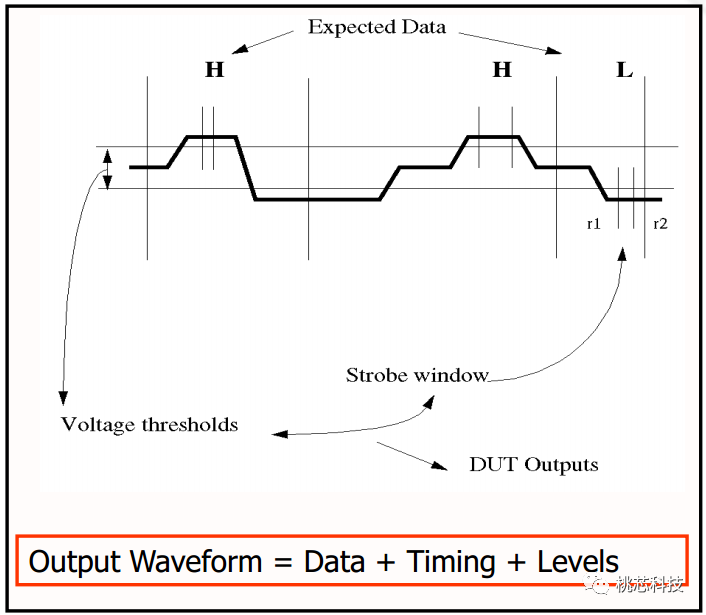

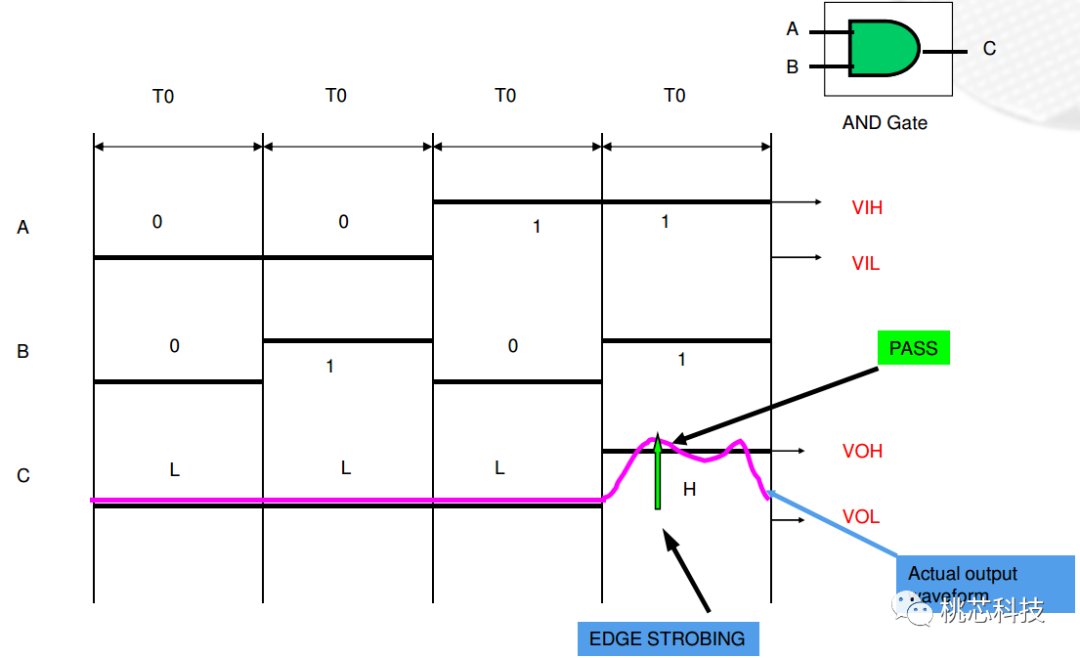

图(12)而芯片在接受到这段输入的波形后,运行特定的逻辑,输出波形如下面图(13),测试机需要在指定的strobe window进行比较输出的与预期的逻辑值的情况,以此来判断DUT是否逻辑功能正常。 图(13)下面图(14)是一个AND gate的逻辑测试的例子,实际的输出会有波动,如图中的紫色的波形,在Edge Strobing地方(pattern的timing设定的)采样到此时的输出为High的状态,表明此AND Gate的逻辑功能是正常。

图(13)下面图(14)是一个AND gate的逻辑测试的例子,实际的输出会有波动,如图中的紫色的波形,在Edge Strobing地方(pattern的timing设定的)采样到此时的输出为High的状态,表明此AND Gate的逻辑功能是正常。 图(14)IDDQ测试的方法:CMOS电路具有低功耗的优点,静态条件下由泄露电流引起的功耗可以忽略,仅仅在转换期间电路从电源消耗较大的电流。Q代表静态(quiescent),则IDDQ表示MOS电流静态时从电源获取的电流。IDDQ测试是源于物理缺陷的测试,也是可靠性测试的一部分,其有着测试成本低和能从根本上找出电路的问题(缺陷)所在的特点。即若在电压测试生成中加入少量的IDDQ测试图形,就可以大幅度提高电压测试的覆盖率。即使电路功能正常,IDDQ测试仍可以检测出桥接、短路、栅氧短路等物理缺陷。测试方法如下面图(15)所示

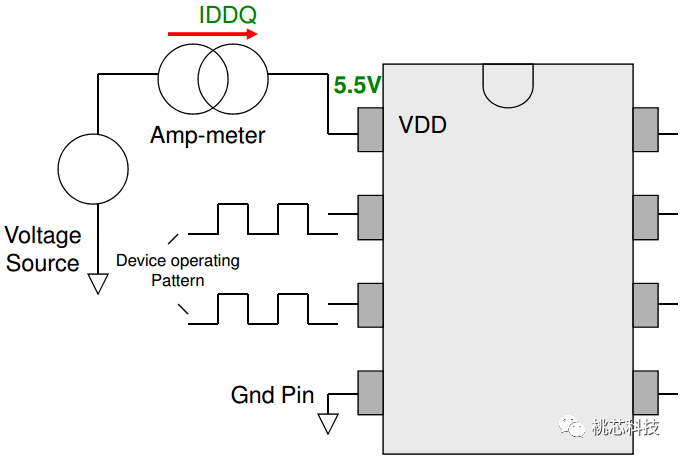

图(14)IDDQ测试的方法:CMOS电路具有低功耗的优点,静态条件下由泄露电流引起的功耗可以忽略,仅仅在转换期间电路从电源消耗较大的电流。Q代表静态(quiescent),则IDDQ表示MOS电流静态时从电源获取的电流。IDDQ测试是源于物理缺陷的测试,也是可靠性测试的一部分,其有着测试成本低和能从根本上找出电路的问题(缺陷)所在的特点。即若在电压测试生成中加入少量的IDDQ测试图形,就可以大幅度提高电压测试的覆盖率。即使电路功能正常,IDDQ测试仍可以检测出桥接、短路、栅氧短路等物理缺陷。测试方法如下面图(15)所示 图(15)Step1: 给VDD上最高电压,并且tester的电压源设定一个钳制电流,防止电流过大损测试机。Step2: run一个特定condition的pattern,去toggle尽量多的晶体管on。等待 5~10ms。Step3: 量测流过VDD上的电流。Step4: run另外一个特定condition的pattern,去toggle尽量多的晶体管off。等待5~10ms。Step5: 量测流过VDD上的电流。Step6: 重复上述的step2到step5的步骤大概5~10次,取读出的平均值。跟datasheet中的规范进行比较。各种测试的测试覆盖率的大概情况如下面图(16)所示:

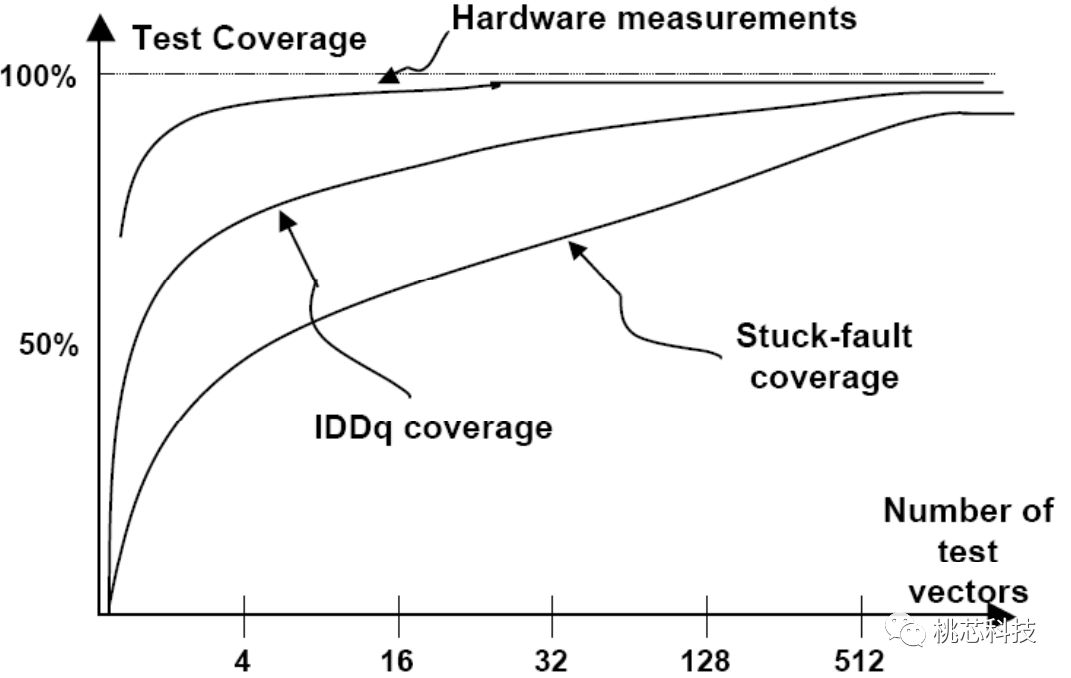

图(15)Step1: 给VDD上最高电压,并且tester的电压源设定一个钳制电流,防止电流过大损测试机。Step2: run一个特定condition的pattern,去toggle尽量多的晶体管on。等待 5~10ms。Step3: 量测流过VDD上的电流。Step4: run另外一个特定condition的pattern,去toggle尽量多的晶体管off。等待5~10ms。Step5: 量测流过VDD上的电流。Step6: 重复上述的step2到step5的步骤大概5~10次,取读出的平均值。跟datasheet中的规范进行比较。各种测试的测试覆盖率的大概情况如下面图(16)所示: 图(16)如上图所示,hardware直接量测是最直接的方法,但是这种方法可以测试的电路有限,很多内部电路无法通过这种方法完成。而Stuck At测试和IDDQ测试的组合,可以有效的在时间和成本经济的情况下提高测试覆盖率。3

图(16)如上图所示,hardware直接量测是最直接的方法,但是这种方法可以测试的电路有限,很多内部电路无法通过这种方法完成。而Stuck At测试和IDDQ测试的组合,可以有效的在时间和成本经济的情况下提高测试覆盖率。3

其它的Hardware测试介绍

连通性测试介绍

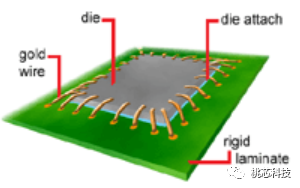

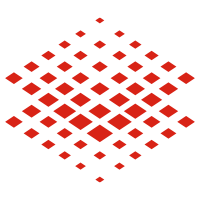

连通性测试是测试芯片的管脚是否有确实连接到测试机之上,芯片的管脚之间是否有短路的一种测试,通常情况下,这项测试会放在第一项进行,因为连通性测试可以很快发现测试机的setup问题,以及芯片管脚开短路的问题,从而在第一时间发现bad dut,节省测试成本。如下图(17)所示的一个封装芯片的剖面图,造成连通性失效主要有这几个原因:a) 制造过程中的问题,引起某些pin脚的开短路。b) 封装中的missing bonding wires,会造成开路。c) 静电问题,造成某个pin被打坏从而造成开短路问题。d) 封装过程中造成的die crack或者某个pin脚的弯曲。 图(17)这个测试主要是去测试pin的ESD保护二极管。一般情况下,会把open/short测试放在一个项目里同时测试,也有情况是需要分开测试这两个项目。测试某个pin到ground/其它pin之间的连通性,如下图(18),

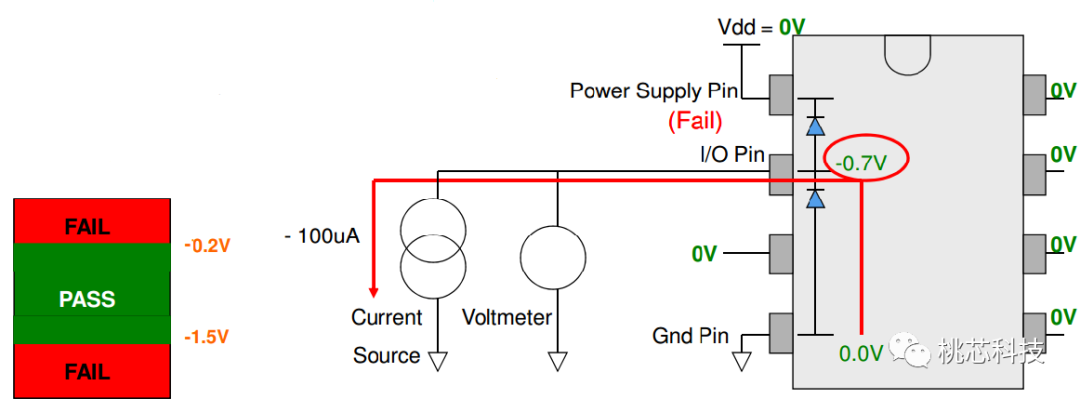

图(17)这个测试主要是去测试pin的ESD保护二极管。一般情况下,会把open/short测试放在一个项目里同时测试,也有情况是需要分开测试这两个项目。测试某个pin到ground/其它pin之间的连通性,如下图(18), 图(18)Step1: 所有不测试的pin都置0v。Step2: 在需要测试的pin上source一个-100uA的电流。Step3: 量测这个在测试的pin上的电压--如果tester与这个测试pin接触很好,并且这个pin本身没有任何的开路或者短路到VDD/ground/其它的pin脚上,那么理想的测试到的电压会是-0.7v。--如果这个在测试的pin有开路的fault,会量测到一个大的负电压。--如果这个在测试的pin有短路到vdd/ground/其它的pin上,会量测到一个接近0v的电压。考虑到实际的电路的情况,一般limit设置为-1.5V ~-0.2V。测试某个pin到VDD/其它pin之间的连通性,如下图(19)

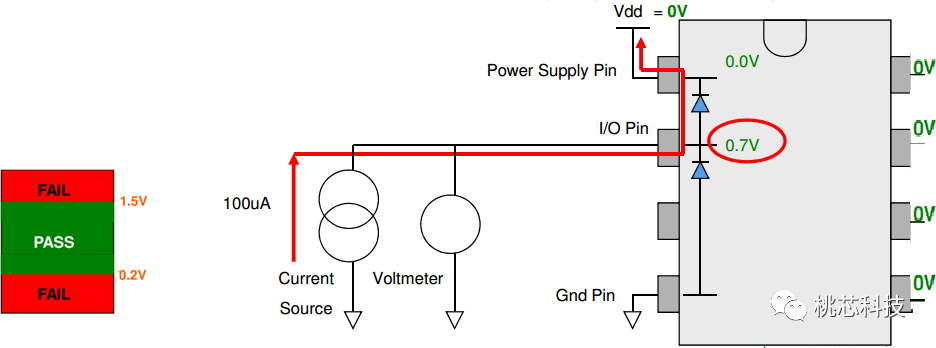

图(18)Step1: 所有不测试的pin都置0v。Step2: 在需要测试的pin上source一个-100uA的电流。Step3: 量测这个在测试的pin上的电压--如果tester与这个测试pin接触很好,并且这个pin本身没有任何的开路或者短路到VDD/ground/其它的pin脚上,那么理想的测试到的电压会是-0.7v。--如果这个在测试的pin有开路的fault,会量测到一个大的负电压。--如果这个在测试的pin有短路到vdd/ground/其它的pin上,会量测到一个接近0v的电压。考虑到实际的电路的情况,一般limit设置为-1.5V ~-0.2V。测试某个pin到VDD/其它pin之间的连通性,如下图(19) 图(19)Step1: 所有不测试的pin都置0v。Step2: 在需要测试的pin上source一个100uA的电流。Step3: 量测这个在测试的pin上的电压。--如果tester与这个测试pin接触很好,并且这个pin本身没有任何的开路或者短路到VDD/ground/其它的pin脚上,那么理想的测试到的电压会是0.7v。--如果这个在测试的pin有开路的fault,会量测到一个大的正电压。--如果这个在测试的pin有短路到vdd/ground/其它的pin上,会量测到一个接近0v的电压。考虑到实际的电路的情况,一般limit设置为0.2V~1.5V。

图(19)Step1: 所有不测试的pin都置0v。Step2: 在需要测试的pin上source一个100uA的电流。Step3: 量测这个在测试的pin上的电压。--如果tester与这个测试pin接触很好,并且这个pin本身没有任何的开路或者短路到VDD/ground/其它的pin脚上,那么理想的测试到的电压会是0.7v。--如果这个在测试的pin有开路的fault,会量测到一个大的正电压。--如果这个在测试的pin有短路到vdd/ground/其它的pin上,会量测到一个接近0v的电压。考虑到实际的电路的情况,一般limit设置为0.2V~1.5V。

DC参数测试(DC Parameters Test)

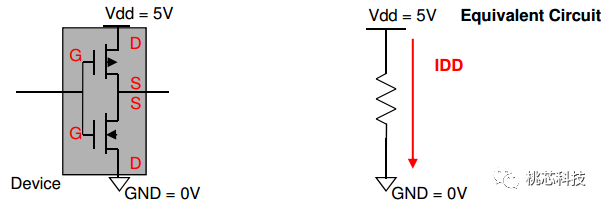

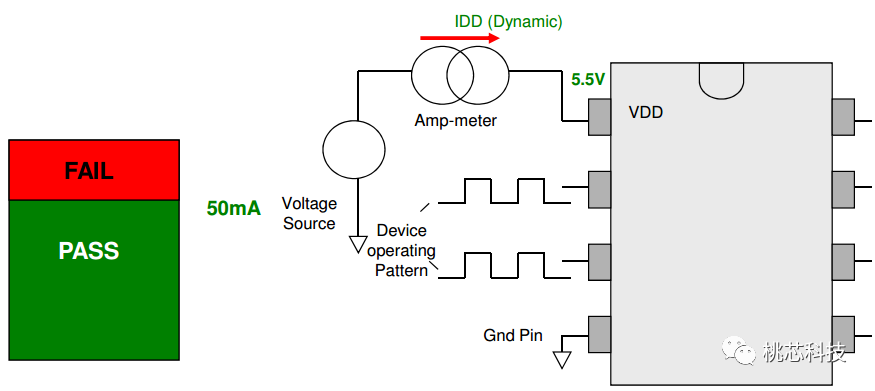

DC参数的测试,一般都是force电流测试电压或者force电压测试电流,主要是测试阻抗性。一般各种DC参数都会在datasheet里面标明,测试的主要目的是确保delivery的芯片的DC参数值符合规范。IDD测试IDD测试(或者叫做ICC测试),在CMOS电路中是测试Drain to Drain的流动电流的,在TTL电路中是测试Collector to Collector的流动电流。如下面图(20)所示: 图(20)Gross IDD/ICC Test (power pin short test)电源pin的短路测试,通常Open/short测试后马上进行,如果在制造过程中有issue,导致了电源到地的短路,会测试到非常大的电流,也会反过来损害到测试机本身。测试的基本方法如下面图(21)所示

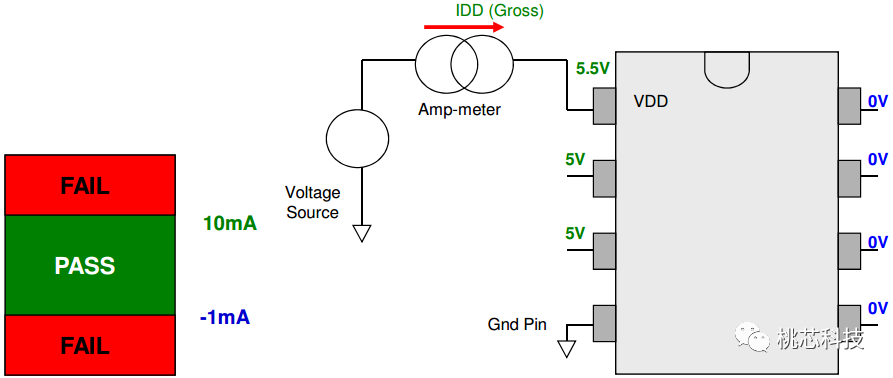

图(20)Gross IDD/ICC Test (power pin short test)电源pin的短路测试,通常Open/short测试后马上进行,如果在制造过程中有issue,导致了电源到地的短路,会测试到非常大的电流,也会反过来损害到测试机本身。测试的基本方法如下面图(21)所示 图(21)Step1: 给VDD上最高电压,并且tester的电压源设定一个钳制电流,防止电流过大损测试机。Step2: 所有的输入pin置高,所有的输出pin置0. 等待5~10ms。Step3: 量测流过VDD上的电流,正向或者反向电流过高都说明电源到地短路了。Static IDD/ICC Test (静态功耗测试)这个项目是测试当芯片在静态或者idle state的情况下,流过VDD的漏电,这个参数对低功耗应用场景特别重要;这项测试也能检测出一些在制造中产生的margin defect,这些defect非常有可能会给芯片带来潜在的可靠性风险。测试方法与下面图(22)所示

图(21)Step1: 给VDD上最高电压,并且tester的电压源设定一个钳制电流,防止电流过大损测试机。Step2: 所有的输入pin置高,所有的输出pin置0. 等待5~10ms。Step3: 量测流过VDD上的电流,正向或者反向电流过高都说明电源到地短路了。Static IDD/ICC Test (静态功耗测试)这个项目是测试当芯片在静态或者idle state的情况下,流过VDD的漏电,这个参数对低功耗应用场景特别重要;这项测试也能检测出一些在制造中产生的margin defect,这些defect非常有可能会给芯片带来潜在的可靠性风险。测试方法与下面图(22)所示 图(22)Step1: 给VDD上最高电压,并且tester的电压源设定一个钳制电流,防止电流过大损测试机。Step2: 跑pre-condition pattern,把芯片设置到低功耗状态。等待5~10ms。Step3: 量测流过VDD上的电流,根据datasheet中的标识设定limit,超过limit即表示坏品。Dynamic IDD/ICC Test (动态功耗测试)这个项目是测试当芯片在不停地运行某种function的情况下,流过VDD的电流。这个类似于某种工作情况下的功耗,需要meet产品spec中的值,对于功耗要求严格的应用方案,此项指标非常重要。测试方法如下面图(23)所示:

图(22)Step1: 给VDD上最高电压,并且tester的电压源设定一个钳制电流,防止电流过大损测试机。Step2: 跑pre-condition pattern,把芯片设置到低功耗状态。等待5~10ms。Step3: 量测流过VDD上的电流,根据datasheet中的标识设定limit,超过limit即表示坏品。Dynamic IDD/ICC Test (动态功耗测试)这个项目是测试当芯片在不停地运行某种function的情况下,流过VDD的电流。这个类似于某种工作情况下的功耗,需要meet产品spec中的值,对于功耗要求严格的应用方案,此项指标非常重要。测试方法如下面图(23)所示: 图(23)Step1: 给VDD上最高电压,并且tester的电压源设定一个钳制电流,防止电流过大损测试机。

图(23)Step1: 给VDD上最高电压,并且tester的电压源设定一个钳制电流,防止电流过大损测试机。

Step2: 让芯片持续不断的运行特定的pattern,等待5~10ms。Step3: 量测流过VDD上的电流,根据datasheet中的标识设定limit,超过limit表示坏品。

Leakage测试

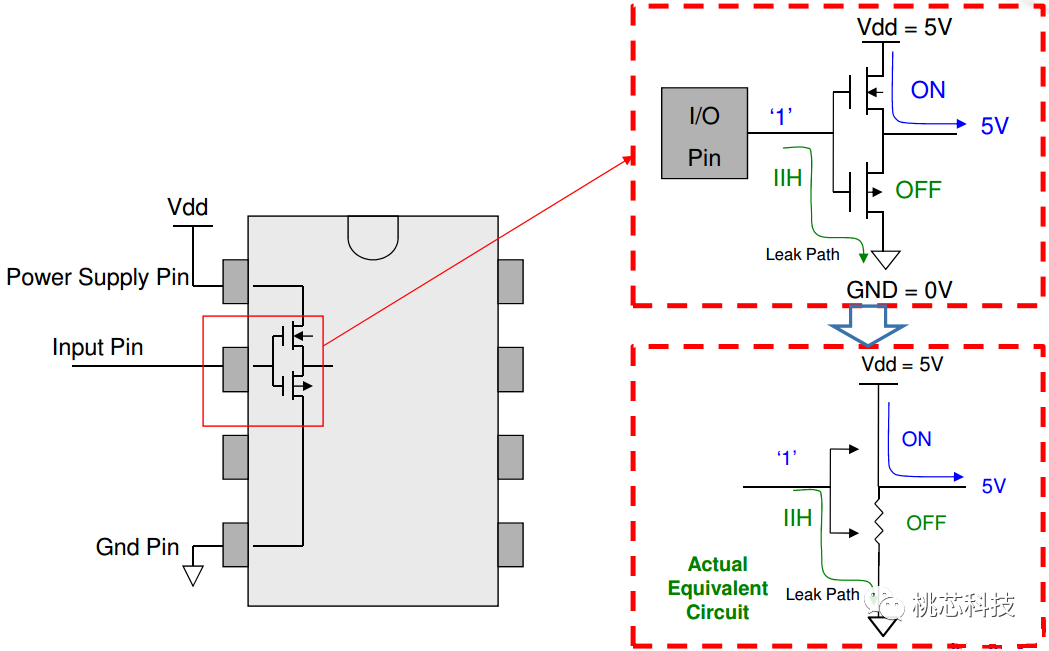

芯片内部晶体管不可能在理想的状态,因此或多或少会存在一定的漏电流,需要测试漏电,保证漏电是在正常的允许的范围内,而不是潜在的defect。Input Leakage Test(IIH and IIL)IIH是当芯片的某个input pin被设定为输入VIH时,从这个input pin到芯片的ground之间的漏电流,如下图(24)所示 图(24)IIL是当芯片的某个input pin被设定为输入VIL时,从芯片的VDD 到这个input pin的之间的漏电流,如下图(25)所示

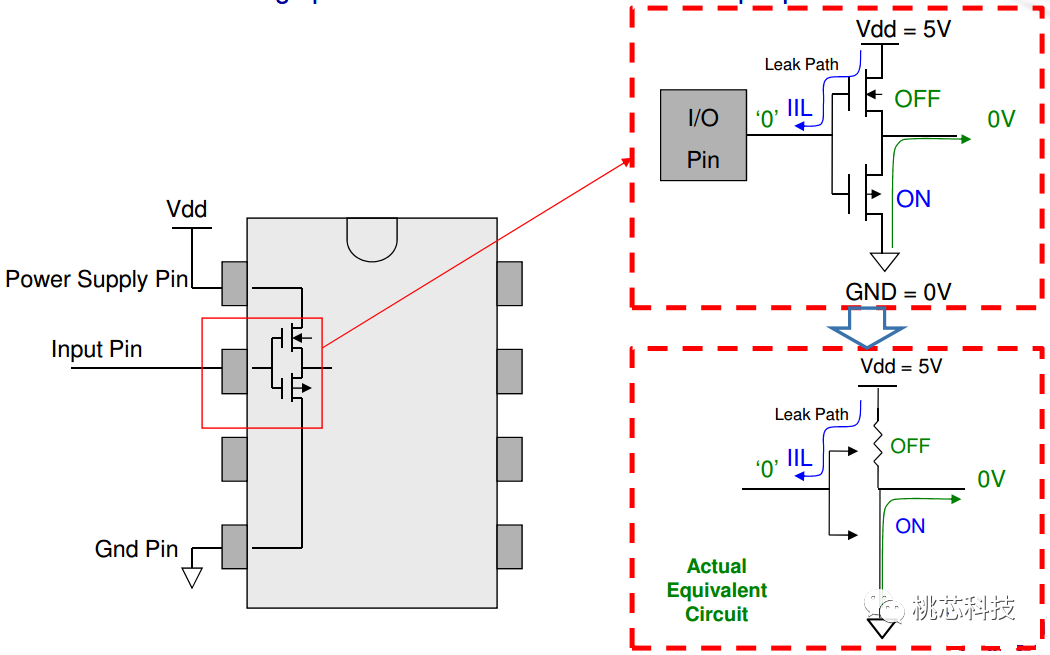

图(24)IIL是当芯片的某个input pin被设定为输入VIL时,从芯片的VDD 到这个input pin的之间的漏电流,如下图(25)所示 图(25)Output Tristate Leakage Test(IOZL and IOZH)Tristate表示的是输出pin是高阻状态,当这个时候,如果输出pin上有电压VDD,那么从输出pin到芯片的ground上会有漏电(IOZH);如果输出pin接地,那么从芯片的VDD到这个输出pin上也会有漏电(IOZL),如下面图(26)所示,这些漏电必须保持在spec规定的范围内,以确保芯片的正常工作,不会有潜在的defect产生。

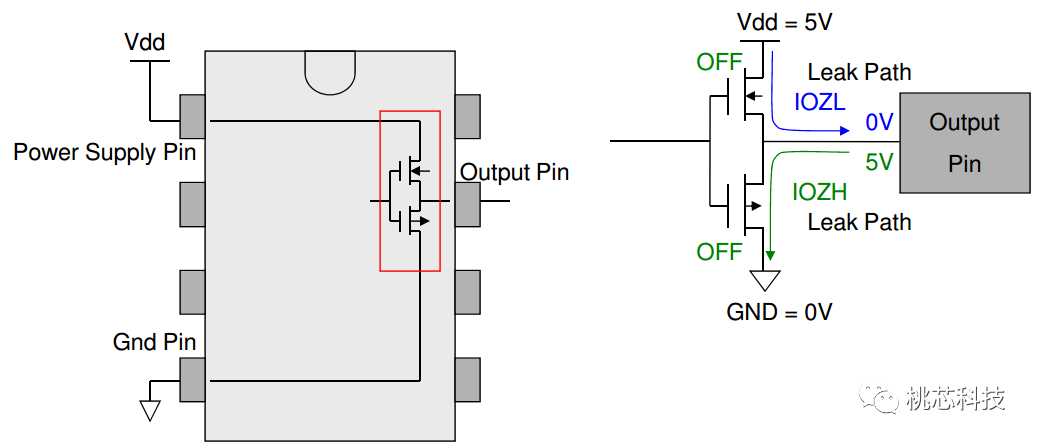

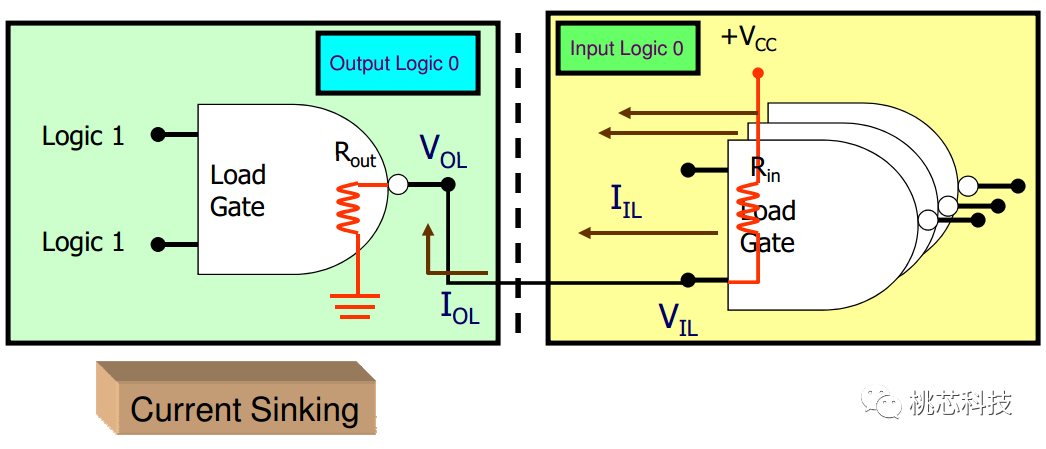

图(25)Output Tristate Leakage Test(IOZL and IOZH)Tristate表示的是输出pin是高阻状态,当这个时候,如果输出pin上有电压VDD,那么从输出pin到芯片的ground上会有漏电(IOZH);如果输出pin接地,那么从芯片的VDD到这个输出pin上也会有漏电(IOZL),如下面图(26)所示,这些漏电必须保持在spec规定的范围内,以确保芯片的正常工作,不会有潜在的defect产生。 图(26)Output Logic Low DC Test(VOL/IOL)VOL表示的是当输出pin为状态low的时候的最大电压,IOL表示的是在此种状态下这个输出pin的最大的电流驱动能力,这个项目是测试当此状态下的输出pin对地的电阻大小,如下面图(27)所示。

图(26)Output Logic Low DC Test(VOL/IOL)VOL表示的是当输出pin为状态low的时候的最大电压,IOL表示的是在此种状态下这个输出pin的最大的电流驱动能力,这个项目是测试当此状态下的输出pin对地的电阻大小,如下面图(27)所示。 图(27)Output Logic High DC Test(VOH/IOH)VOH表示的是当输出pin为状态high的时候的最小电压,IOH表示的是在此种状态下这个输出pin的最大的电流驱动能力,这个项目是测试当此状态下的芯片的VDD到这个输出pin的电阻大小,如下面图(28)所示。

图(27)Output Logic High DC Test(VOH/IOH)VOH表示的是当输出pin为状态high的时候的最小电压,IOH表示的是在此种状态下这个输出pin的最大的电流驱动能力,这个项目是测试当此状态下的芯片的VDD到这个输出pin的电阻大小,如下面图(28)所示。 图(28)随着芯片工艺越来越先进,晶体管密度越来越高,芯片测试的复杂度和难度也成倍地增长。本文通过各种失效模式及检测机理的讨论,梳理了一下基本的测试概念。后续我们会再针对混合信号测试、RF测试、DFT测试进行一些探讨,谢谢!

图(28)随着芯片工艺越来越先进,晶体管密度越来越高,芯片测试的复杂度和难度也成倍地增长。本文通过各种失效模式及检测机理的讨论,梳理了一下基本的测试概念。后续我们会再针对混合信号测试、RF测试、DFT测试进行一些探讨,谢谢!

北京汉通达科技主要业务为给国内用户提供通用的、先进国外测试测量设备和整体解决方案,产品包括多种总线形式(台式/GPIB、VXI、PXI/PXIe、PCI/PCIe、LXI等)的测试硬件、相关软件、海量互联接口等。经过二十年的发展,公司产品辐射全世界二十多个品牌,种类超过1000种。值得一提的是,我公司自主研发的BMS测试产品、芯片测试产品代表了行业一线水平

-

芯片

+关注

关注

458文章

51519浏览量

429428 -

测试

+关注

关注

8文章

5454浏览量

127375

发布评论请先 登录

相关推荐

Advantest CEO:先进芯片测试需求大增

科技少年梦 科普粤海行|芯海科技科普基地启迪智慧未来

soc芯片测试有哪些参数和模块

龙芯中科成功举办少年开放日系列科普活动

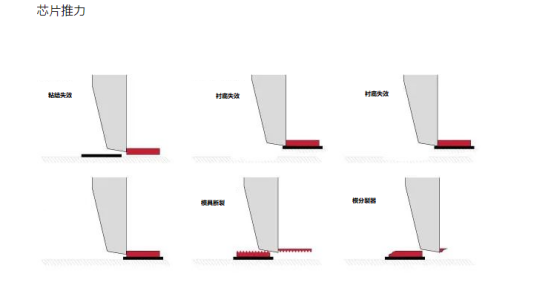

想了解芯片推力测试?点击这里,了解最新测试方法!

芯片的出厂测试与ATE测试的实施方法

为什么要进行芯片测试?芯片测试在什么环节进行?

芯片测试科普

芯片测试科普

评论