- PCB板布线错误;

- 单片机质量有问题;

- 晶振质量有问题;

- 负载电容或匹配电容与晶振不匹配或者电容质量有问题;

- PCB板受潮,导致阻抗失配而不能起振;

- 晶振电路的走线过长;

- 晶振两脚之间有走线;

- 外围电路的影响。

- 排除电路错误的可能性,因此你可以用相应型号单片机的推荐电路进行比较。

- 排除外围元件不良的可能性,因为外围零件无非为电阻,电容,你很容易鉴别是否为良品。

- 排除晶振为停振品的可能性,因为你不会只试了一二个晶振。

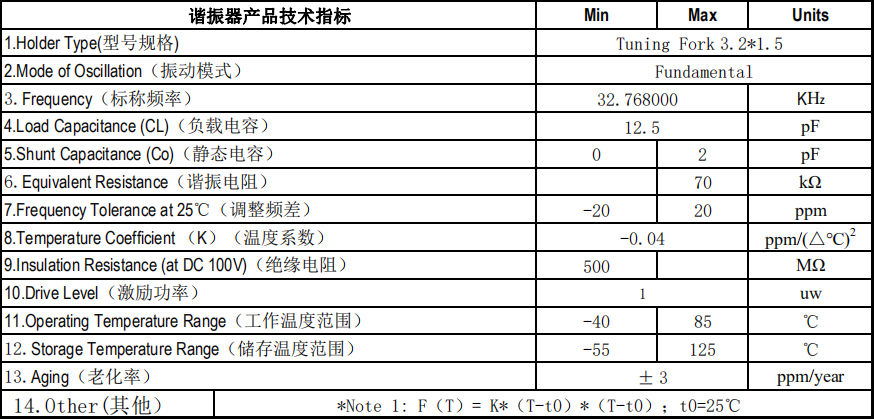

- 试着改换晶体两端的电容,也许晶振就能起振了,电容的大小请参考晶振的使用说明。

- 在PCB布线时晶振电路的走线应尽量短且尽可能靠近IC,杜绝在晶振两脚间走线。

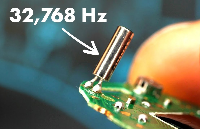

32.768kHz晶振是市面上使用最为广泛的一类晶振。爱普生/EPSON目前提供三类32.768kHz晶振产品以满足客户不同需要,分别是:32.768kHz有源晶振(OSC),32.768kHz无源晶振(X’tal)和内置32.768kHz晶体谐振器的实时时钟模块(RTC)。

有源晶振(OSC)和实时时钟模块(RTC)由于内置了相应的电路,因而不太容易出现不起振的问题。在实际使用时不需要考虑相对复杂的频率匹配问题。

不起振的情况主要出现在无源晶振上,尤其是kHz级别的无源晶振(X’tal),而MHz级别的AT晶振则相对少见。

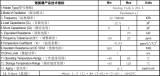

电路结构与晶体单元不匹配。由此导致产生频率不够稳定、停止起振或振荡不稳定等问题。因此在电路设计时,为了获得稳定的振荡,通常情况下石英晶体单元与振荡电路的匹配十分重要。

解决晶振不起振至少要对以下三个要素:对振荡频率(频率匹配)、振荡裕度(负阻抗)和激励功率的三项进行评估

电路结构与晶体单元不匹配。由于概率问题,在小批量试产时由于数量少,没有及时发现。

如何避免晶振不起振导致的时间延误、不良率高

晶振本身的一致性、稳定性好是解决不起振问题的关键之一。如果晶振本身的稳定性、一致性不好,电路结构与其的匹配就无从谈起。

尽可能选择有源晶振,有源晶振的价格要比无源晶体贵,但是由于原厂已经配置好了内部电路,基本不存在电路匹配问题,也就极大避免了晶振不起振问题的发生。

-

晶振

+关注

关注

34文章

2870浏览量

68074 -

时钟

+关注

关注

11文章

1734浏览量

131527

发布评论请先 登录

相关推荐

低功耗输出频率32.768kHz的汽车用晶振SG-3031CMA

为什么32.768KHz晶振这么火? 到底应用在哪些领域?

爱普生32.768kHz晶振FC-135:小型化为高端产品带来的卓越优势

32.768Khz晶振使用经验分享

SMD3215 32.768KHZ贴片晶振 ±20ppm,批量价6毛5左右

32.768kHz晶振不起振的原因与解决

32.768kHz晶振不起振的原因与解决

评论