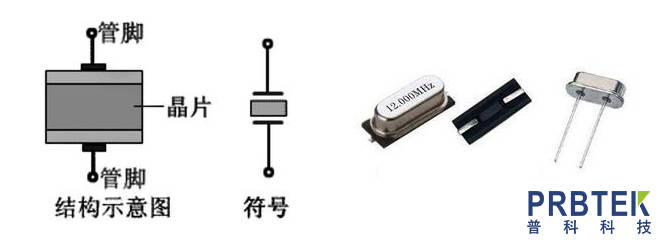

晶振在单片机中的重要性不言而喻,但是,作为单片机中记录工作频率的软件,它又是非常脆弱的。轻微的触碰都可能导致其功能失常。因此,单片机晶振不起振也是常见现象。很多客户会咨询这方面的问题,本文就针对单片机晶振经常遇到的问题及解决方法给大家做下介绍。

首先,我们分析引起单片机晶振不起振的原因有哪些?

1、PCB布线错误,现在的PCB不再是单一功能电路(数字或模拟电路),而是由数字电路和模拟电路混合组成的。因此,PCB布线的时候可能出现问题导致晶振不起振。

(晶振电路设计考虑事项:

1.位置要选对:晶振内部是石英晶体,如果不慎掉落或受不明撞击,石英晶体易断裂破损,所以晶振的放置远离板边,靠近MCU的位置布局。

2.两靠近:耦合电容应尽量靠近晶振的电源管脚,如果多个耦合电容,按照电源流入方向,依次容值从大到小摆放;晶振则要尽量的靠近MCU。

3.走线短:所有连接晶振输入/输出端的导线尽量短,以减少噪声干扰及分布电容对晶振的影响。

使晶振、外部电容器(如果有)与 IC之间的信号线尽可能保持最短。当非常低的电流通过IC晶振振荡器时,如果线路太长,会使它对 EMC、ESD与串扰产生非常敏感的影响。而且长线路还会给振荡器增加寄生电容。

4.高独立:尽可能保证晶振周围的没有其他元件。防止器件之间的互相干扰,影响时钟和其他信号的质量。晶振周围 1mm禁布器件,0.5mm禁布过孔走线,所有晶振下不打过孔(包括地过孔)。当心晶振和地的走线。

5.尽可能将其它时钟线路与频繁切换的信号线路布置在远离晶振连接的位置。

6.外壳要接地:晶振的外壳必须要接地,除了防止晶振向外辐射,也可以屏蔽外来的干扰。

如果实际的负载电容配置不当,第一会引起线路参考频率的误差.另外如在发射接收电路上会使晶振的振荡幅度下降(不在峰点),影响混频信号的信号强度与信噪.当波形出现削峰,畸变时,可增加负载电阻调整(几十K到几百K).要稳定波形是并联一个1M左右的反馈电阻.)

2、单片机或晶振的质量问题;

3、负载二极管或匹配电容与晶振不匹配或者电容质量有问题;

4、PCB板受潮,导致阻抗失配而不能起振;

5、晶振电路的走线过长或两脚之间有走线导致晶振不起振,通常我们在PCB布线时晶振电路的走线应尽量短且尽可能靠近振荡器,严禁在晶振两脚间走线;

6、晶振受外围电路的影响而不起振。

除此之外还有其他的原因需要注意:

1、晶振的选型,选择合适的晶振对单片机来说非常重要,我们在选择晶振的时候至少必须考虑谐振频点、负载电容、激励功率、温度特性长期稳定性等参数。合适的晶振才能确保单片机能够正常工作。

2、电容引起的晶振不稳定,晶振电路中的电容C1和C2两个电容对晶振的稳定性有很大影响,每一种晶振都有各自的特性,所以我们必须按晶振生产商所提供的数值选择外部元器件。通常在许可范围内,C1,C2值越低越好,C值偏大虽有利于振荡器的稳定,但将会增加起振时间。一般情况下我们使得C2值大于C1值,这样可使得上电时加快晶振起振。

3、单片机晶振被过分驱动引起的问题,晶振被过分驱动会渐渐损耗晶振的接触电镀从而引起晶振频率的上升。我们可用一台示波器来检测,OSC,输出脚,如果检测一非常清晰的正弦波且正弦波的上限值和下限值都符合时钟输入需要,则晶振未被过分驱动,相反,如果正弦波形的波峰,波谷两端被削平,而使波形成为方形,则晶振被过分驱动,这时就需要用电阻RS来防止晶振被过分驱动,判断电阻RS值大小的最简单的方法就是串联一个5k或10k的微调电阻,从0开始慢慢调高,一直到正弦波不再被削平为止,通过此办法就可以找到最接近的电阻RS值。

4、画PCB的时候,要求晶振离它的放大电路(IC管脚)越近越好。这是由于晶振的输出能力有限,它仅仅输出以毫瓦为单位的电能量。在IC(集成电路)内部,通过放大器将这个信号放大几百倍甚至上千倍才能正常使用。晶振和IC间一般是通过铜走线相连的,这根走线可以看成一段电容或数段导线,导线在切割磁力线的时候会产生电流,导线越长,产生的电流越强。

晶振就好比是单片机的心脏,晶振为单片机提供基本的时钟信号,通常一个系统内都是共用一个晶振,一但晶振失常,那单片机也就不能正常工作。如果你发现单片机无法正常工作,那有很大部分原因是晶振造成的。

-

晶振

+关注

关注

34文章

3066浏览量

68902

发布评论请先 登录

相关推荐

STM32H743VGT6外部晶振不起振是什么原因?如何解决?

使用ADS1255的时候晶振不起振怎么解决?

开关电源不起振有几种原因

测量晶振要注意,探头也有讲究,不然会导致晶振不起振!

晶振不起振的原因

晶振不起振的原因

评论