今年3月,Allegro 和 Sigrity 软件最新发布了一系列的产品更新(SPB17.4 QIR4 release)。接下来,我们将陆续介绍各个产品更新亮点。通过实例讲解、视频演示让您深入了解AllegroPCB Editor、AllegroSystem Capture、AllegroPackage Designer Plus、SigrityAurora、Sigrity SystemSI、Sigrity SystemPI等产品的新功能及用法,助力您提升设计质量和设计效率。

Allegro

PCB Editor

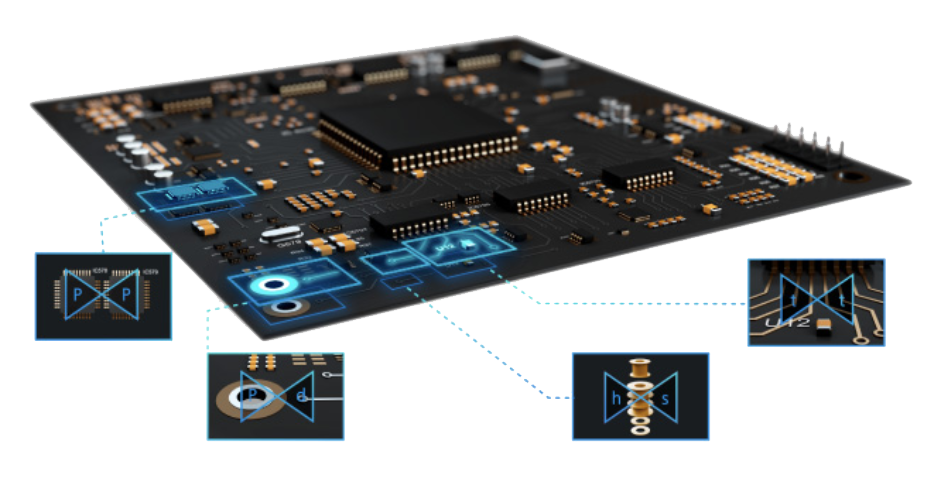

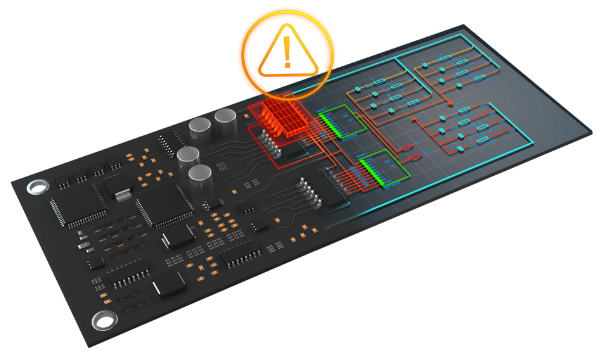

PCB 设计亮点

动态背钻:背钻信息跟随设计,实时更新。设计调整后,无需手动更新背钻信息。

微孔检查:设定激光孔相关的设计规则,确保HDI设计高质量交付。

参数化高速结构:

无需繁琐选择高速结构要素,输入参数即可生成所需高速结构;

在设计中,像使用过孔一样使用高速结构(替换、在Constraint Manager中设定)。

3D Canvas:让设计者看到PCB实体,眼前展示的是组装完成的PCB。

DFM/DFA设计:不同区域设置不同的DFM/DFA规则。

Allegro Constraint Compiler:将设计指南转换为设计规则,实现规则同源,帮助设计者快速准确复用规则。

●●●●●●●

Allegro

System Capture

原理图

设计亮点

Symbol 设计更高效:实现跨section的操作;支持文档类symbol、异构部件创建。

原理图设计性能:同一层次下的Block顺序可调;不同section之间Pin顺序可调。

设计完整性检查:基于设计规则,可Waive DRC;用户自定义类别和规则;可增加DRC注释。

设计流程更畅通:Block内变量重用;关联Block和变量,以利于Block更新;可生成层次BOM。

PSpice集成:PSpice 仿真模拟设计;运行 PSpice 高级分析以优化电路,估算良率。

AWR-RF集成:用Allegro库设计MWO的射频电路;直接用供应商提供的部件进行设计;RFIP无缝导入PCB制造库。

●●●●●●●

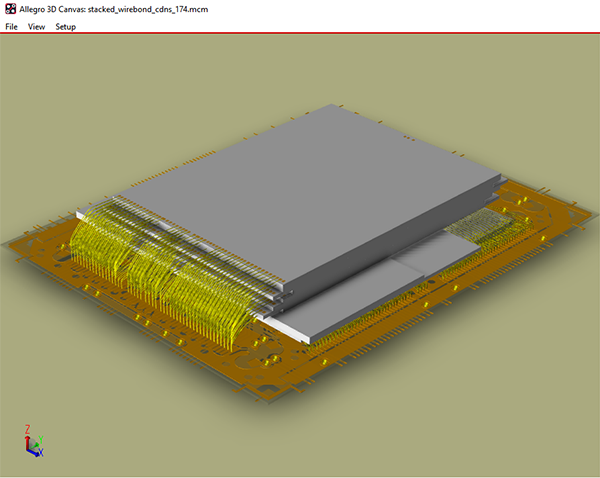

AllegroPackage

Designer Plus

封装 设计亮点

焊盘编辑更灵活:多孔焊盘创建、焊盘隔离设置等功能,帮助用户更高效地建立想要的焊盘形式。

实时DFM:Package to Package区域规则,同名网络过孔检查,更详细DFM规则设置保证设计满足制造要求。

参数化高速结构:高速差分结构参数化创建,全新自动化框选替换操作,提升设计效率。

硅基供电网络参数化设计:针对硅基设计,参数化创建IC风格电源网络、过孔阵列以及电源平面,保证供电和接地充足。

●●●●●●●

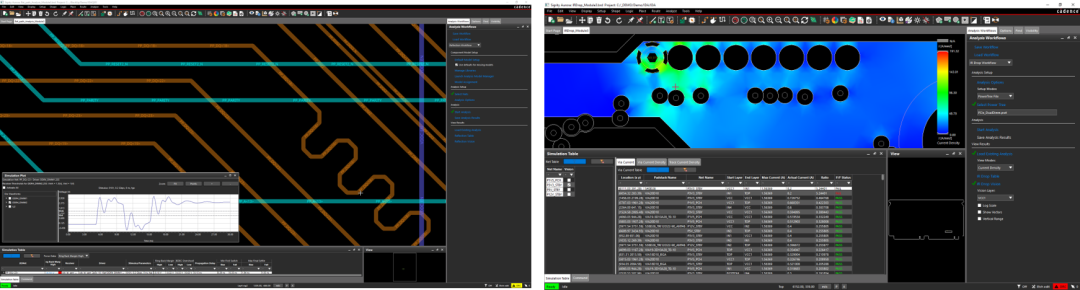

Sigrity

Aurora

互连建模 仿真亮点

支持对未布线网络的拓扑提取及建模:支持布线前按照预拉线曼哈顿长度拓扑提取,并进行信号互连搭建,进行信号完整性仿真分析。

支持Clarity3D Solver和Sigrity PowerSI引擎直接集成:在Aurora环境中,可以通过选择需要提取的网络调用Clarity 3D Solver和Sigrity PowerSI引擎进行S参数的仿真建模。

IR Drop直流电压降仿真支持自动剪切功能:自动剪切功能,可以加快仿真的速度,针对大型PCB的区域分析及部分电路仿真提升仿真的速度。

新增生成同轴电缆和双绞线电缆的模型:生成同轴电缆和双绞线建模,支持框架及参数建模和自定义参数建模的办法,通过修改编辑支持直接进行信号互连拓扑及信号互连仿真。

●●●●●●●

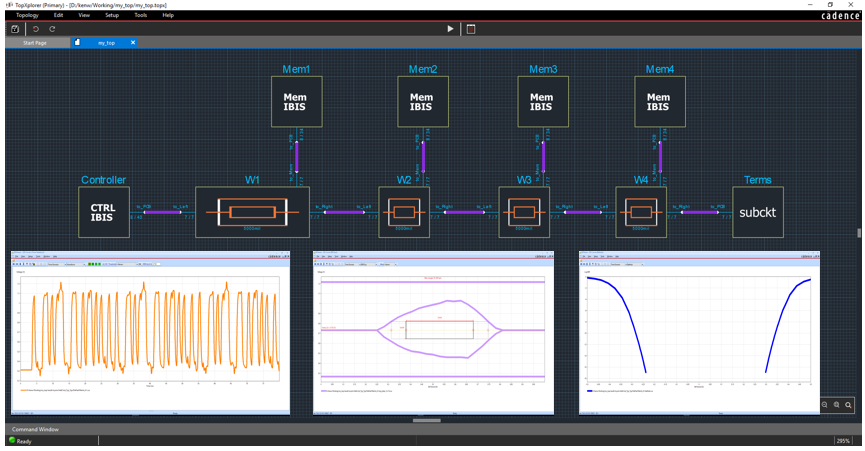

Sigrity

SystemSI

系统信号 仿真亮点

新增支持MIPI-C PHY仿真及标准合规包检查:支持MIPI-C仿真与合规检查分析,支持信号链路拓扑互连及仿真,能自动生成合规性分析报告,眼图和误码率,抖动结果。

新增支持GDDR6 接口及JEDEC协议自动化分析:能够在仿真接口中直接调用GDDR6的接口标准,进行仿真结果的合规性分析检查,并支持按照JEDEC协议自动化分析来输出合规性的检查分析报告。

●●●●●●●

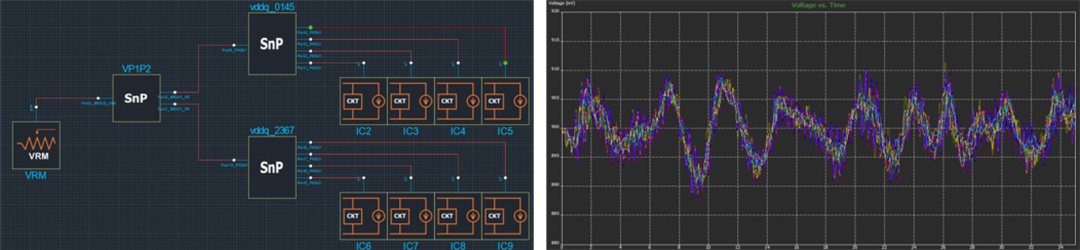

Sigrity

SystemPI

系统电源 仿真亮点

加强支持假设分析:允许在Sigrity OptimizePIdecap库中自动寻找合适的元件进行扫描分析,以求出最佳的结果,支持时域和频域的范围内扫描结果优化

加强PWL生成功能:支持增强功能,低通,高通,带通,带阻滤波器,增加了随机扫描的噪声,允许设置波形的时间及时间步长和停止时间。

-

allegro

+关注

关注

42文章

658浏览量

145295

发布评论请先 登录

相关推荐

实时网络的仿真和配置工具RTaW Pegase v4.6版本更新

Allegro X 23.11 版本更新 I PCB 设计:一键移除评审内容 &amp; 导入ODB++

Allegro X 23.11 版本更新 I PCB 设计:梯形布线的分析性能提升

【2K0300先锋板】【v1.0.241021版本】BSP 更新,欢迎更新使用

Allegro X 23.11 版本更新 I PCB 设计:与器件关联的动态禁布区

Allegro X 23.11 版本更新 I PCB 设计:图纸打印和时序调整

Allegro X 23.11 版本更新 I PCB 设计:DFA_BOUND 用于 DFA 规则设定

求助,如何更新esp-iot-solution中lvgl库的版本?

Allegro X 23.11 版本更新 I 原理图设计:变体及 function 的创建与管理

求助,通过VScode构建的集成开发环境如何更新环境下的ESP-IDF版本?

chrome插件新版本(v3版本)中的热更新,即加载更新远程js的方法探索

Allegro X 23.11 版本更新 - 亮点概要

2024 Allegro X 23.1.1 版本更新——亮点概要

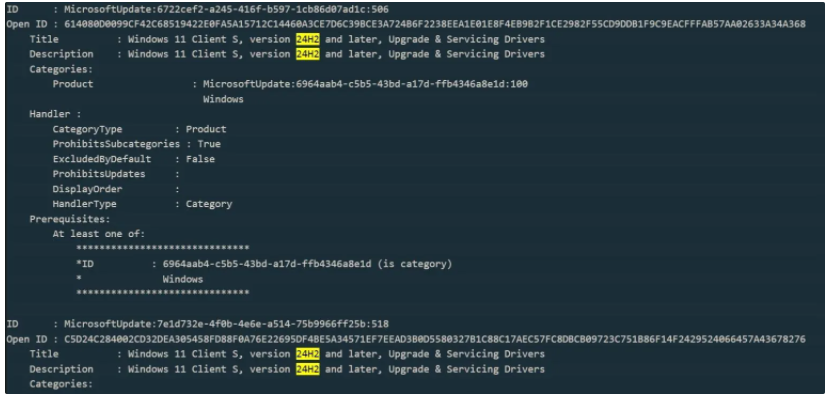

微软24H2版本已进入测试阶段,近期将发布候选版本更新

ANToolsProV3.0全新大版本更新内测介绍

版本更新 | 2022 Allegro SPB 17.4 版本更新——亮点概要

版本更新 | 2022 Allegro SPB 17.4 版本更新——亮点概要

评论