仿真和验证是开发任何高质量的基于 FPGA 的 RTL 编码过程的基础。在上一篇文章中,我们介绍了面向实体/块的仿真,即通过在每个输入信号上生成激励并验证 RTL 代码行为是否符合预期,对构成每个 IP 核的不同模块进行实体/块的仿真。

前文回顾

如何测试与验证复杂的FPGA设计(1)——面向实体或块的仿真

在本篇文章中,我们将介绍如何在虹科IP核中执行面向全局的仿真,而这也是测试与验证复杂FPGA设计的第二个关键步骤。

面向全局的仿真

全局仿真意味着验证整个IP实体的正确行为,包括构成产品的每个子模块。为了适应不同客户的用例,虹科SoC-e IP核解决方案在设计时充分考虑了灵活性,这意味着虹科所有的IP核都是高度可配置的,无论是在集成时(以优化 FPGA 中的封装)还是在运行时。借助于有着不同接口选项的寄存器映射(在下面的示例中,使用 AXI4),运行时配置成为可能。

这种灵活性也对仿真过程提出了挑战,因为需要根据仿真环境中的不同测试用例来配置IP。对此,虹科的合作伙伴SoC-e团队开发了一个令人惊叹的智能测试平台环境,在该环境中可以进行实时配置并实现自动化,开发人员可以通过“点击即用”的方式来执行复杂的仿真。例如,测试台可以通过交换机发送以太网帧,并可以通过访问IP 核的统计寄存器来读取结果(并检查输出是否符合预期)。

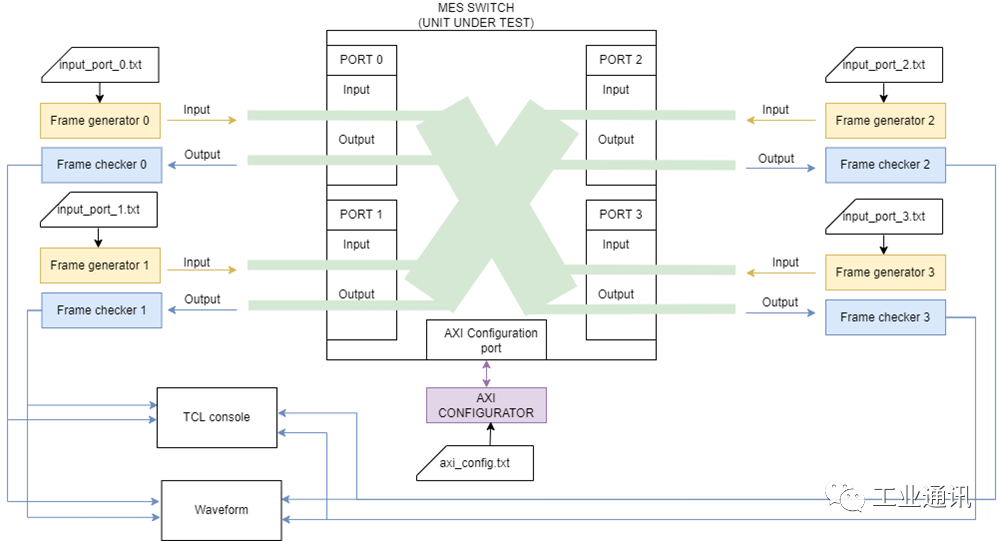

这极大地加快了调试过程,并允许开发团队执行快速迭代,而这在基于硬件的测试环境中会慢得多。在下图为具有此类全局测试平台架构的框图(基于虹科网管以太网交换机IP核):

网管型以太网交换机 (MES) 表示为UUT。其余的测试台组件是符合整个环境的不可综合的 VHDL 模块:

Frame Generator::该模块连接到以太网交换机 IP 的入口端口,负责生成激励(以太网帧)。

Frame Checker:该模块连接到以太网交换机IP的出端口,负责分析交换机转发的流量。

AXI Configurator:它控制 AXI4 配置总线以修改配置寄存器的内容(读/写操作)。

测试平台执行流程

正常的测试平台执行流程如下:首先,AXIConfigurator模块根据测试用例配置IP核。之后,每个FrameGenerator都会生成测试帧,并将其发送到启用的入口端口。帧是通过循环重复某些特定测试文件中定义的内容来生成的。最后,Frame Checker接收帧(接收与否,取决于测试用例)。该块将检查每个端口对应的统计信息,并根据执行的测试用例确定输出是否符合预期的。

虹科SoC-e测试平台架构的一大亮点是Frame Checker可以自动检测多种错误,例如完整性错误、转发错误或帧丢失。这是可实现的,因为Frame Generator可以生成具有特定格式的流量(例如有效载荷中的特殊模式、序列号等),Frame Checker可以解释这些流量。

测试平台测试计划

该测试平台套件的惊人灵活性还与SoC-e定义的严格测试计划相结合。对于每个IP核,都有一个测试计划,旨在在仿真环境中测试尽可能多的特性。

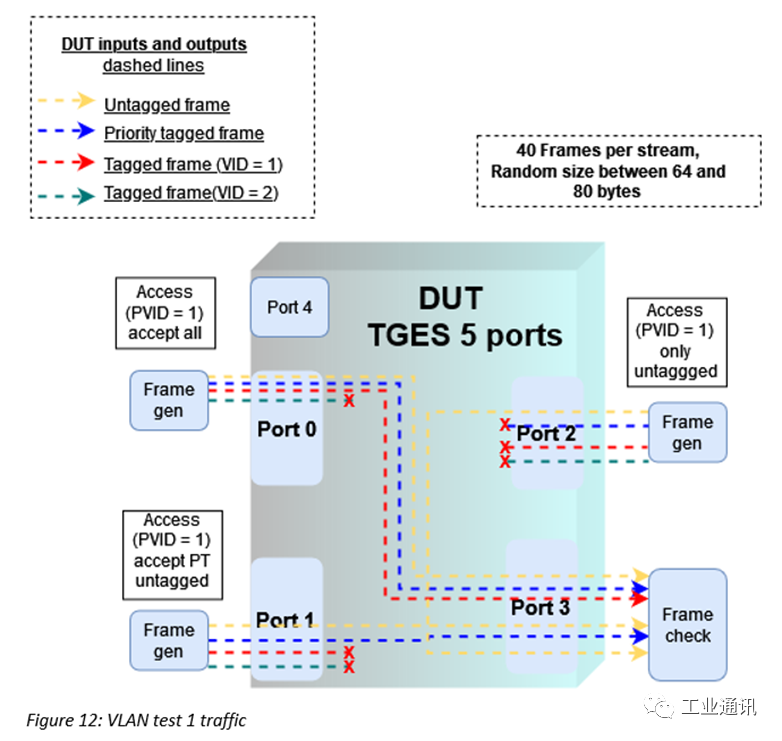

例如,网管以太网交换机IP的测试计划可以被划分为五个主要部分:

通用交换

自定义转发

过滤数据库

优先队列

这些部分旨在涵盖与网络相关的不同功能的行为,以及不同的流量模式和情况。

测试平台的结果可以由开发人员或用户以不同的方式进行分析。TCL控制台用于快速反馈测试结果。然而,在某些情况下,在仿真的特定时刻深入了解特定信号值可能会很有趣。对于这种情况,还开发了预先格式化的波形,以便于查找特定信号。

用于测试执行的命令行界面(CLI)

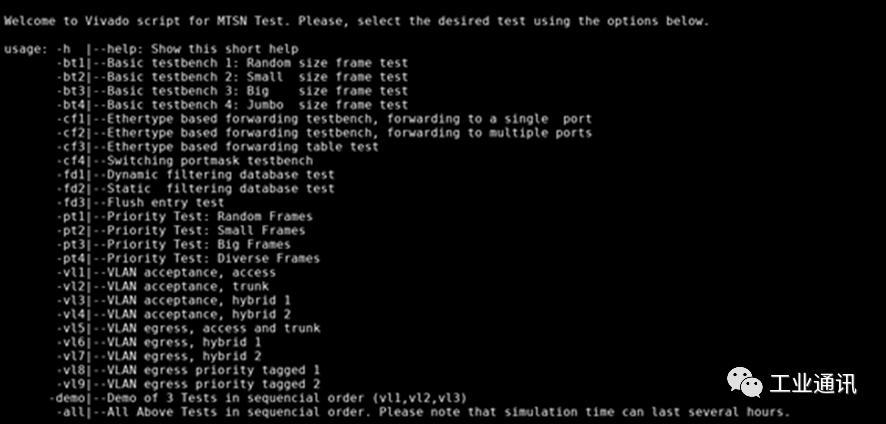

此测试平台环境中包含的最新功能之一是可以直接从命令行界面(CLI)执行所有测试,而无需打开RTL仿真工具(Vivado或其他工具)。这是一个很大的改进,因为它可以实现更高的测试自动化。它基于使用Vivado编译器命令的脚本(Python)的使用,以便用户生成易于解释的结果。

下图显示了向用户显示的仿真菜单。用户只需选择相应的选项即可执行任何列出的测试:

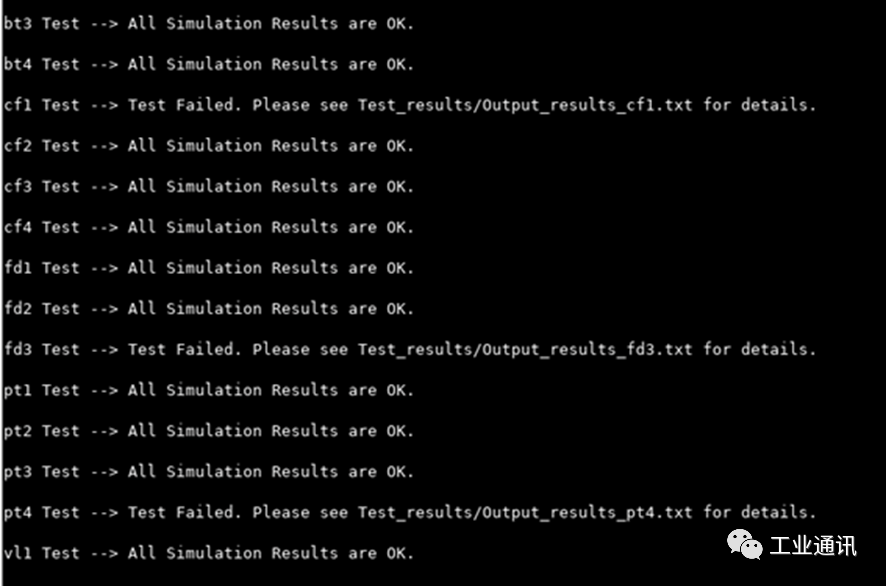

众所周知,仿真是一个需要大量时间的过程。即使在功能强大的计算机中执行,毫秒或以上范围内的复杂仿真也需要持续数十分钟,甚至更长。为了简化执行所有测试的过程(这需要几个小时),我们实现了一个“-all”选项,它允许在管道中执行所有测试,且无需用户交互。完成所有测试后,它将提供有关每个测试的报告消息(如下图所示),并在测试失败的情况下生成输出文件,以便开发人员稍后进行分析。

-

仿真

+关注

关注

50文章

4070浏览量

133542 -

IP核

+关注

关注

4文章

327浏览量

49484

发布评论请先 登录

相关推荐

虹科技术前沿 TSN网络中时间感知整形器的性能验证实测

测试与验证复杂的FPGA设计(2)——如何在虹科的IP核中执行面向全局的仿真

测试与验证复杂的FPGA设计(2)——如何在虹科的IP核中执行面向全局的仿真

评论