静电放电保护器件种类与特点

概述

静电放电(ESD)是一种意外的快速高压瞬态波形,出现在电路内的导体上。ESD引起的高电压和电流峰值可能导致静电敏感IC等器件发生故障。人际接触是ESD的常见来源。即使人与电路没有直接接触,电容式检测开关等器件也可以允许电荷耦合到电导体上。在ESD放电可能导致电路故障的情况下,需要ESD保护。

电磁干扰(EMI):电磁辐射的存在,可能会破坏附近的系统。EMI的来源包括电风暴(闪电),主电源线中断,太阳辐射和附近的电路(电源,变速电机驱动器,电弧焊机等)。

在电磁辐射 (EMI) 下正常工作。

不会发出超过系统类型及其使用环境所定义的法规的EMI。

静电保护器件种类

下表总结了可用于 ESD 保护的不同组件。大致按从最低功率到最高功率分量排序。

优势:便宜、小

缺点:对高功率ESD事件无效

对高电压|敏感适用于帮助降低由小 ESD 事件引起的电压尖峰

优势:非常严格控制的“接通”电压

缺点:对高功率ESD事件无效

齐纳二极管是雪崩二极管的一种形式,就像TVS一样。主要区别在于,齐纳二极管通常设计用于更清晰的导通特性(用于电压调节目的),而功耗则更小。

TVS瞬态电压抑制二极管

优势:导通时间快(特别是单向,双向较慢)

可处理中等功率 ESD 事件

缺点:不适合作为单个元件来有效应对高功率ESD事件(需要与MOV,火花间隙或GDT配对)。

MOV(金属氧化物压敏电阻)

优势:通流量大

缺点:累积退化

大漏电流

大电容 (10−1000pF10−1000pF)

气体放电管

优势:可熄灭极高功率 ESD 事件(例如雷击)

缺点:比TVS二极管更笨重、更昂贵

不要具有低而尖锐的导通电压,因此通常与TVS二极管结合使用。

累积降级为高功率事件

GAP火花间隙

火花间隙非常简单(只是PCB层上的铜形状!工作原理与GDT相同,但没有受控的气氛和压力。

标准

IEC-61312-1:雷电电磁脉冲保护,于1995年首次推出。

Telecordia GR-1089核心:电磁兼容性和电气安全 - 网络电信设备的通用标准:电信服务提供商使用。它包含 NEBS(网络设备 - 建筑系统)标准。

IEC 61643-1,第一版,1998年,连接到低压配电系统的浪涌保护器件。最早引用8/20us雷电波形之一。

IEEE C62.41.2,关于低压(1000 V及以下)交流电源电路中浪涌电压特性化的推荐做法。

符合 IEC 61000-4系列标准

IEC 61000-4 完全是关于电磁兼容性 (EMC) 的。

符合 IEC 61000-4-2 标准

例如,上海雷卯 ULC0511CDN ESD 二极管阵列的 ESD 耐压 VESD 的额定值为 ±30kV(符合 IEC61000-4-2(接触),±30kV,符合 IEC61000-4-2(空气)标准。

IEC 61000-4-4

特别令人感兴趣的是第4部分(61000-4-4),标题为“测试和测量技术 - 电气快速瞬变/突发抗扰度测试”。它详细介绍了如何在电路上构建测试以测量其对ESD的敏感性,重点是来自源的ESD,例如感性负载的中断和继电器触点反弹。第一版于1995年发布。截至2022年,2012年版本是最新的。

IEC 61000-4-4 定义了一些测试级别,以及端口必须能够承受的相关峰值电压。“电源端口”和“信号端口”之间是有区别的。

测试级别 | 峰值电压 - 电源端口 | 峰值电压 - 信号端口 |

| 1 | 0.5千伏 | 0.25千伏 |

| 2 | 1千伏 | 0.5千伏 |

| 3 | 2千伏 | 1千伏 |

| 4 | 4千伏 | 2千伏 |

| X | 不适用 | 不适用 |

测试级别 X 指定一个特殊测试,其中级别由用户定义。所有级别的“重复频率”均为5或100kHz。

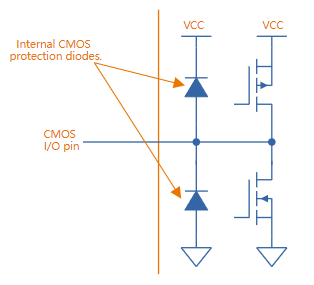

CMOS I/O 上的内部 ESD 保护

内置保护在CMOS I/O引脚上非常常见,这些引脚可能是器件的一部分(从简单的负载开关到中等复杂性的微控制器,再到高复杂性的FPGA)。它们通常为每个 I/O 引脚两个。一个连接在引脚和GND之间,一个连接在引脚和VCC之间。两者在正常工作条件下均为反向偏置(GND<=VI/O<=VCC)。

CMOS数字I/O引脚示意图,突出显示了许多设计中普遍存在的内部保护二极管(即使IC数据手册中没有提到它们)。

它们用于在引脚发生故障时保护敏感的CMOS逻辑。如果VI/O 上的电压高于 VCC(例如,正 ESD 电压尖峰),则顶部二极管导通,将引脚上的电压箝位至不超过VCC+Vf。同样,如果VI/O上的电压降至VGND以下(例如,负ESD电压尖峰),则底部二极管导通,将引脚上的电压箝位至不超过−Vf。

要小心,因为这些二极管通常具有相当低的最大电流。超过此最大电流将吹动ESD二极管,通常导致其开路,从而消除了敏感CMOS电路的保护,然后几乎瞬间被油炸。然后,您的 I/O 引脚将停止工作。如果幸运的话,它只会是一个受影响的引脚。如果没有,整个端口(如果适用),甚至整个设备都会被失效。

无论它们多么有用,它们也会在特定情况下产生设计挑战,因此在进行任何涉及CMOS I/O且存在ESD保护二极管的原理图设计时,都需要仔细考虑。导致问题的两种情况是:为具有多个电压轨的电路上电时。当VI/O上的电压在某些点上可能高于VCC时,由于输入信号的性质。在低功耗设计中,当您有选择地关断为这些IC供电的电压轨时。

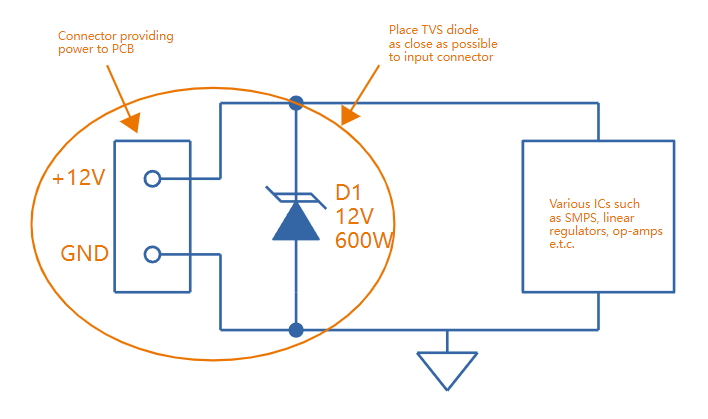

单通道普通 TVS 二极管

养成一个好习惯 - 将TVS二极管放置在PCB的输入/输出两端(而不仅仅是电源轨,尽管这是本原理图中所示的)。将TVS尽可能靠近PCB的入口位置放置。

如上所示的TVS还可以防止反极性。在这种情况下,TVS将正向导通并将电压箝位至约−0.7V。确保这会熔断保险丝,或者TVS足够大,可以无限期地维持功耗。

在+12V电源上同时使用保险丝和TVS到PCB。在这种情况下,保险丝放置在TVS二极管之前,因此如果+12V以错误的方式连接(电流通过F1和D1),保险丝也会熔断,此处F1采用leiditech的PPTC系列产品。

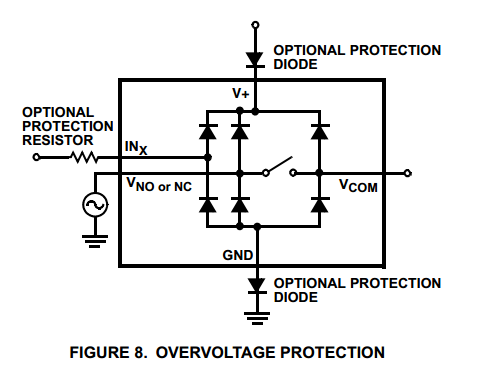

TVS阵列 ESD 二极管

可以添加IC外部的额外二极管,以防止通过具有VCC和GND的ESD保护二极管的器件上的CMOS IO引脚泄漏电流。下图显示了如何将它们连接到受保护的IC。

添加外部ESD二极管。

但是,这种方法有其缺点。IC看到的实际电源电压在二极管上降低两倍的压降(VfVf)(通常为2x 0.5-0.7V = 1.0-1.4V)。此外,IC接地现在与系统接地有很大不同。这可能会干扰单端ADC测量和其他模拟功能。

串联电阻进入 CMOS I/O

最常用的外部ESD保护方法是在ESD能量源和要保护的集成电路引脚之间添加一个小串联电阻。有点违反直觉的是,小至50Ω的电阻可能会使CMOS IC的ESD抗扰度提高一倍。更高的免疫力是可能的;更高的保护水平与增加的串联电阻成正比。此方法的工作原理有两个原因。首先,串联电阻与IC寄生引脚电容(通常为5至10 pF)配合使用,形成截止频率低于1 GHz的单极点低通滤波器。这导致串联电阻衰减大部分 ESD 事件的高频能量(在 HBM 放电中高达 90% 的上升沿功率)。其次,当IC保护电路正常工作时,其阻抗非常低(在几十欧姆或更低的量级)。这种低电阻与串联电阻一起工作,形成分压器,因此ESD事件产生的高电压只能使IC内置保护电路偏置为总ESD电压的一部分。这种衰减是对上升沿滤波的补充。这些影响的总和来自一个简单的外部串联电阻,在要求苛刻的应用中显著提高了ESD性能。

最佳放置

如果要将TVS二极管和串联电阻作为ESD保护添加到CMOS I/O引脚(例如微控制器上的GPIO引脚),则最好先放置串联电阻(更接近ESD事件的源),然后再放置TVS二极管(更靠近微控制器)。

这是允许的,因为电阻不会受到ESD的损坏,并且可以消耗大部分功率,仅留下部分用于TVS二极管,这意味着CMOS I/O引脚上的电压不会像其他方式那样变化。

上拉/下拉问题

串联电阻的一个问题是,当与上拉或下拉电阻配合使用时,它们可能会导致问题。上拉/下拉电阻在CMOS I/O输出上很常见,这些输出具有集电极开路(更常见的选择)或发射极开路配置。问题在于,在特定情况下,ESD/限流串联电阻和上拉/下拉电阻将形成分压器。

检查输入的最大数字低电平和最小数字高电压电平。如果它们仍然得到满足,那么您不必担心。

总结

电子产品的接口防护需用过压保护器件,很多工程师意识到要用保护器件,但由于选型不当或没按照ESD电路PCB设计原则,造成产品静电测试或EMC测试不通过,产品多次验证测试,浪费人力财力,造成产品延迟上市的事情总有发生,或过度设计,造成成本压力。

雷卯电子专业为客户提供电磁兼容EMC的设计服务,提供实验室做摸底测试,从客户高效,控本方便完成设计,希望为更多的客户能快速通过EMC的项目,提高产品可靠性尽力。

雷卯电子电磁兼容实验室,提供免费测试,提供外围静电保护参考电路。

-

保护器

+关注

关注

6文章

1188浏览量

35902

发布评论请先 登录

SGM12UB1D2:超低压电容单通道ESD保护器件解析

SGM18CB1B3:高性能低电容ESD保护器件解析

SGM18UB1E1:18V超低电容单通道ESD保护器件解析

SGM15UB1E2:超低压电容单通道ESD保护器件详解

SGM05FB4D2:高性能四通道ESD保护器件的全面解析

SGM05FB8D2:高性能八通道ESD保护器件的深度剖析

SGM05UB1B3:超低压电容单通道ESD保护器件的深度解析

SGM05FB2E2:高性能ESD保护器件的设计与应用解析

SGM12CB1A5:低电容单通道ESD保护器件解析

深入解析SGM05CB1A7低电容单通道ESD保护器件

SGM05CB1A8:低电容单通道ESD保护器件的全方位解析

SGM05CB1A4:低电容单通道ESD保护器件的技术剖析与应用指南

MMBZxxVCL - Q1 双通道 ESD 保护器件:设计与应用指南

MDD保护器件在应用中的效果及常见问题与解决方案

静电放电保护器件种类与特点

静电放电保护器件种类与特点

评论