每个传统的封装设计师都了解电镀条 (plating bar) 及其作用。为了在制造过程中提供电流,每个网络都连接到 BGA 的边界,以便使电流到达所有需要通电的区域。

电镀条的定义通常是“围绕设计边界的金属连接”,会略微超出 BGA 的最终轮廓。电镀条将所有引脚连接在一起,当 BGA 与相邻的器件分离后,就会移除电镀条。不会留下任何互连的网络——除非使用蚀刻工艺,去除 BGA 轮廓内部网络之间的短路;这将是一个额外制程步骤。

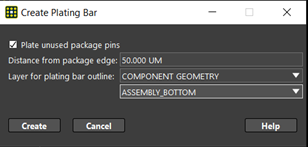

在Cadence Allegro Package Designer Plus工具中,电镀条由两部分组成。首先,“电镀条”本身(外面的导体环)从封装边缘外移,实现全部线路连接。然后,在每个网络需要连接到电镀条器件的地方创建引脚。

如果有引脚没有连接到电镀条上,或者如果一个网络在电镀条器件上没有对应的一个或多个引脚,制程将会出现问题。

这是一个相当简单的过程和程序。对于新的设计形式,如硅基板和 system-on-wafer 设计,水平相连(而不是垂直相连)通过焊球离开基板边缘的走线,可能根本就没有与电镀条相连。相反,它们可能在一个更大的模式中连接到另一个相邻的设计器件。

边缘连接器

在这些设计中确定网络的出口(在哪一层、在封装的哪一面,甚至是末端的 X,Y轴位置)至关重要。如果走线的出口与它在下一个设计器件中的配对连接位置不一致,那么整个设计将无法正常运行。

此外,网表中需要有器件到器件的连接,以确保没有遗漏。这也将使接口的映射变得容易管理。电镀条设计方法不适合表现这种类型的立体连接关系。

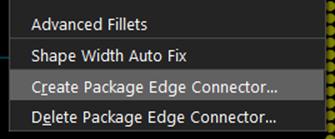

边缘连接器 (Edge Connector) 是 Allegro Package Designer Plus 中的器件对象,用于创建和配置这些接口。它们可以通过 SI Layout 菜单的 (需要 Silicon Layout Option的使用权) Create Package Edge Connector 工具制作,如下图所示:

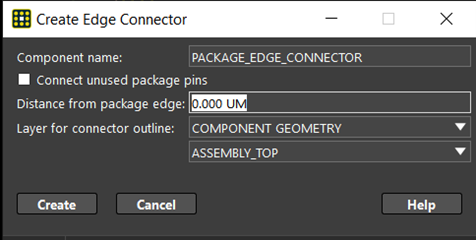

启动后,如果不仔细观察,可能会认为运行的是电镀条创建工具。这是因为创建电镀条和边缘连接器都需要类似的物理几何形状。

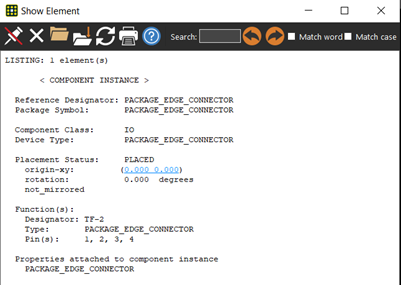

仔细观察会发现两者有一些重要的区别。首先,一定要给器件命名。边缘连接器是一个 IO 类器件,就像 BGA 一样。它为相邻器件而不是下一层基板提供 IO。因此,比起电镀条,参考指示、设备名称和符号名称会更加一目了然。

连接对齐

边缘连接器组件可以提供哪些优势?如果在下一个器件中重复刚使用过的"边缘连接器"界面,那么可以确信器件之间走线是对齐的,因为使用了相同数据库的设定资料。

简单示例

假设我们有一个 10 x 10 器件大型设计中的一个较小的模块,我们希望器件的北侧与相邻单元的南侧完全吻合,东侧和西侧完全吻合。

步骤1:

使用"边缘连接器"工具,对设计的一侧进行布线。在本例中,我们对东测进行布线。布线完成后,生成"边缘连接器"。

步骤2:

使用 symbol edit application 模式,选中东侧的引脚。把它们复制到西侧,用基板的一个角作为参考点,就可以确信相邻接的器件两侧完全对齐。

步骤3:

将正确的网络分配给西侧的连接器引脚。该操作有助于尽早获得关于一些可能发生问题的反馈:

是否需要交换芯片接口的引脚,以便对相关的网络进行布线,同时不需要对"层"做出不必要的更改?

所有的差分对和总线的顺序都很理想吗?

延伸到裸片下 BGA 焊球的网络,而不是延伸到相邻单元的网络,是否应该重新布设,以避开同一层上交叉的走线?

对于所有的网络,相对于顶层网表,网络和网络的连接是否正确?

如果能够回答以上问题,我们就可以确信解决方案是有效的。如果无法回答,可以在设计流程的早期进行最有效的修正。毕竟,返工的代价是我们不愿承担的。

完成最初的接口设计后,如果需要进行任何更改,那么我们需要知道更改对周围器件的影响。只能通过 symbol edit application 模式或 UNFIXED_PINS 属性移动引脚。设计师不希望在无意间移动或删除走线。并且走线的端点是锁定的。

自动布线

布线时,布线工具需要有一个连接起点和终点。

封装"边缘连接器"的引脚提供了这些端点。我们可以运行自动布线工具,任何一个交互式或自动交互式的布线工具均可,或者也可以运行自己编写的脚本来进行布线。如果走线最后可以成功到达边缘连接器的引脚,那么走线就是正确的。

最后,由于知道端点在两个模块中的位置,我们可以计算总延迟、相对延迟等结果。在一个器件中收紧并完成布线时,可以利用这些结果来更新下一个器件中的允许延迟和容差。逐渐添加和平衡器件的相对位置,并调整到最终的理想位置(也许需要在某个器件的东侧进行添加,而在另一个器件的西侧进行添加,以便容纳各种新器件)。

Q

为什么不直接设计一个大型的、扁平化的设计?

如果我们要设计一个 10x10 阵列的模块,为什么不简单地把所有 100 个器件并排放在同一个设计中,然后进行整体布线呢?

不采用该方法的理由有很多,其中几点特别关键:

为了更快地验证变更。因为我们知道每个裸片都是相同的,所以不需要在整个晶圆图上运行检查。只需运行一个实例,就可以知道已经找到了95% 或更多的违反设计规则的情况。

如果在一个实例中出现了违反设计规则的情况,那么在该实例中进行纠正,便可以纠正所有 100 个单元。因此,只需要修正一次。

如果设计的下一次迭代需要一个 20x20 的阵列,那么我们对此不需要做任何额外工作,只要在现有的实例中定义一个更大的矩阵即可。

设计中要关注的项目减少了,在工程变更(ECO) 上要刷新的实例也减少了,工作效率大大提高

-

连接器

+关注

关注

98文章

14488浏览量

136449

发布评论请先 登录

相关推荐

矩形连接器的生产过程

在连接器电镀加工中镀金含量是多少?

医疗设备的六种常见连接器类型

精密电子连接器电镀加工中pogo pin零部件的电镀要点

4000m²的电镀车间 保障连接器厂商的电镀需求

技术资讯 I 电镀条与边缘连接器

技术资讯 I 电镀条与边缘连接器

评论