Allegro和 Sigrity 软件最新发布了一系列的产品更新(SPB17.4 QIR4 release)。我们将通过实例讲解、视频演示让您深入了解 Allegro PCB Editor、Allegro System Capture、Allegro Package Designer Plus(本期内容)、Sigrity Aurora(本期内容)、Sigrity SystemSI、Sigrity SystemPI等产品的新功能及用法,助力提升设计质量和设计效率。

Cadence Sigrity Aurora 为 PCB 设计前、设计中和布局后提供传统的信号和电源完整性 (SI/PI) 分析,结合 Cadence Allegro PCB 编辑和布线技术,Sigrity Aurora用户在设计初期就可以使用 “What-if” 探索环境进行分析,从而获得更准确的设计约束并减少设计迭代。

Sigrity Aurora 直接读写 Allegro PCB 数据库,可快速准确地整合设计和分析结果。它提供了一个基于 SPICE 仿真器和获得专利的 Sigrity 嵌入式混合场求解器,用于二维和三维结构提取。同时支持兼顾电源影响(Power-Aware)的 IBIS 模型,如需要还支持晶体管级别的模型。高速信号可以在布局阶段中或布局阶段后,对比备选方案进行研究,以便对所有相关信号进行全面分析。

在最新的 SPB 17.4 版本中,Cadence Sigrity Aurora 主要在以下几个方面对互连建模的仿真功能进行了更新:

支持对未布线网络的拓扑提取及建模:支持布线前按照预拉线曼哈顿长度拓扑提取,并进行信号互连搭建,进行信号完整性仿真分析。

支持 Clarity 3D Solver 和 Sigrity PowerSI 引擎直接集成:在 Aurora 环境中,可以通过选择需要提取的网络调用 Clarity3D Solver 和 Sigrity PowerSI 引擎进行 S参数 的仿真建模。

IR Drop 直流电压降仿真支持自动剪切功能:自动剪切功能,可以加快仿真的速度,针对大型 PCB 的区域分析及部分电路仿真提升仿真的速度。

新增生成同轴电缆和双绞线电缆的模型:生成同轴电缆和双绞线建模,支持框架及及参数建模和自定义参数建模的办法,通过修改编辑支持直接进行信号互连拓扑及信号互连仿真。

Sigrity Aurora

互连建模仿真亮点——

#1 对未布线网络的拓扑提取及建模

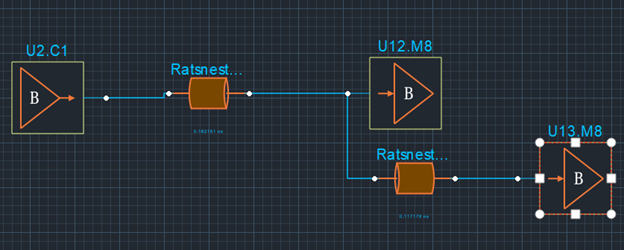

Aurora_TopWbench_SPB17.4 更新之后,Aurora 可支持直接读取 Allegro PCB 数据库,支持对未布线网络的拓扑提取及建模,支持布线阶段前对信号互连拓扑及信号互连链路进行布线提取,并进行信号互连仿真。

接下来我们使用一个实例文件来讲解未布线网络的拓扑提取及建模的办法。

1►

实例讲解 · 视频版

建议在WIFI环境下观看,并注意调整音量

2►

实例讲解 · 图文版

1

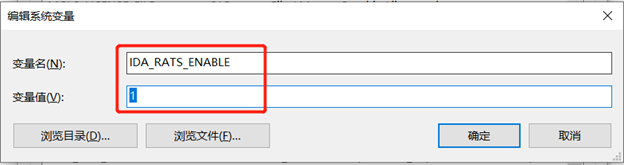

使用未布线网络的拓扑提取及建模功能,首先需要设置系统环境变量 IDA_RATS_ENABLE。

2

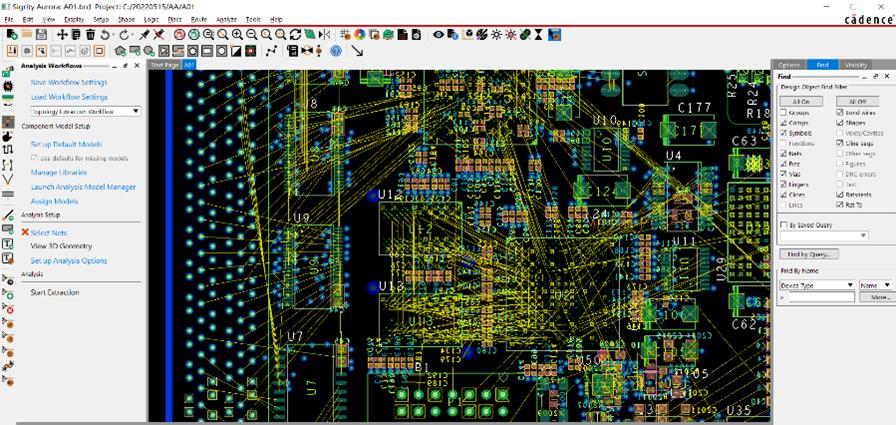

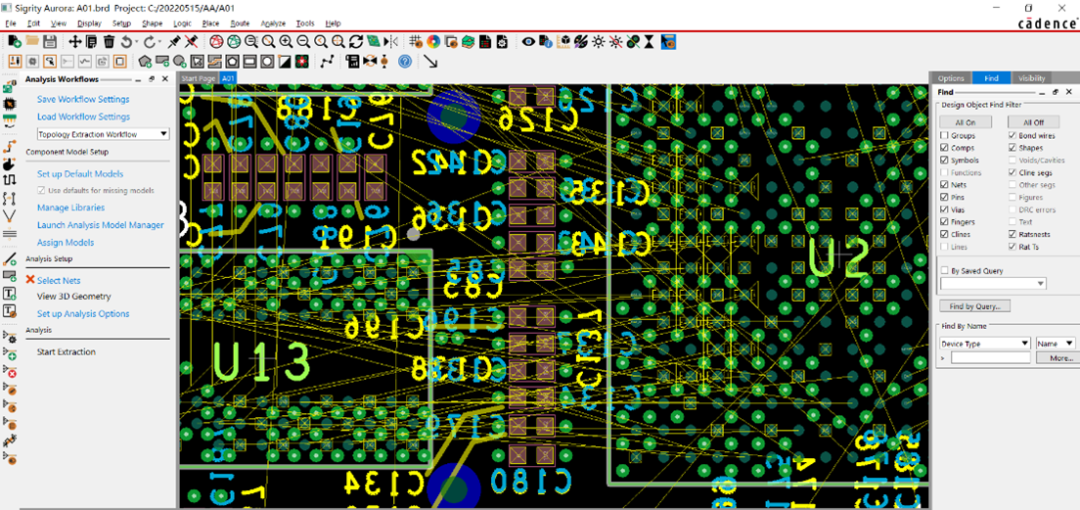

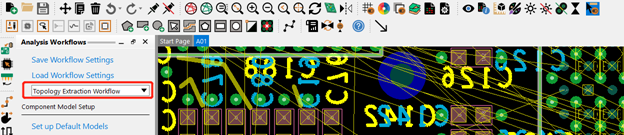

在 Analysis Workflows 流程中选择 Topology Extraction Workflows 拓扑提取流,进入信号互连拓扑流程。

3

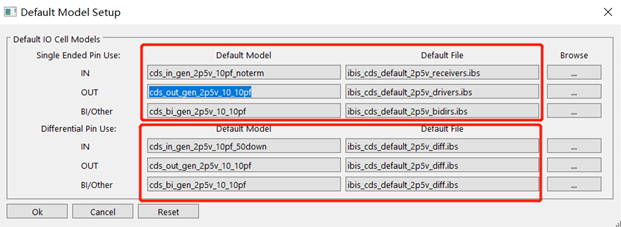

Component Model Setup 用来设置元件模型的参数配置, Set up Default Models 用来配置默认的元件模型, Single Ended Pin Use 设置单端口网络引脚设置, IN 输入引脚模式设置,OUT 输出模型设置, BI/Other 桥接其他模型设置。Differential Pin Use 设置差分端口网络引脚设置,允许浏览 IBIS 文件修改输入、输出、桥接的 GPIO 引脚模型。

4

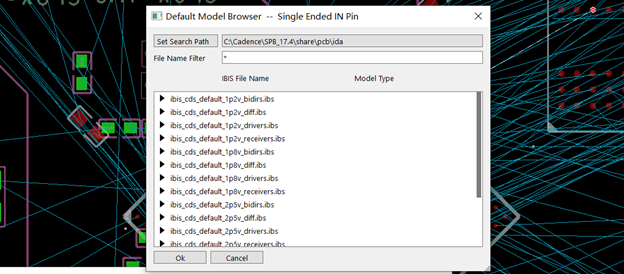

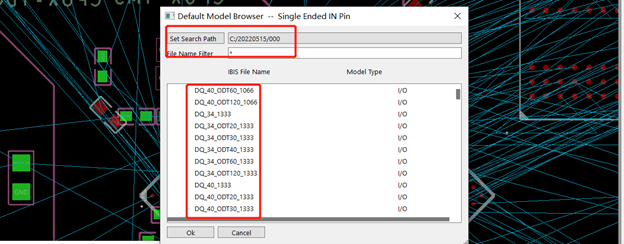

支持修改模型,点击 Browse 浏览默认的模型文件,点击 Set Search Path 支持设置 IBIS 路径,允许在修改后的 IBIS 路径下查找新的 IBIS 文件进行模型的配置。

5

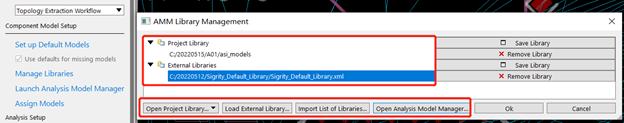

Manage Libraries 用来配置模型库,允许支持对本地项目库的设置和编辑管理,也允许调用 AMM 外部系统库。能导入 AMM 外部库、导入库的清单、打开和管理分析库文件等。

6

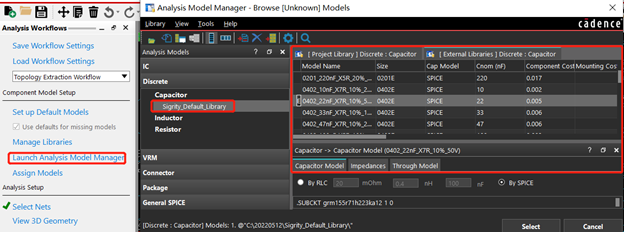

Launch Analysis Model Manager 用来启动元件的模型管理器,在模型管理器窗口中,能够对项目库和外部的库文件进行查阅、编辑、删除、修改等管理。并且可以分析模型库中元件的参数,包括电容、电阻、电感、VRM、连接器、封装、SPICE 模型等。

7

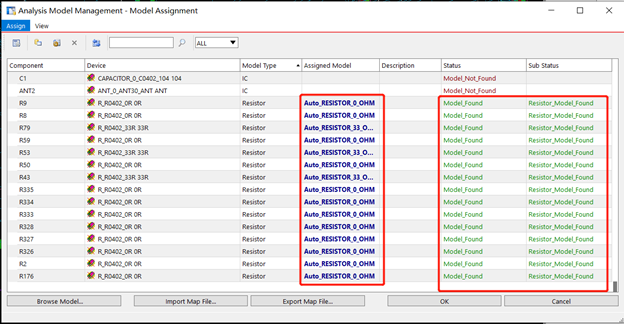

Asign Models 用来给元件添加赋予模型,在Analysis Model Management 窗口中可以查看。允许对元件自动生成赋予生成模型,也支持手动进行模型配置。允许从 AMM 文件元件的模型管理器选中模型,也允许调用 IBIS 模型文件进行模型的设置和赋予设置。

8

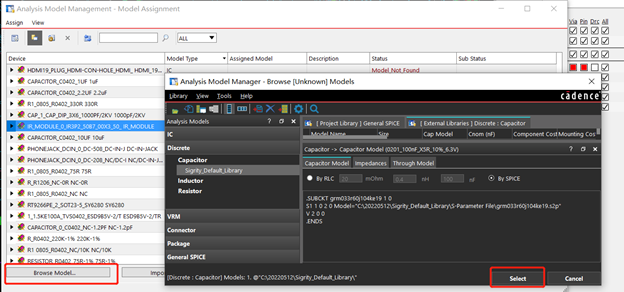

选中需要添加模型的元件,然后选择 Browse Model 按钮在元件的模型管理器中选取模型文件和模型参数的设置。

9

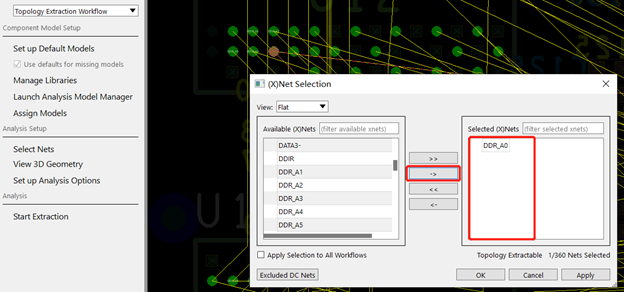

Select Nets 选取需要进行分析的网络,在 Net Selection 中选择需要分析的网络,点击右侧图标按钮可以选中需要分析的网络,支持单网络和差分网络的提取分析。若分析网络中存在直流电源网络或者 GND 网络可以点击 Excluded DC Nets 按钮进行 DC 直流网络的设置和分配。

10

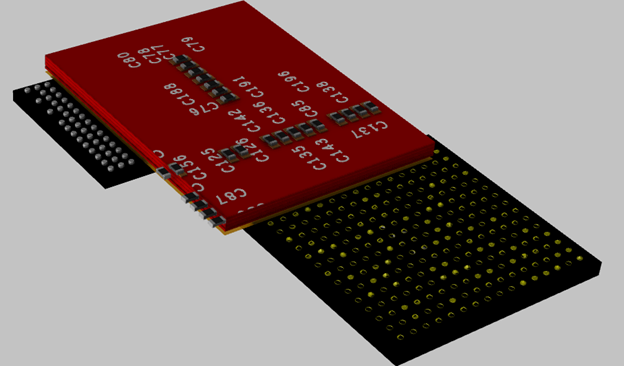

View 3D Geometry 用来预览显示选中分析网络的互连通路,可以查看分析网络的所在层及网络通道的属性显示结果。

11

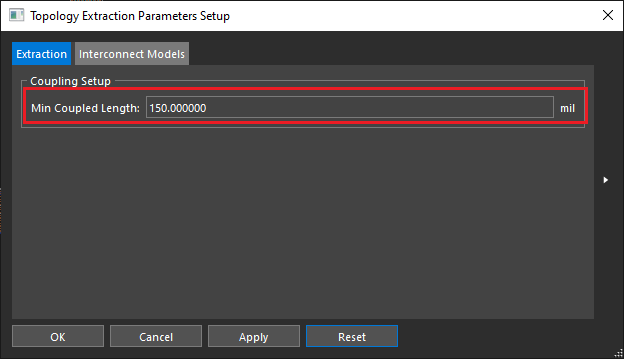

Set up Analysis Options 用来设置网络拓扑提取的参数, Min Coupled Length 用来设置布线耦合,最小长度默认的参数为 150mil。

12

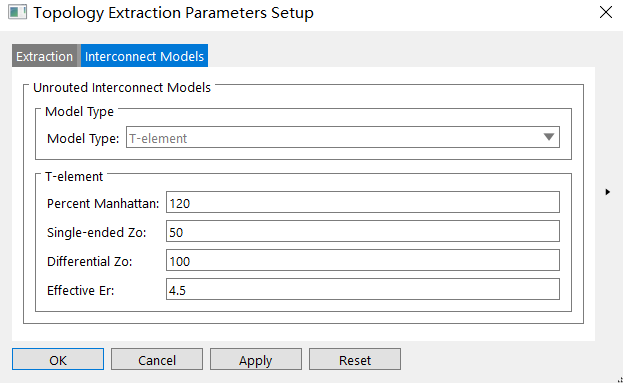

选择 Interconnect Models 设置未布线的传输线模型,默认采用 T-element 模型数据。Percent Manhattan 设置未布线拓扑预拉线的曼哈顿百分比,数据默认为120%,Sigle-ended Z0 设置单线阻抗数据,Differential Z0,设置差分模式的阻抗数据,Effective Er 设置介电常数。

13

点击 Start Extraction 命令,即可按照设置好的参数来提取互连的信号拓扑结构。

14

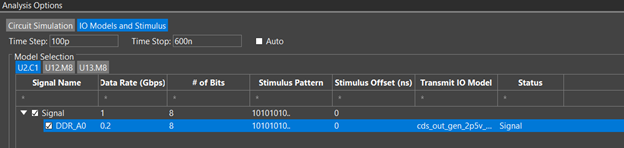

设置激励波形的时间及波形的数据参数。

15

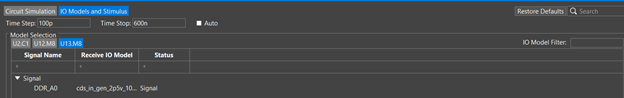

设置信号发送的和接收的模型参数。

16

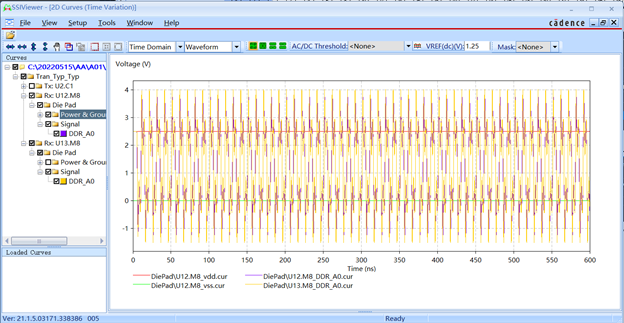

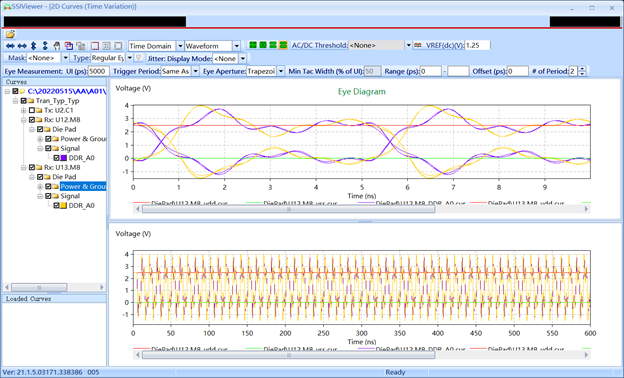

执行仿真以后,就可以看到基于当前的未布线网络拓扑提取到的波形数据结果。

-

网络

+关注

关注

14文章

7561浏览量

88752

发布评论请先 登录

相关推荐

Cadence Allegro 17.4PCB阻抗分析功能操作说

Allegro X 23.11 版本更新 I PCB 设计:梯形布线的分析性能提升

【2K0300先锋板】【v1.0.241021版本】BSP 更新,欢迎更新使用

Allegro X 23.11 版本更新 I PCB 设计:与器件关联的动态禁布区

Allegro X 23.11 版本更新 I PCB 设计:图纸打印和时序调整

请问mesh网络中拓扑结构是如何管理的?

Allegro X 23.11 版本更新 I PCB 设计:DFA_BOUND 用于 DFA 规则设定

苹果Safari 17.4更新提速60%,提升网络体验

【技术课堂】拓扑篇丨LC串联谐振拓扑仿真建模及控制策略分析

利用Sigrity Aurora进行PCB布线后的仿真分析-阻抗及寄生参数析

2022 Sigrity Aurora SPB 17.4 版本更新 I 对未布线网络的拓扑提取及建模

2022 Sigrity Aurora SPB 17.4 版本更新 I 对未布线网络的拓扑提取及建模

评论