Allegro和 Sigrity 软件最新发布了一系列的产品更新(SPB17.4 QIR4 release)。我们将通过实例讲解、视频演示让您深入了解 Allegro PCB Editor、Allegro System Capture、Allegro Package Designer Plus(本期内容)、Sigrity Aurora、Sigrity SystemSI(本期内容)、Sigrity SystemPI等产品的新功能及用法,助力提升设计质量和设计效率。

Cadence Sigrity SystemSI 的模块化设计允许用户方便地搭建任意拓扑,支持最新的 IBIS/Spice/ TouchStone/IBIS-AMI 模型。

Sigrity SystemSI 可以对高速串行通道进行眼图和误码率分析,对系统中的任意参数进行扫描,得到最优化配置,并且集成了 PCI-E、SATA 等工业标准,直接对仿真结果进行判别。

Sigrity SystemSI 可以对整个 DDR 系统进行准确的 SSN 分析,集成 JEDEC 标准,自动为用户量测 SI 参数,并以此为基础,进行自动化时序分析。

面对 10Gbps 以上的高速通道传输的通讯信号,我们大多数会采用差分方式设计,这样可以持续更快速地传输大比特量数据。

Sigrity SystemSI 的高速串行和并行模块,可以适应高速信号传输通道的标准分析流程,支持 AMI 算法建模接口,能够更高效地创建发送端和接收端模型,同时内部的参数定义方式将芯片设计和业界高速传输标准(DDR/HDMI/USB/PCI-E等)以流程化的方式提供给用户,最终满足用户对系统总体 BER 的预测,并判断抖动、噪声是否都在指定的容限内,实现更简单易用的流程化操作。

Sigrity SystemSI

系统信号仿真亮点——

2#为GDDR6 接口增加基于 JEDEC 自动化分析功能

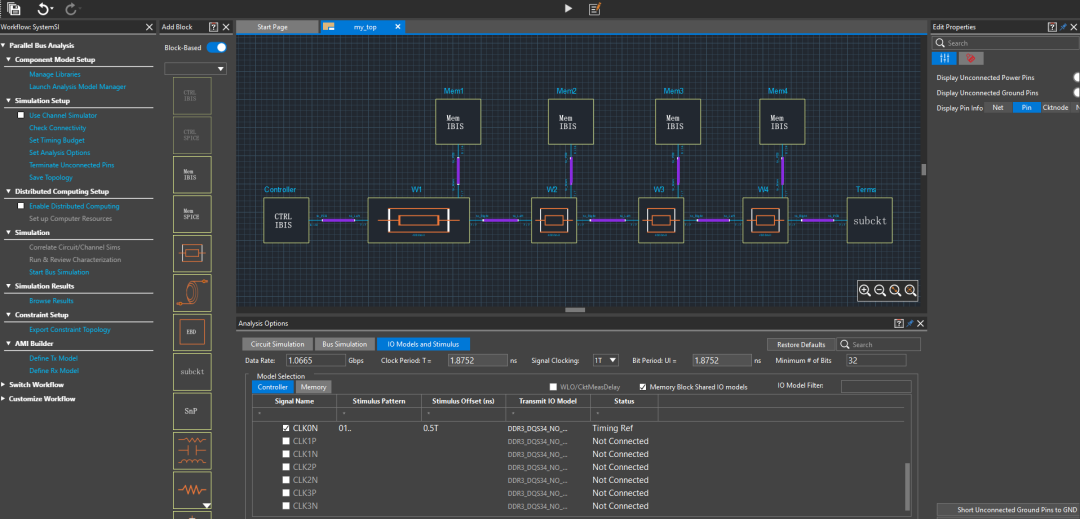

Wbench_SPB17.4_QIR4 更新之后,Sigrity SystemSI 可以支持为 GDDR6 接口增加基于 JEDEC 协议的自动化分析功能。接下来使用一个 DDR 的例子来说明 GDDR6 分析流程及内存块支持多个模型等功能。

实例讲解 · 图文版

1

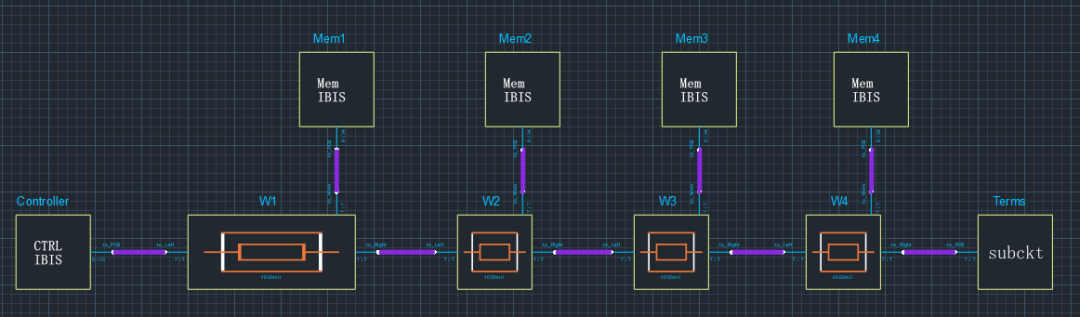

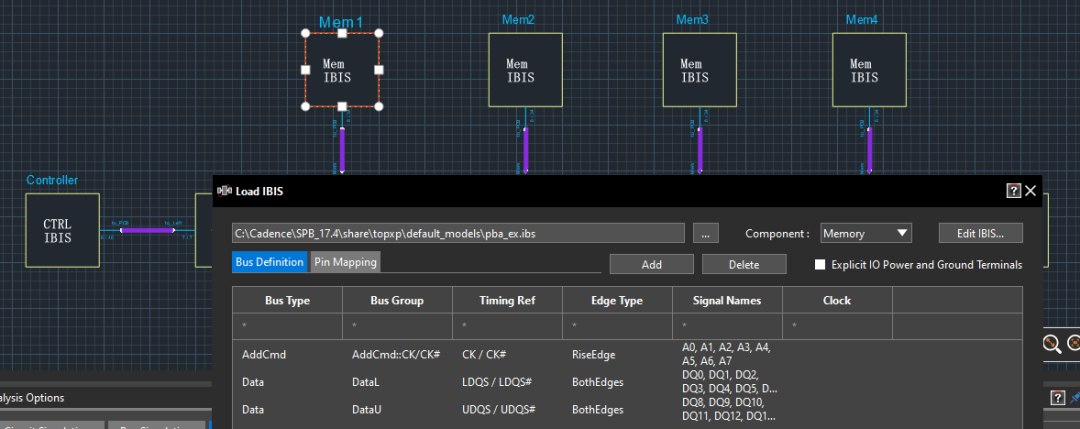

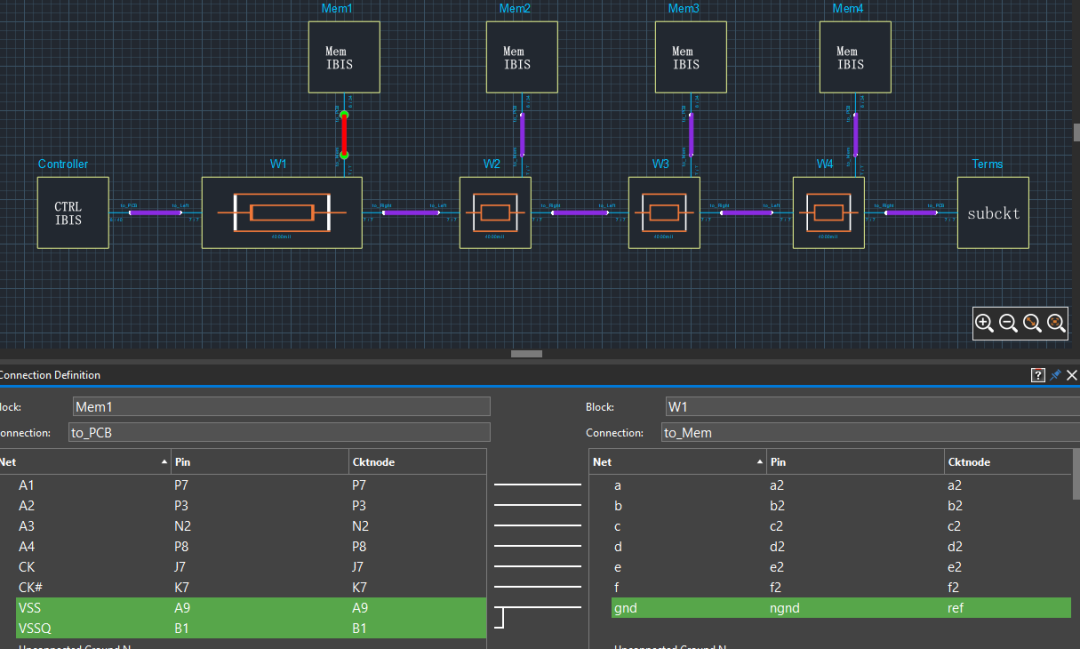

之前版本中拓扑的内存块仅支持分配相同的 IBIS 模型文件,现在的版本中不同位号的内存块可以分配给不同的 IBIS 型号,相当于不同的内存可以使用不同公司/厂商的 IBIS 模型文件。

2

拓扑中不同组的内存块可以分配不同的 IBIS 组件模型文件。

3

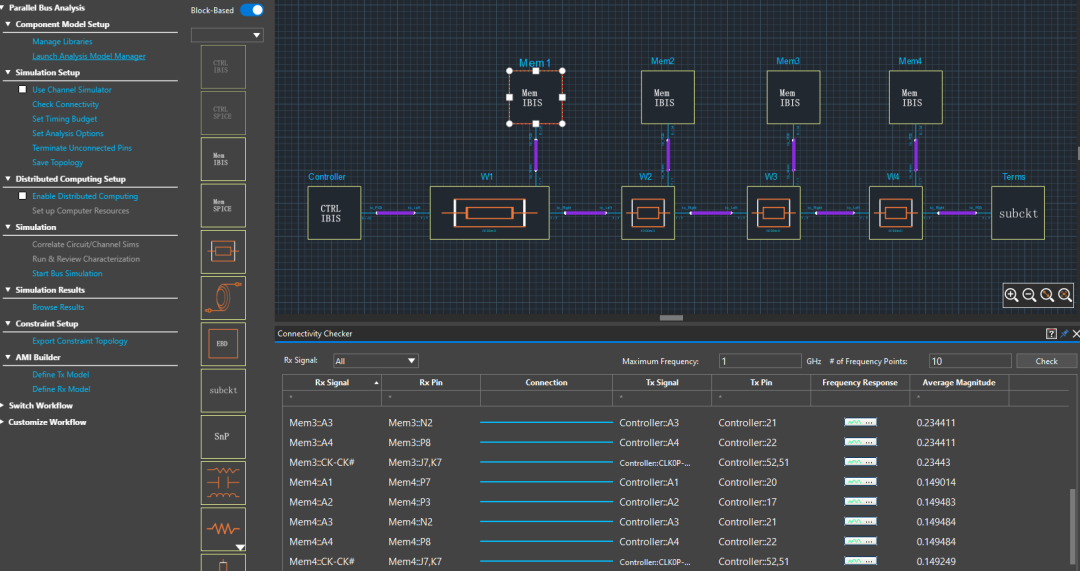

检查内存仿真模块之间的电气连接,检查互连信号发送接收的数据完整度。

4

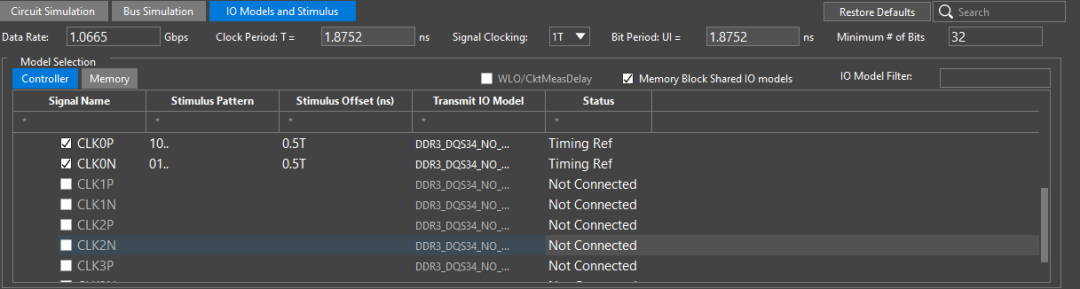

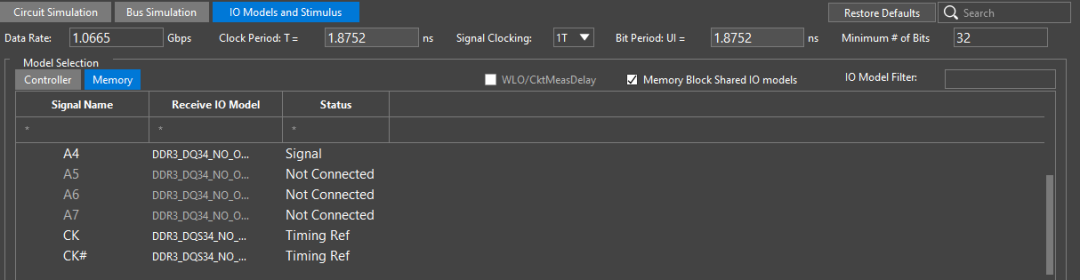

设置控制器模型参数、数据速率、信号周期以及发送和接收端的 IBIS 模型。

5

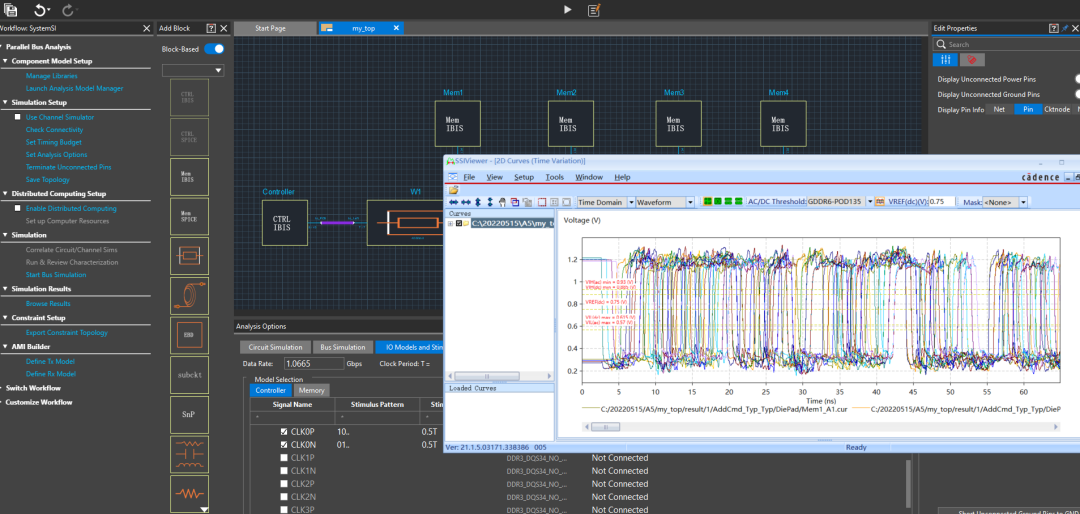

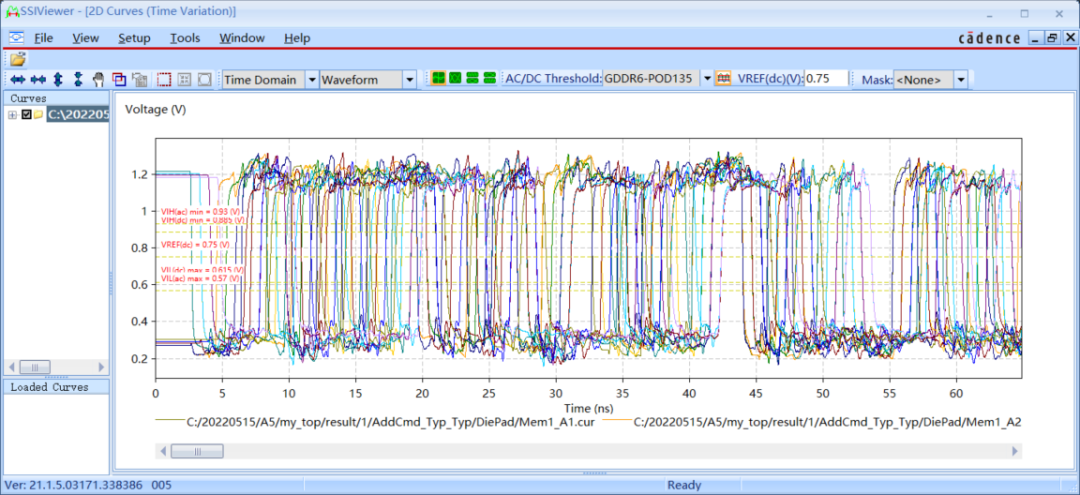

设置参数完成以后,执行仿真可以看到仿真完成后的结果波形数据。

6

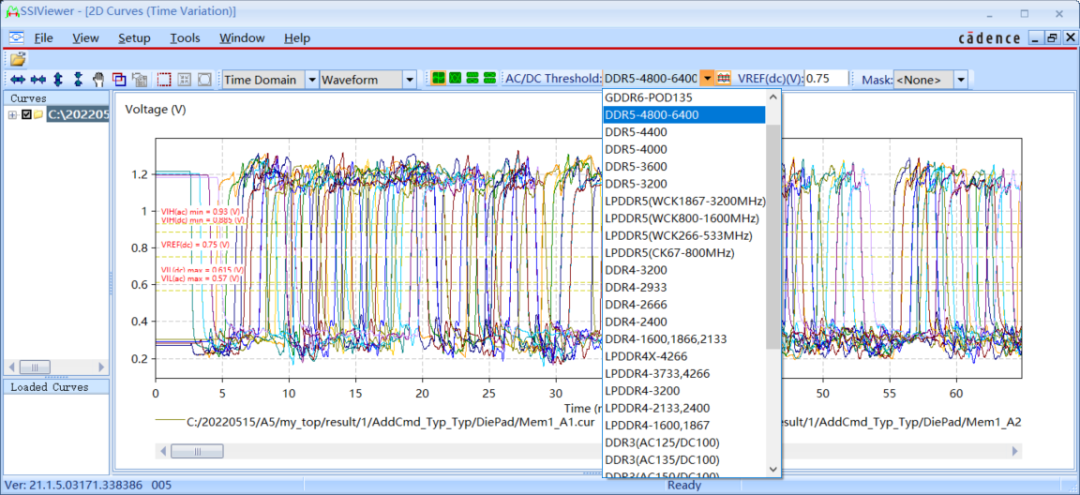

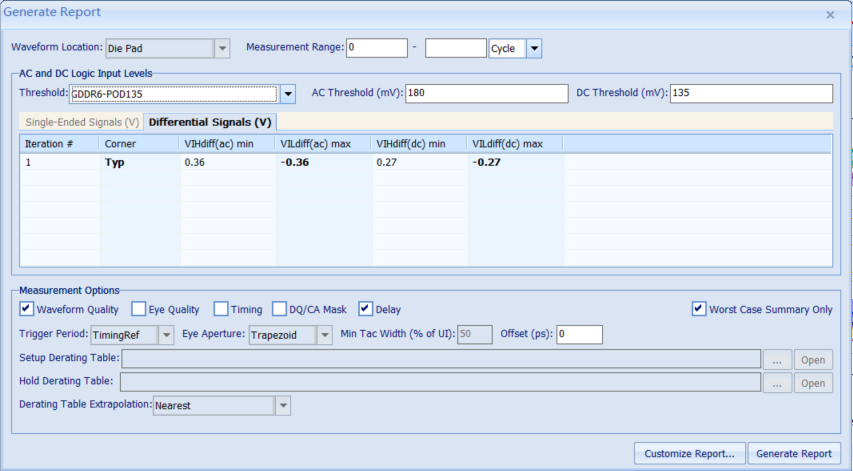

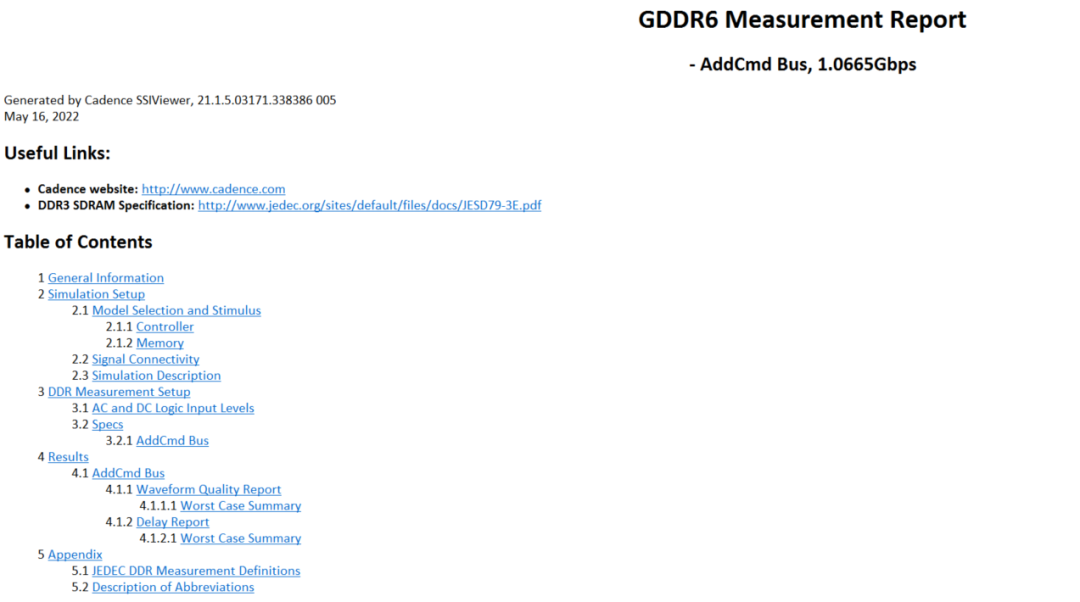

调用新增加的 GDDR6 接口模板分析波形数据。

7

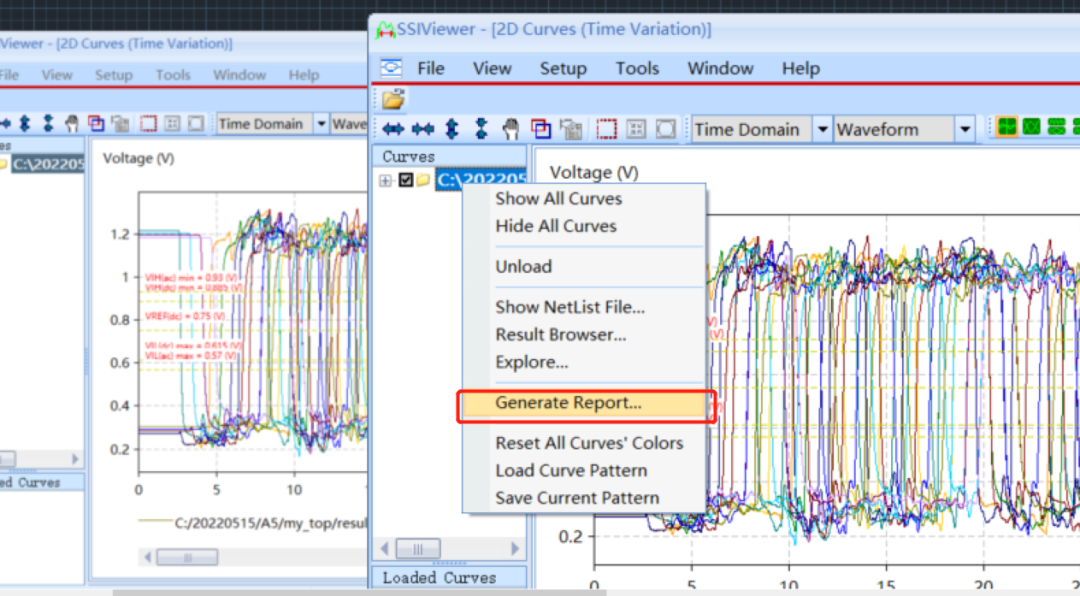

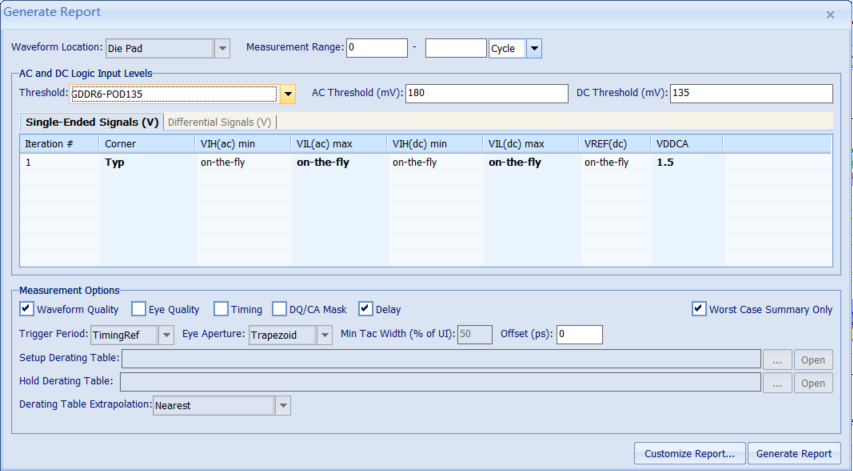

支持生成 GDDR6 基于 JEDEC 自动化分析功能的报告。

8

支持生成 GDDR6 基于JEDEC 自动化分析功能的报告。

9

支持生成 GDDR6 基于JEDEC 自动化分析功能的报告。

-

allegro

+关注

关注

42文章

657浏览量

145255

发布评论请先 登录

相关推荐

下一代高端显卡标配,容量和速度双翻倍的GDDR7登场!

实时网络的仿真和配置工具RTaW Pegase v4.6版本更新

RFID技术助力物流自动化分拣:提升速度、效率与准确性

Cadence Allegro 17.4PCB阻抗分析功能操作说

英伟达推出搭载GDDR6显存的GeForce RTX 4070显卡

Allegro X 23.11 版本更新 I PCB 设计:梯形布线的分析性能提升

Allegro X 23.11 版本更新 I PCB 设计:DFA_BOUND 用于 DFA 规则设定

美光出样业界容量密度最高新一代 GDDR7 显存

有办法自动为CYUSB4347-BZXC更新固件吗?

AMD RDNA4或采用GDDR6显存,Navi 4X或Navi 4C具备216个计算单元

Rambus推GDDR7内存控制器IP满足AI应用需求

英伟达、AMD新款显卡或仍配备2GB GDDR7显存

利用Sigrity Aurora进行PCB布线后的仿真分析-阻抗及寄生参数析

2022 Sigrity SPB 17.4 版本更新 I SystemSI 为GDDR6接口增加基于JEDEC自动化分析功能

2022 Sigrity SPB 17.4 版本更新 I SystemSI 为GDDR6接口增加基于JEDEC自动化分析功能

评论