今年三月,英特尔、AMD、Arm、两家领先的代工厂、Google Cloud、Meta、高通和 ASE 宣布,他们正在建立一种新的小芯片(chiplet)互联开放标准,名为通用小芯片互联技术(Universal Chiplet Interconnect Express,UCIe),旨在标准化小芯片的构建和相互通信方式。

过去几年的一大趋势是业内越来越多地使用多裸片先进封装,作为构建硅基系统的一种方式,通常称为系统级封装(Systems-in-Package,SiP)。目前,小芯片 (chiplet) 之间的通信没有什么重大的技术挑战,至少没有超出电路板上芯片通信的既有挑战。而在没有任何标准的情况下,所有 SiP 上的裸片都来自同一家公司(尽管通常是在多个半导体工艺节点上)。值得注意地, HBM 是一个例外(还有 HBM2 和 HBM3),JEDEC 参与了标准制定,Micron 等制造商提供了裸片堆栈,以便整合到基于高级封装的设计中。

Universal Chiplet Interconnect Express (UCIe) 标准

只有当标准得到普遍采用时,才能最大程度体现其价值。因此,对于建立小芯片互联开放标准,最重要的是哪些公司宣布加入其中。前文已经提到,最初的签署名单是:

英特尔、AMD、Arm、两家领先的代工厂、Google Cloud、Meta、高通和 ASE

在这些公司中,哪些公司实际上提供了符合标准的裸片,还有待观察。当然,Arm 不生产芯片,代工厂也不设计芯片;但也许有一天,将有可能制造一个搭载英特尔 x86 处理器、Google TPU 和高通 5G 调制解调器的 SiP,并且所有这些都整合在同一个封装中。

IP 公司没有受邀参加最初的官宣活动,可能是因为需要邀请的半导体和系统公司已经足够多。但我们将调整我们的 D2D(Die-to-Die)互连来遵循该标准——这样说应该并不唐突。

显然,UCIe 将效仿 PCIe(二者的名字都很相似)。PCIe 已经使大量供应商能够制造可以成功协同工作的电路板和芯片;同样,UCIe的目标则是使不同制造商的小芯片之间能够有类似水平的互操作性。至于什么样的商业环境能够促成这一目标,还有待观察。

至少,未来将应该有可能从多家公司购买裸片,并由这些公司制造裸片,然后当把这些裸片组装在一个先进多裸片封装时,它们可以顺利协同工作。进一步说,未来将可能有公司配备现成的裸片库存,从而消除等待生产这一过程。而更为理想的是,未来将可能有分销商(或新公司类型)拥有来自多个制造商的裸片库存,就像他们现在拥有封装好的元件一样。

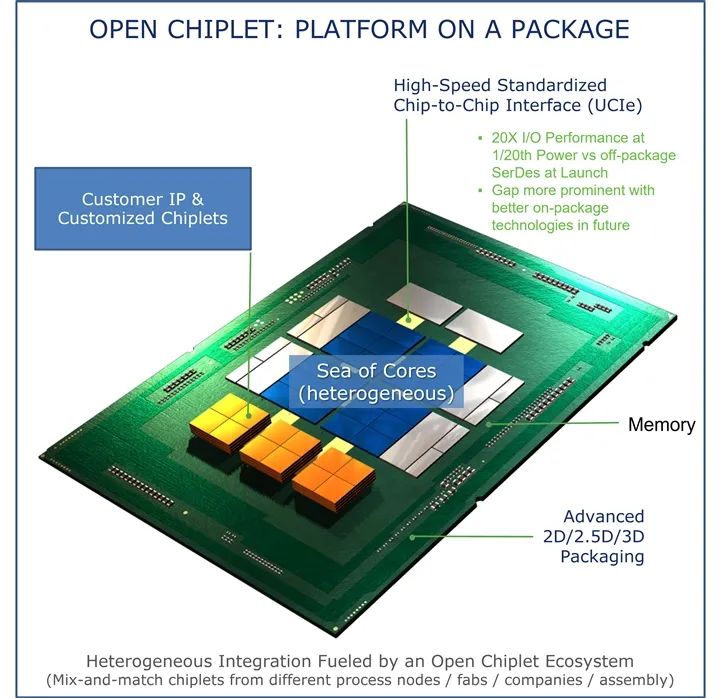

开发 D2D 互连的一个重要动机是,它比 PCB 上的芯片外连接具有更高的性能和更低的功耗。事实上,最初的产品发布承诺能够以 1/20 的功耗获得 20 倍的性能(见上图的新闻稿)。

与 PCIe(和 USB)一样,UCIe 标准最初的开发工作是由英特尔完成的,然后他们将该标准捐赠给后来成立的 UCIe 联盟。与其最为相似的的标准实际上是高级互连总线 (Advanced Interconnect Bus ,AIB),最初也是由英特尔开发而后捐赠给CHIPS 联盟;CHIPS 全称为“Common Hardware for Interfaces, Processors, and Systems(接口、处理器和系统的通用硬件)”,专注于开源的硬件和工具。

UCIe 显然不仅仅是英特尔的标准,这一点可以从最初通告的签署名单中看出。能让英特尔、AMD 和 Arm 联手合作,这件事必然意义重大。该规范包括物理层(电信号标准)和上面的协议层,并且详细说明了支持的 bump 间距,这间接指定了可以使用的先进封装技术。

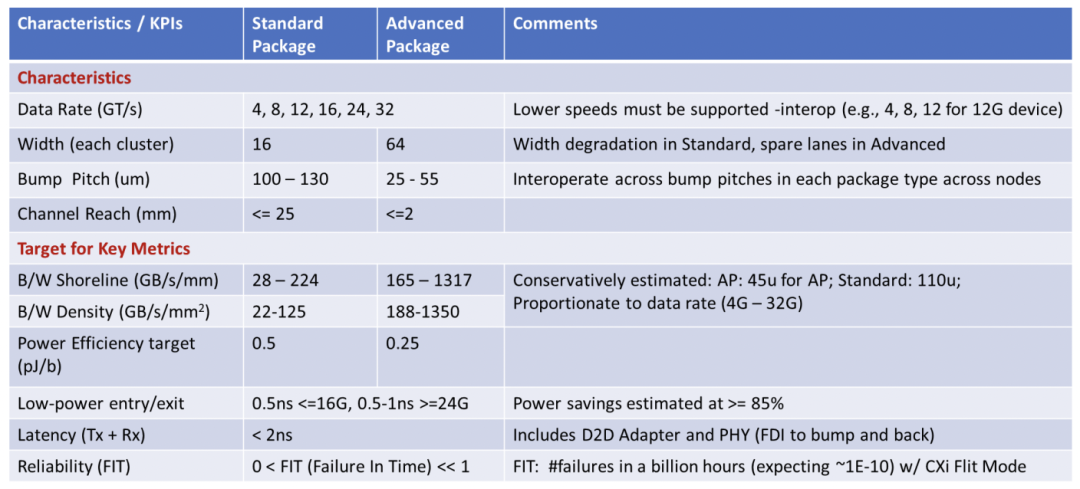

上表对初始标准中的数字进行了更深入的分析。

在白皮书《Universal Chiplet Interconnect Express (UCIe): Building an Open Chiplet Ecosystem(UCIe:构建开放的芯片生态系统)》中,有这样一段总结:

《UCIe:构建开放的芯片生态系统》

业界对一个开放的小芯片生态系统有巨大的需求,它将释放整个计算连续体的创新。UCIe 1.0 提供了极高的能效和极具性价比的性能。事实上,它是一个具有即插即用模式的开放标准,以多个成功的标准为蓝本,并由一群最合适不过的行业领导者推出,这将确保该标准被广泛采用。我们预计下一代创新将发生在小芯片层面,而使小芯片组合能够提供不同功能以供客户选择,将充分满足客户的应用要求。

-

芯片

+关注

关注

457文章

51350浏览量

428304

发布评论请先 登录

相关推荐

乾瞻科技宣布最新UCIe IP设计定案,推动高速传输技术突破

Alpahwave Semi推出全球首个64Gbps UCIe D2D互联IP子系统

MATLA B助力数字与模拟芯片设计:高效实现HLS、UCIe和UVM

新思科技发布40G UCIe IP,加速多芯片系统设计

新思科技发布全球领先的40G UCIe IP,助力多芯片系统设计全面提速

小鹏汽车自主研发的智能驾驶芯片已顺利完成流片阶段

一文了解CableLabs的领域与行业影响力

行业资讯 I 一文了解通用小芯片互联技术 (UCIe) 标准

行业资讯 I 一文了解通用小芯片互联技术 (UCIe) 标准

评论